Collection of memory configuration files for Xilinx Vivado along with example design for a few boards.

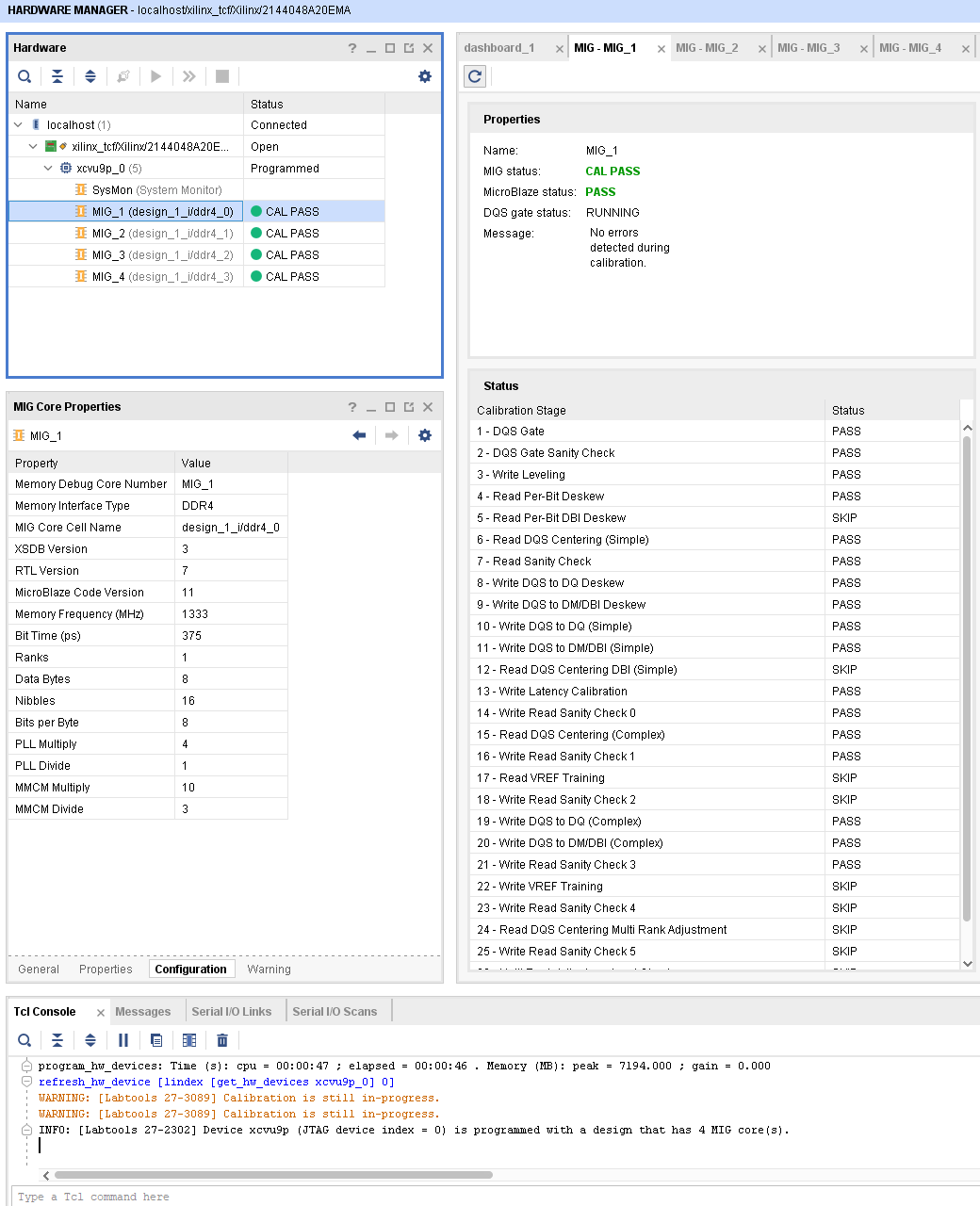

Tested with Vivado version 2019.2 & 2022.1

- UDIMM Crutial Ballistix Sport BLS4G4D240FSB (CT40A512M8RH-075E component) - 4GB

- UDIMM Crutial Ballistix Sport BLS8G4D240FSB (CT40A512M8RH-075E component) - 8GB

- UDIMM Crutial Ballistix Sport BLS16G4D26BFSB (CT40A1G8WE-75H:D component) - 16GB

- SODIMM Crutial Ballistix Sport BLS4G4S26BFSD (CT40A512M8WE-75H component) - 4GB

- SODIMM Micron MTA8ATF1G64HZ (MT40A1G8WE-075E component) - 8GB

- Bittware CVP13

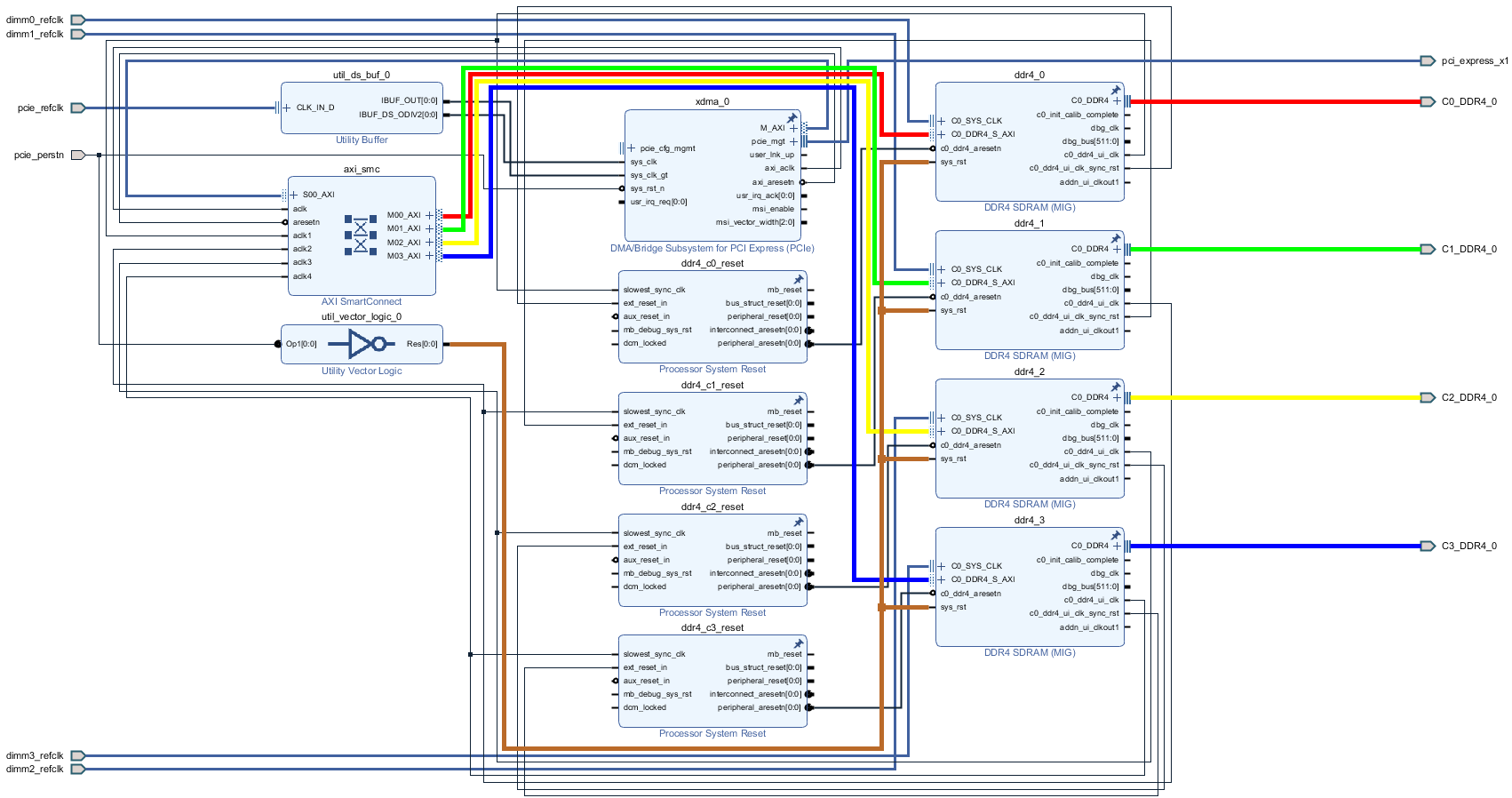

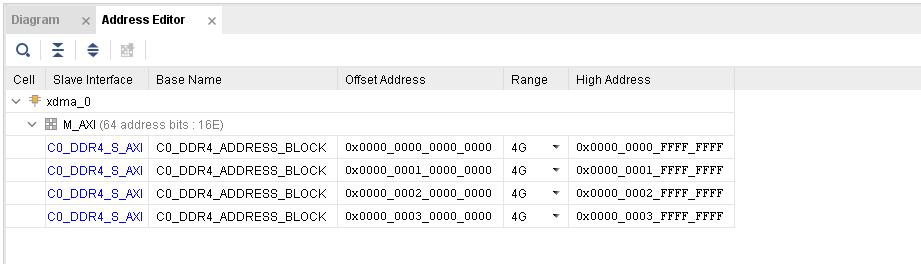

- Xilinx BCU1525

- Xilinx VCU1525

- Xilinx ZCU104

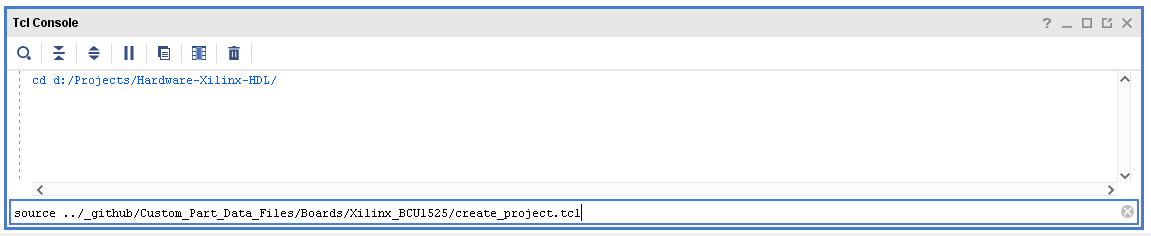

Clone repo, go to your project directory and source TCL script from Vivado. For example:

cd ~

git clone https://github.com/D953i/Custom_Part_Data_Files.git

In Vivado TCL console:

source ../_github/Custom_Part_Data_Files/Boards/Xilinx_BCU1525/create_project.tcl