- Autor: Gonzalo G. Fernandez

- Carrera de Especializacion en Sistemas Embebidos

- Laboratorio de Sistemas Embebidos - FIUBA

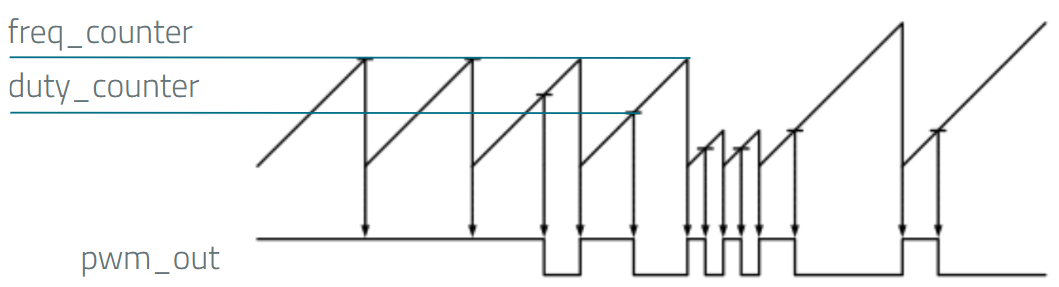

El comportamiento se basa en el siguiente diagrama de tiempo:

La salida queda definida por:

- freq_counte: define la frecuencia del canal PWM

- duty_counter: define el duty cycle del canal PWM

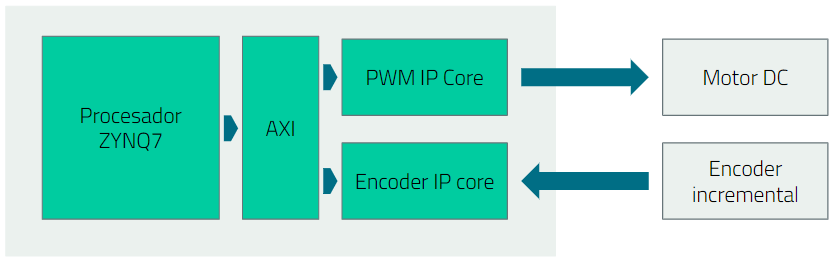

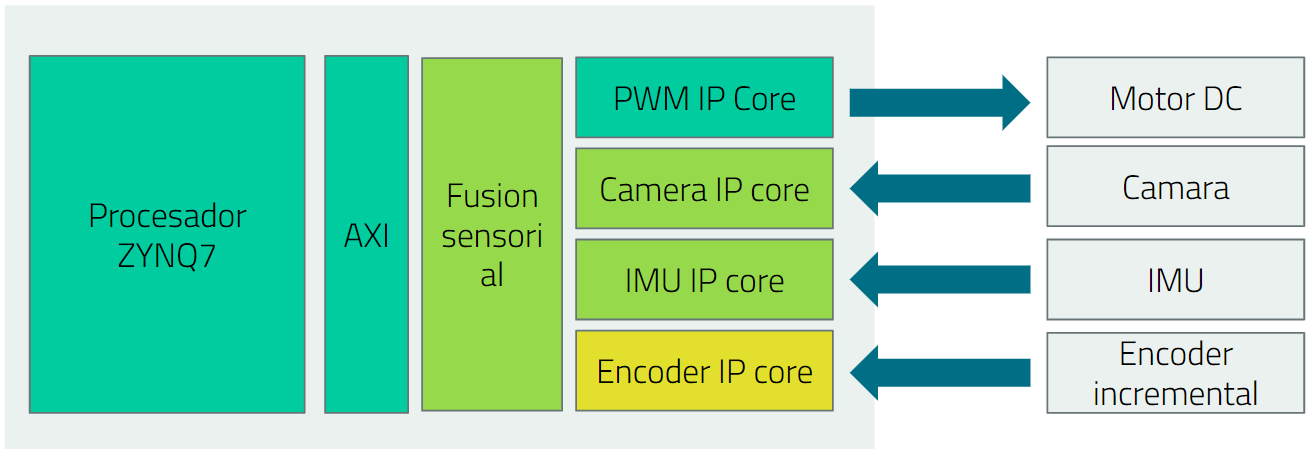

El diagrama de bloques del modulo diseñado es el siguiente:

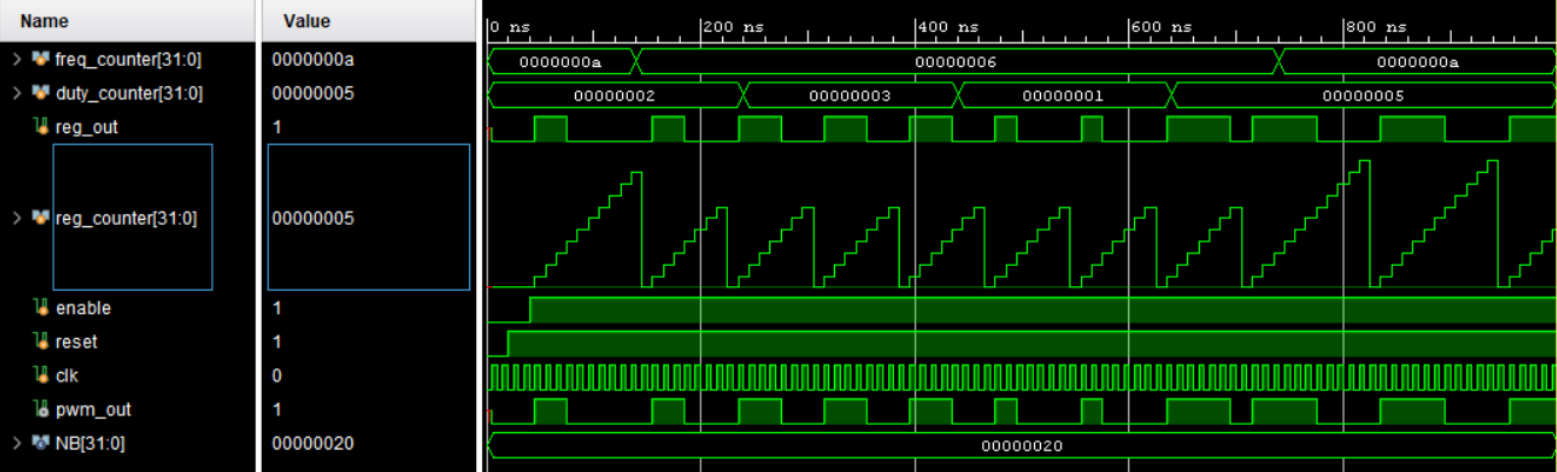

Simulacion comportamental:

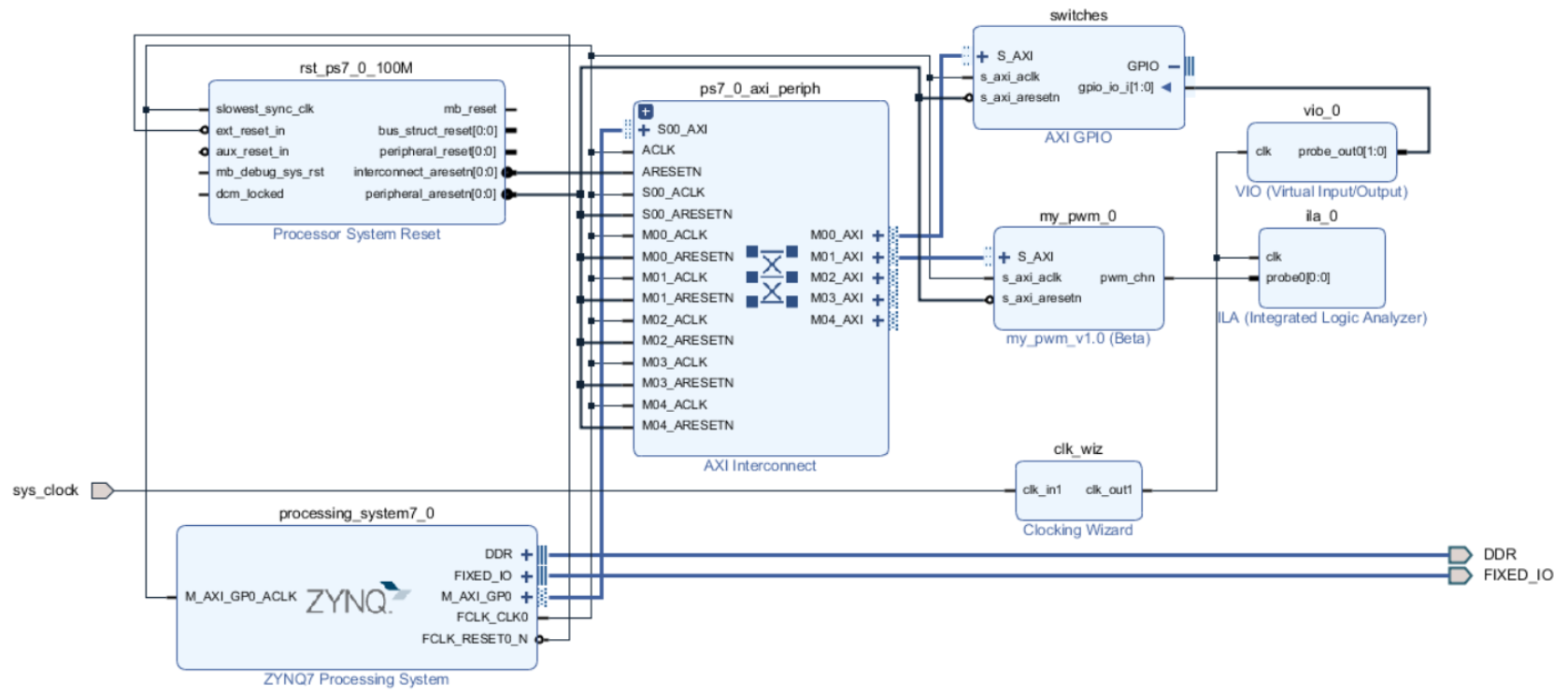

Project block design (PWM y switches):

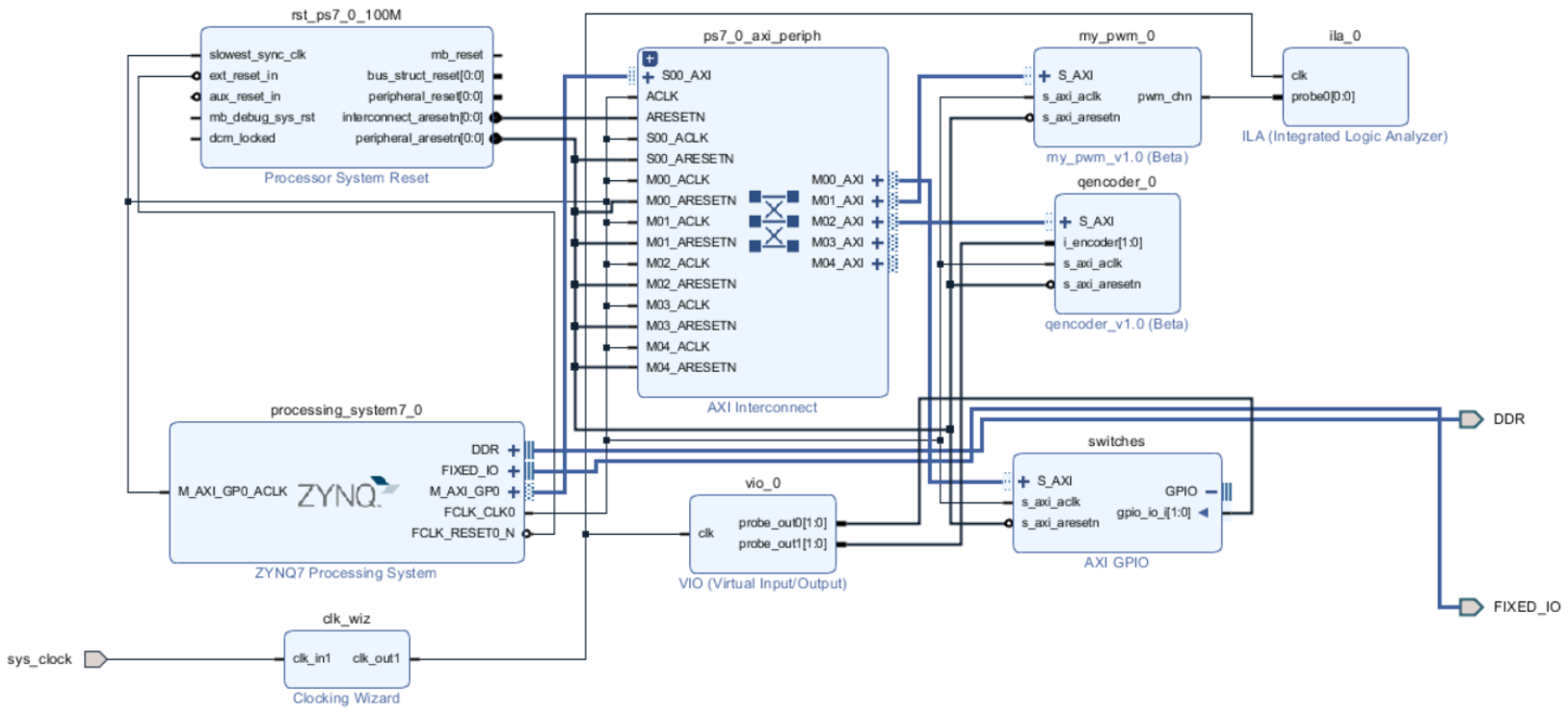

Project block design (PWM, encoder y switches):

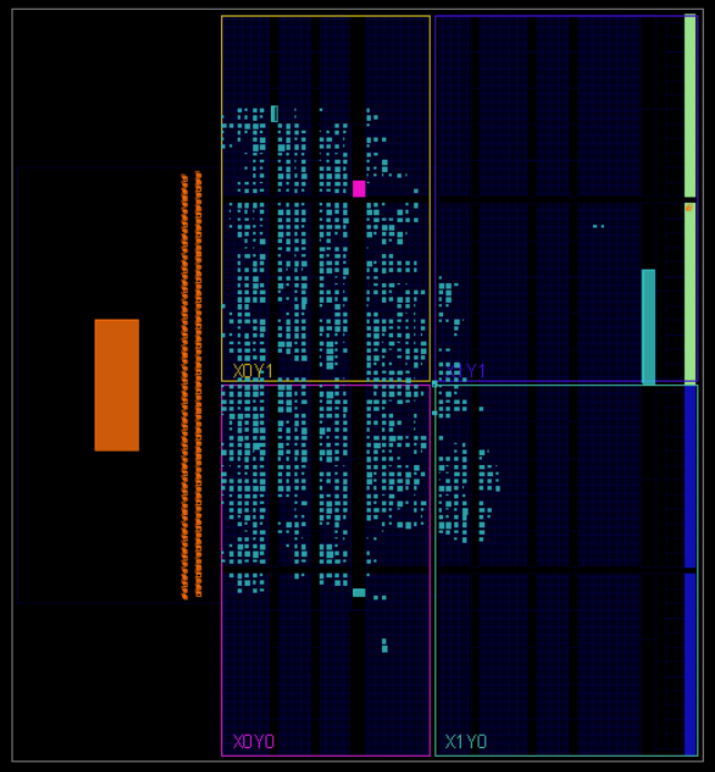

Timing report:

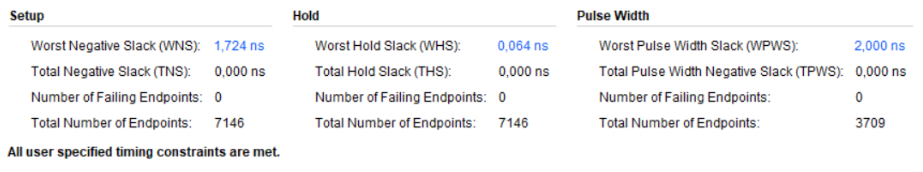

Utilization report:

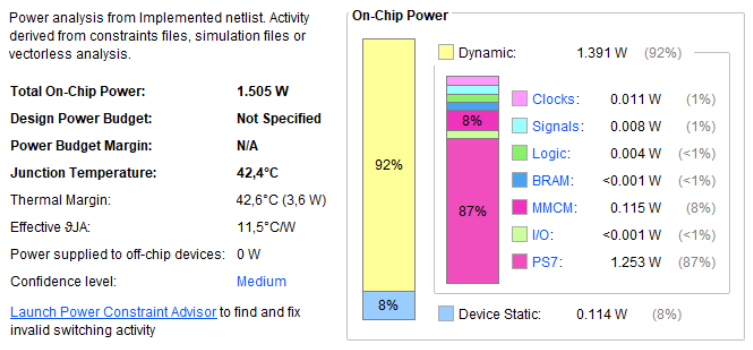

Power report: