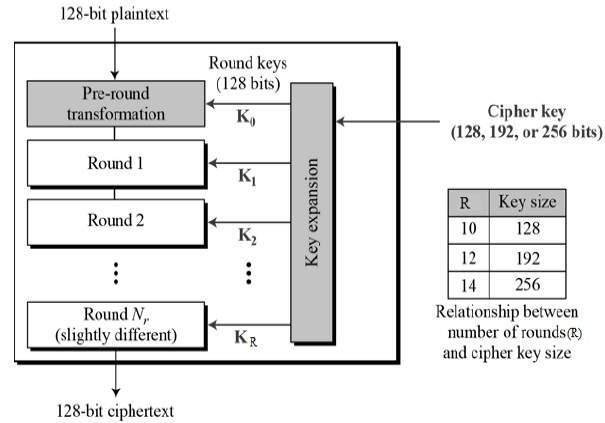

The Advanced Encryption Standard (AES) is a symmetric block cipher to encrypt sensitive data. This implementation supports a 128-bit key. AES-128 bit requires 10 rounds to complete the full operation. The input data is 128 bits and the input key is also 128-bit and each round requires 1 cycle to complete.

-

Add round key

-

Substitute bytes

-

Shift rows

-

Mix columns

-

Icarus-Verilog can be installed via Homebrew :

$ brew install icarus-verilog -

Download Scansion from here.

-

Clone the repository.

-

Run

$ makeand type MIPS code to see it in binary form in rams_init_file.hex file. -

$ make simulatewill:

- compile design+TB

- simulate the verilog design

$ make displaywill:

- display waveforms.