This is our group project for ENSC 452 - Advanced Digital System Design. We decided to do audio processing in the form of a DJ board.

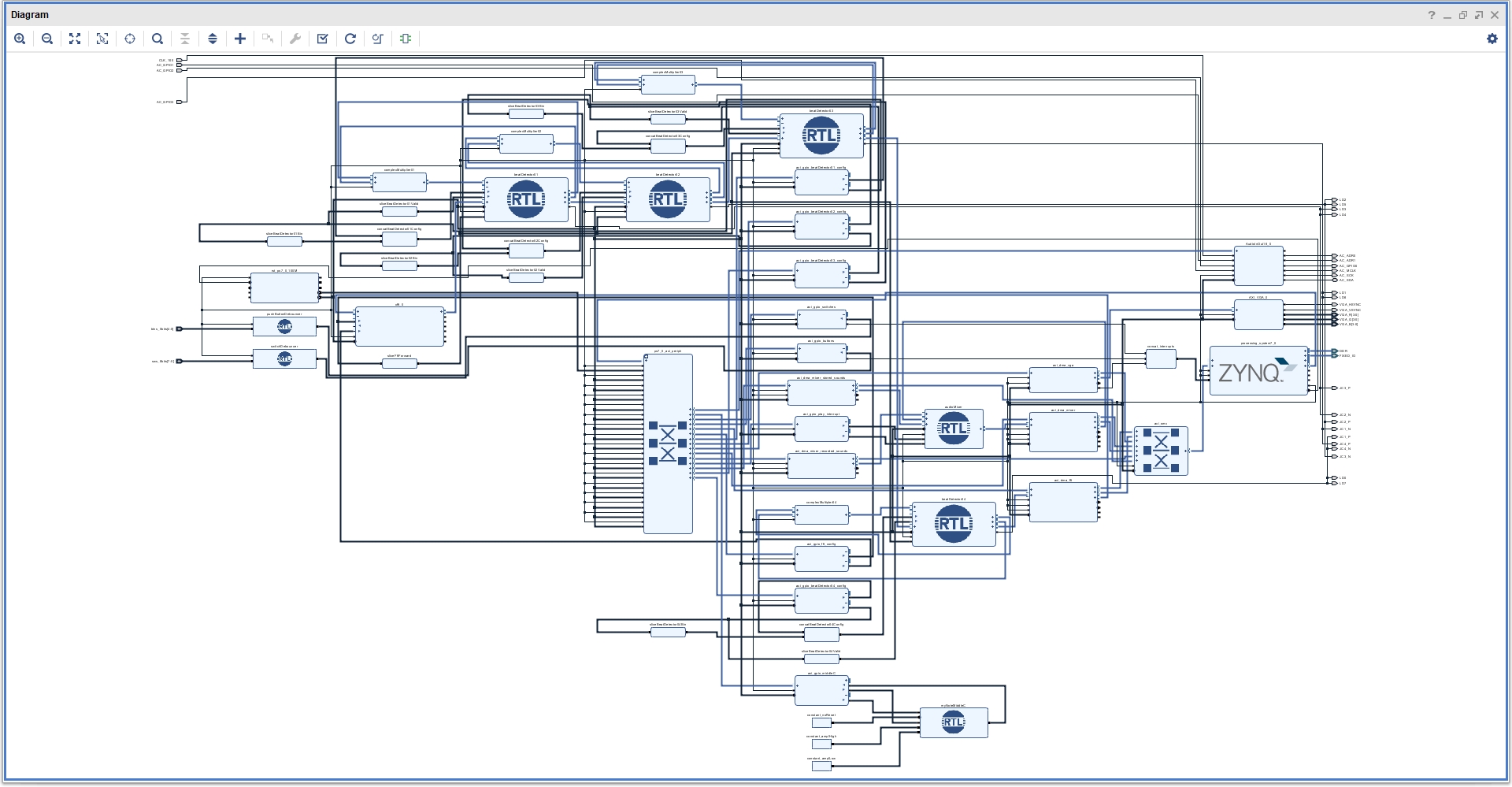

- AXI-Stream FFT (512 point)

- AXI GPIO

- AXI DMA

- AXI Audio Controller

- AXI-Stream VGA Core (see acknowledgements)

- Beat Detector (Custom)

- Audio Mixer (Custom)

- Play stored sounds (Airhorn and DJ Khaled's Another One)

- Equalizer effects for high, mid, and low frequencies.

- Echo effect.

- Record and playback Line In audio.

- Loopback recorded audio.

- ZedBoard

- Vivado 2017.3

- Vivado 2017.3 Tcl Shell

- Xilinx SDK

- Open Vivado.

- Run

build.tcl. This will generate the block diagram. - Click

Generate Bitstream. This will take a while, so grab yourself a coffee and get comfortable! - Export the hardware.

- Launch the SDK with default settings.

- Import projects from

./sdk. Do not select the*_bspandaudioTest_wrapper_*projects. - Create a board support package (BSP) with the name

audioTest_bspand the following setting:

Uncheck Use default location.

Location: (browse tosdkfolder)

CPU: ps7_cortexa9_0. - Create a board support package (BSP) with the name

vga_bspand the following setting:

Uncheck Use default location.

Location: (browse tosdkfolder)

CPU: ps7_cortexa9_1. - Build the project.

- Program the FPGA with the bitstream that you exported.

Make two debug configurations with the following names:

- Run Me First!

In theTarget Setuptab:

Debug Type: Standalone Application Debug.

Uncheck Program FPGA.

Check Run ps7_post_config.

In theApplicationtab:

Core 0: audioTest/audioTest.elf

Core 1: (none) - Run Me Second!

In theTarget Setuptab:

Debug Type: Standalone Application Debug.

Uncheck Program FPGA.

Check Run ps7_post_config.

In theApplicationtab:

Core 0: audioTest/audioTest.elf

Core 1: vga/vga.elf

- Ensure that Skip All Breakpoints is deselected.

- Debug

Run Me First!, and click Continue when loaded. - Debug

Run Me Second!. If a prompt pops up regardingRun Me First!, click Yes to terminate it and continue.

- Open the Vivado 2017.3 Tcl Shell.

- In

./ddr, modify the TCL script to point to the absolute path of theddrfolder. - Copy and paste the script into the shell.

- Verify that the shell has loaded all files onto the board.

- In the SDK, click Continue on core 0 (important!).

- Click Continue on core 1.

- Plug in your audio source into Line In.

- Plug in your headphones/speakers into Headphone Out.

- Go and have fun!

- In the SDK, click File > New > Application Project.

- Choose any name for your application project.

- For the Hardware Platform, choose audioTest_wrapper_*, and click Next.

- Select Zynq FSBL, and click Finish. This is your bootloader.

- Build all projects.

- Click Xilinx > Create Boot Image.

- Specify an output path with the filename as

BOOT.bin - Add the following files in order:

- bootloader

.elfwith Partition Typebootloader. - bitstream

.bitwith Partition Typedata. - audioTest

.elfwith Partition Typedata. - anotherOne

.binwith Partition Typedataand with Load set to the address inluiMemoryLocations.h. - airhorn

.binwith Partition Typedataand with Load set to the address inluiMemoryLocations.h.

- bootloader

- Click Create Image.

- Copy

BOOT.binto the root of a FAT32 formatted SD card, and insert it into the ZedBoard. - Set the boot mode of the ZedBoard to SD Card by shorting jumpers MIO4 and MIO5.

- Turn it on, and have fun!

- Switch 0: Adjust low frequencies (Down - off, Up - on)

- Switch 1: Adjust mid frequencies (Down - off, Up - on)

- Switch 2: Adjust high frequencies (Down - off, Up - on)

- Switch 3: Enable pitch adjustment with push buttons (not working) (Down - off, Up - on)

- Switch 4: Enable echo adjustment with push buttons (Down - off, Up - on).

- PL Push Button Up: Amplify the enabled effects from switch 3 and 4.

- PL Push Button Centre: Reset the enabled effects from switch 3 and 4 to their default (off) values.

- PL Push Button Down: Lower the enabled effects from switch 3 and 4.

The following two push buttons depend on the settings on switches 7 to 5.

- PS Push Button Right: Playback sound to Headphone Out.

- PS Push Button Left: Record sound from Line In.

| Setting | Switch 7 | Switch 6 | Switch 5 |

|---|---|---|---|

| Use/record recorded sound 1 (no loopback) | Down | Down | Down |

| Use/record recorded sound 1 (loopback) | Up | Down | Down |

| Use/record recorded sound 2 (no loopback) | Down | Up | Up |

| Use/record recorded sound 2 (loopback) | Up | Up | Up |

| Use stored sound 1 (Another One) | Down | Up | Down |

| Use stored sound 1 (Airhorn) | Down | Down | Up |

- Kind thanks to our classmates Maggie Parkhurst and Steven Lippmann for lending us their VGA core.

- AXI-Lite Slave from Laxer3a

- Circular buffer for echo effect from EmbeddedArtistry