Github: https://github.com/ultraembedded/riscv_sbc

This repo contains a working RISC-V based Single Board Computer project based around the LambaConcept USB2Sniffer FPGA board.

The board is available for purchase on the LambdaConcept shop;

https://shop.lambdaconcept.com/home/35-usb2-sniffer.html

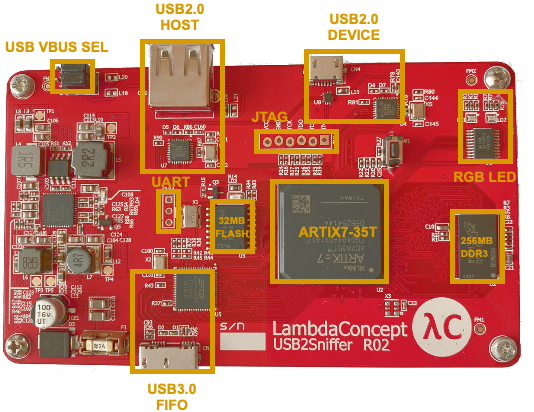

The USB2Sniffer is designed to be used as a USB 2.0 capture device, or as a development board for USB 2.0 IP designs.

It has plenty of fast DDR3 RAM and SPI-Flash, as well as USB 2.0 (Host + Device) and USB 3.0 (high speed FIFO) interfaces.

It can be repurposed as a single board computer (SBC) for running RISC-V Linux with both USB 2.0 host and USB 2.0 device support!

- XC7A35T Artix 7 Series FPGA xc7a35t-fgg484-1

- 256MB DDR3 Micron MT41K256M16TW-107

- 32MB SPI Flash Micron MT25QL256ABA

- USB3.0 to FIFO Bridge (up to 400MB/s of bandwidth to the FPGA) FTDI FT601

- 2 x High Speed USB2.0 ULPI PHY Microchip USB3300

- 3 RGB LEDs, 2 x GPIO pins

To clone this project and its dependencies;

git clone --recursive https://github.com/ultraembedded/riscv_sbc.git

Most of the IP cores used in this project are designed by myself and available as easy to follow open-source Verilog modules. The remainder (DDR3, CDC, PLL) are IP cores built with Xilinx Vivado.

| Name | Description | Provider |

|---|---|---|

| riscv_top | 32-bit RISC-V CPU or Dual Issue RV32 | - |

| usb_host | Basic USB Host | - |

| ulpi_wrapper | ULPI PHY Interface | - |

| core_soc | Peripherals - UART, SPI, GPIO | - |

| dbg_bridge | UART to AXI bus master | - |

| spiflash | SPI-Flash XIP | - |

| usb_serial | USB Device UART | - |

| mig_axis.xci | MIG DDR3 Controller | Xilinx |

| axi_cdc_buffer.xci | AXI4 Clock Domain Converter | Xilinx |

| axilite_cdc_buffer.xci | AXI4-Lite Clock Domain Converter | Xilinx |

- DDR3, SPI-Flash, ULPI interfaces now working.

- RISC-V CPU booting Linux RV32 5.0 kernel to BusyBox userspace.

- Option of USB Serial port implemented in the FPGA fabric for Linux console access (connected via USB micro port).

- Option of Linux console / debug output via UART connector (@ 1M baud).

- USB Host port working under Linux (mounting USB storage devices).

- Initial Verilog source released.

- Prebuilt bitstream added to 'bitstreams' folder.

- More instructions to come...

A prebuilt FPGA bitstream and series of bootloaders are provided in the bitstreams directory.

These can be flashed onto the board with a Vivado supported programmer using the provided makefile / Vivado TCL;

# Make sure vivado tools are available in the shell path....

# Create a MCS file containing the bitstream and various bootloaders

# This creates riscv_sbc.mcs

cd bitstreams

make create_mcs

# Program riscv_sbc.mcs onto the onboard SPI-Flash

make program_flash

The SPI-Flash device is expected to contain the following files;

| Offset | File | Description |

|---|---|---|

| 0x00000000 | fpga.bit | FPGA bitstream. |

| 0x00300000 | primary_boot.bin | Bootloader copies Flash 0x00400000 - 0x0040FFFF to 0x80000000 and jumps to it. |

| 0x00400000 | secondary_boot.bin | Bootloader for Linux. Copies Kernel from FLASH to RAM. |

| 0x00500000 | config.dtb | Linux Device Tree Blob (output from dtc). |

| 0x00600000 | vmlinux.bin | Linux Kernel binary. |