This Verilog implementation is a replica of the classical AY-3-8913 programmable sound generator. With roughly a 1600 logic gates this design fits on a single tile of the TinyTapeout.

The main goals of this project are:

- closely replicate the behavior and eventually the complete design of the original AY-3-891x with builtin DACs

- provide a readable and well documented code for educational and hardware preservation purposes

- leverage the modern fabrication process

A significant effort was put into a thorough test suite for regression testing and validation against the original chip behavior.

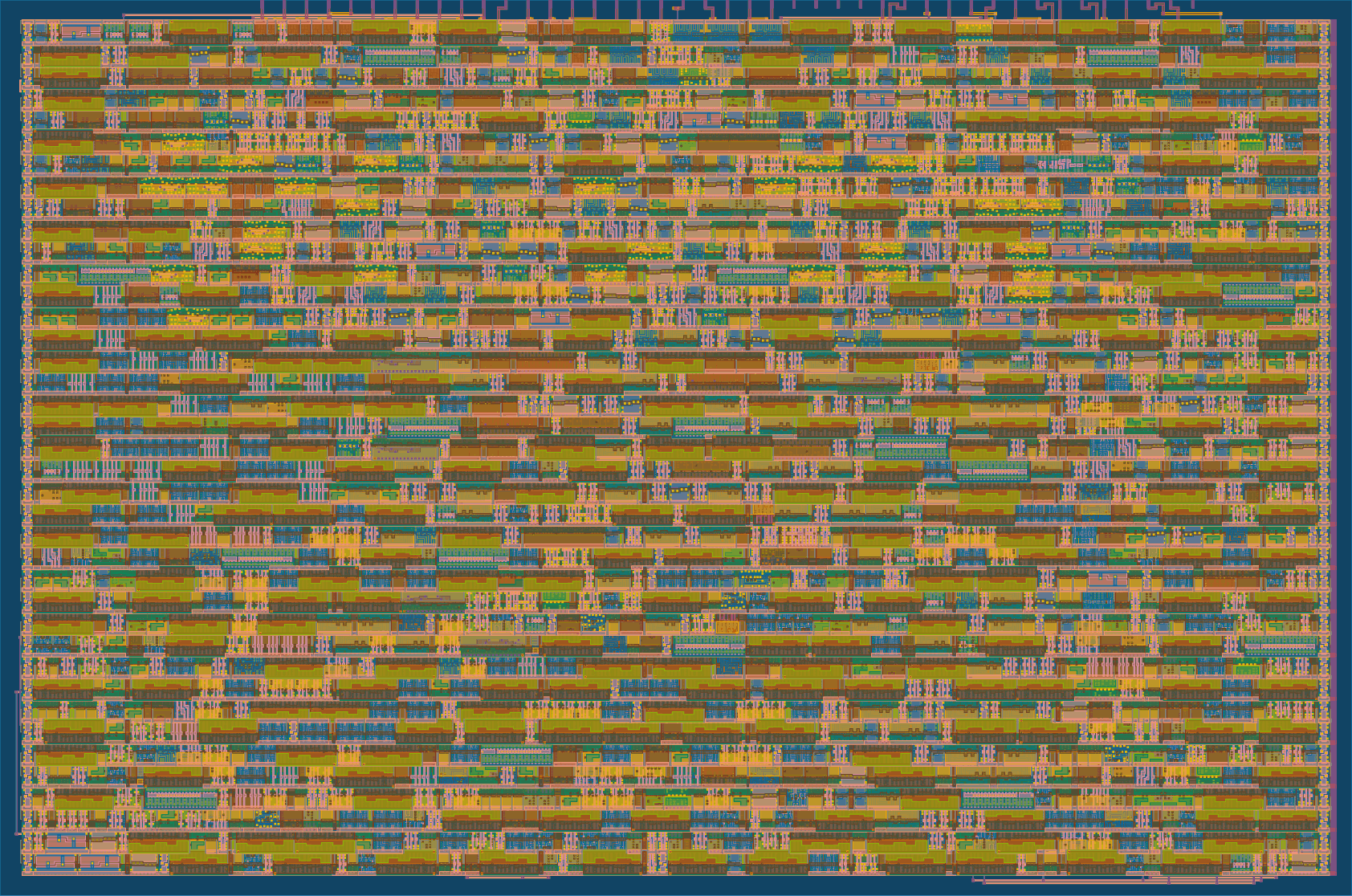

The ASIC for the AY-3-8913 replica is built using the open source Skywater 130nm PDK and is part of multi project TinyTapeout.

Using 130nm process this AY-3-8913 fits in 160x100 um. The design consist of roughly 1600 digital logic gates and of which 223 are data flip-flops storing 1 bit of data each. Logic takes 87% of the chip area. Total wire length is 30 mm!

Examine the layout of this chip in 3D!

- 3 square wave tone generators

- 1 noise generator

- 1 envelope generator with 10 patterns

- Capable to produce a range of waves typically from 122 Hz to 125 kHz, defined by 12-bit registers.

- 16 different volume levels

The AY-3-891x family of programmable sound generators was introduced by General Instrument in 1978. Variants of the AY-3-891x were broadly used:

- home computers: Amstrad CPC, Atari ST, Oric-1, Sharp X1, MSX, ZX Spectrum 128/+2/+3

- game consoles: Intellivision, Vectrex

- and arcade machines

The AY-3-891x chip family competed with the similar Texas Instruments SN76489.

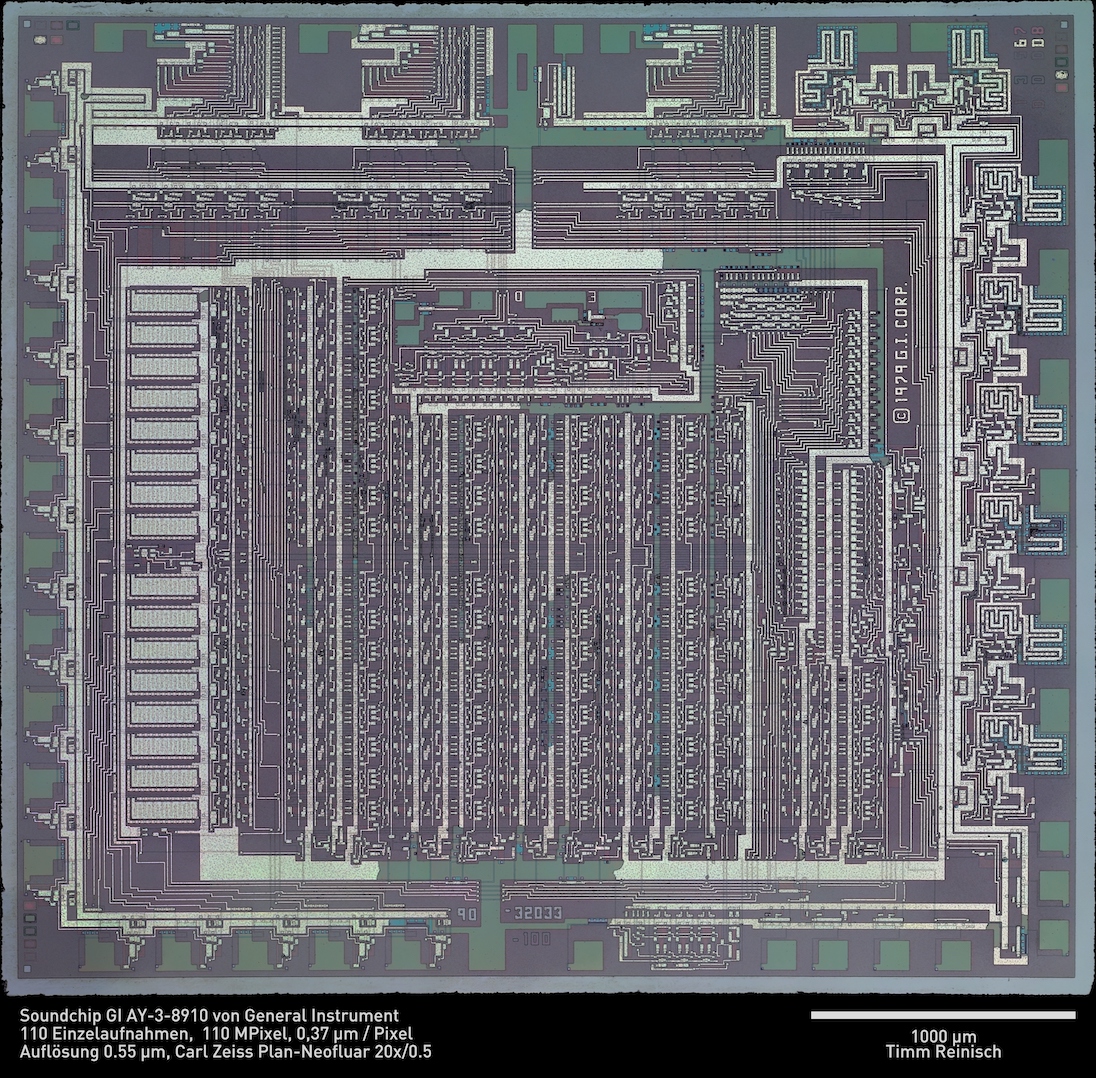

This implementation would not be possible without the reverse engineered schematics and analysis done by lvd and based on decapped AY-3-8910 and AY-3-8914 chips!

- https://en.wikipedia.org/wiki/General_Instrument_AY-3-8910

- https://www.vgmpf.com/Wiki/index.php/AY-3-8910

- https://github.com/lvd2/ay-3-8910_reverse_engineered/blob/master/pdf/generalinstrument_ay-3-8910.pdf

- https://github.com/simondotm/ym2149f/blob/master/doc/Resources.md

- https://www.polynominal.com/atari-st/atari-st-ym2149f-yamaha.html

- https://www.atari-shrine.co.uk/hardware/articles/Yamaha%20YM2149.html

- http://wiki.intellivision.us/index.php?title=PSG

- https://www.atarimagazines.com/v4n7/stsound.html

- http://clarets.org/steve/projects/2021_ym2149_sync_square.html

- YMZ294, YMZ284, YMZ285

- AY-3-8910, AY-3-8912, AY-3-8930

- YM2149

- YM3439

- T7766A

- WF19054, JFC 95101 and KC89C72

- https://maidavale.org/blog/ay-ym-differences/

- Atari ST, Intellivsion, Amstrad CPC, Oric-1, Colour Genie, MSX, ZX Spectrum 128

- https://github.com/lvd2/ay-3-8910_reverse_engineered

- http://privatfrickler.de/blick-auf-den-chip-soundchip-general-instruments-ay-3-8910/

- https://siliconpr0n.org/map/gi/ay-3-8910/

- https://siliconpr0n.org/map/gi/ay-3-8914

- AY-3-8910 die size: 4.16 mm x 3.80 mm

There are several ways to connect this chip to the microcontroller and speaker.

One option is to connect off the shelf data parallel Digital to Analog Converter (DAC) for example Digilent R2R Pmod to the output pins and route the resulting analog audio to piezo speaker or amplifier.

Another option is to use the Pulse Width Modulated (PWM) AUDIO OUT pin with OpAmp+capacitor based integrator or capacitor based low-pass filter and a speaker:

uController AY-3-8913

,---------. ,---._.---.

| | 2 Mhz ->|CLK SEL0|<-- 0

| GPIOx|----------->|BC1 SEL1|<-- 0

| GPIOx|----------->|BDIR |

| GPIOx|----------->|D0 |

| GPIOx|----------->|D1 |

| GPIOx|----------->|D2 | C1

| GPIOx|----------->|D3 | ,----||----.

| GPIOx|----------->|D4 | | |

| GPIOx|----------->|D5 | | OpAmp | Speaker

| GPIOx|----------->|D6 AUDIO| | |\ | /|

| GPIOx|----------->|D7 OUT |-----.---|-\ | C2 .--/ |

`---------' `---------' | }---.---||---| |

,--|+/ `--\ |

| |/ | \|

| |

GND --- GND ---

| SEL1 | SEL0 | Description | Clock frequency |

|---|---|---|---|

| 0 | 0 | Standard mode, clock divided by 8 | 1.7 .. 2.0 MHz |

| 1 | 1 | -----//----- | 1.7 .. 2.0 MHz |

| 0 | 1 | New mode for TT05, no clock divider | 250 .. 500 kHZ |

| 1 | 0 | New mode for TT05, clock div. 128 | 25 .. 50 MHz |

- https://github.com/jotego/jt49 (Verilog)

- https://github.com/dnotq/ym2149_audio/ (VHDL)

- https://opencores.org/projects/sqmusic

- https://github.com/mamedev/mame/blob/master/src/devices/sound/ay8910.cpp

- https://github.com/arnaud-carre/sndh-player/blob/main/AtariAudio/ym2149c.cpp

- https://github.com/mengstr/Discrete-AY-3-8910 - using only discreet 74-series logic ICs!

- http://antarctica.no/stuff/atari/YM2/Misc.Games/ Music from several Atari ST games in YM format

- https://www.cpc-power.com/index.php?page=database Music from many Amstract CPC games in YM format

- https://vgmrips.net/packs/system/atari/st Music from AtariST games in VGM format

- https://vgmrips.net/packs/system/sinclair/zx-spectrum-128 Music from ZX Spectrum 128 games in VGM format

- https://vgmrips.net/packs/system/ascii/msx Music from MSX games in VGM format

TinyTapeout is an educational project that aims to make it easier and cheaper than ever to get your digital designs manufactured on a real chip.

To learn more and get started, visit https://tinytapeout.com.

Edit the info.yaml and uncomment the source_files and top_module properties, and change the value of language to "Verilog". Add your Verilog files to the src folder, and list them in the source_files property.

The GitHub action will automatically build the ASIC files using OpenLane.

Please see the instructions for:

- Submit your design to the next shuttle on the website. The closing date is November 4th.

- Edit this README and explain your design, how it works, and how to test it.

- Share your GDS on your social network of choice, tagging it #tinytapeout and linking Matt's profile:

- LinkedIn #tinytapeout matt-venn

- Mastodon #tinytapeout @matthewvenn

- Twitter #tinytapeout @matthewvenn