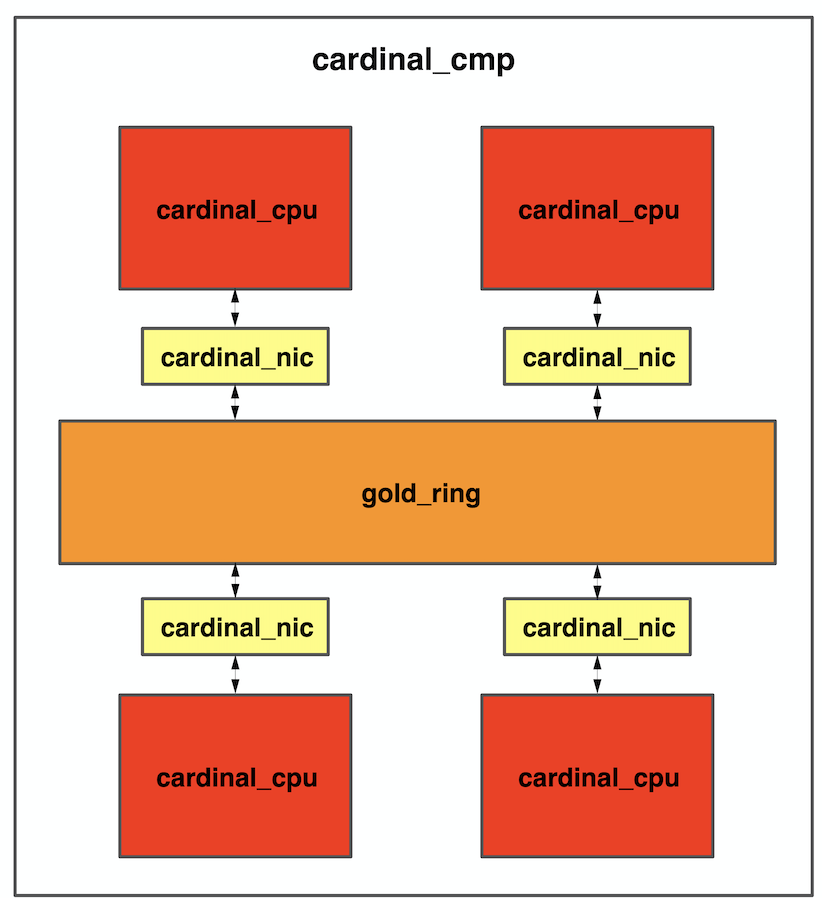

This Cardinal 4-core chip multi-processor system is implemented based on Cardinal processor with 32-bit address and 64-bit data and Cardinal 4-node ring NoC which supports packet (VCT or wormhole) switching. Cardinal NiC is short for network interface components that can be used to simplify packets changing between ring NoC and processors. Each register or buffer of NiC can be accessed using 2-bit memory address so memory instructions (LD or SW) can be used to access NiC and make it possible to transfer messages between different IP cores.

./Docs

All documents and spec files related to this project;

./project/design

All design source files;

./project/include

Related library files (gscl45nm) and simulation models used in simulation;

./project/netlist

Netlist file (.v), standard delay files (.sdf) and contraints files (.sdc) generated by Design; Compiler;

./project/pnr

Screenshot and log file of Cadence Innovus (P & R);

./project/report

Timing, area, power and also design checking log file generated by Design Compiler;

./project/scripts

Tcl scripts used by NC-Sim and Design Compiler;

./project/src

Source file used by Design Compiler to do logic synthesis;

./project/tb

Testbench file for individual modules;

./project/test_cases

Test_cases used by run.csh to function testing of top CMP module;

./project/work

Not applied;

./peoject/makefile

Makefile used to do simulation for RTL design (pre-simulation) and netlist (post-simulation);

./project/makefile_disable

Makefile used to do automatic simulation,

synthesis and static timing analysis

./project/run.csh

Csh scripts used to simulate the top cardinal_cmp.v or cardinal_cmp_syn.design

./setup_v1908.csh

Used to set all lab environments out project depends on