E2LP NES is port of fpga_nes, fpga-targeted Nintento Entertainment System emulator written in Verilog, for E2LP.

It is currently under development, and is most notably missing support for mappers and the DMC sound channel. At this point, it runs most NROM games capably (e.g., Super Mario Brothers, Excitebike).

In addition, this project includes a C++ Windows application called NesDbg, which communicates with the FPGA over USB UART to load ROMs, run unit tests, readwrite memory, etc. Project also contains an Arduino sketch for testing NES compatible gamepads.

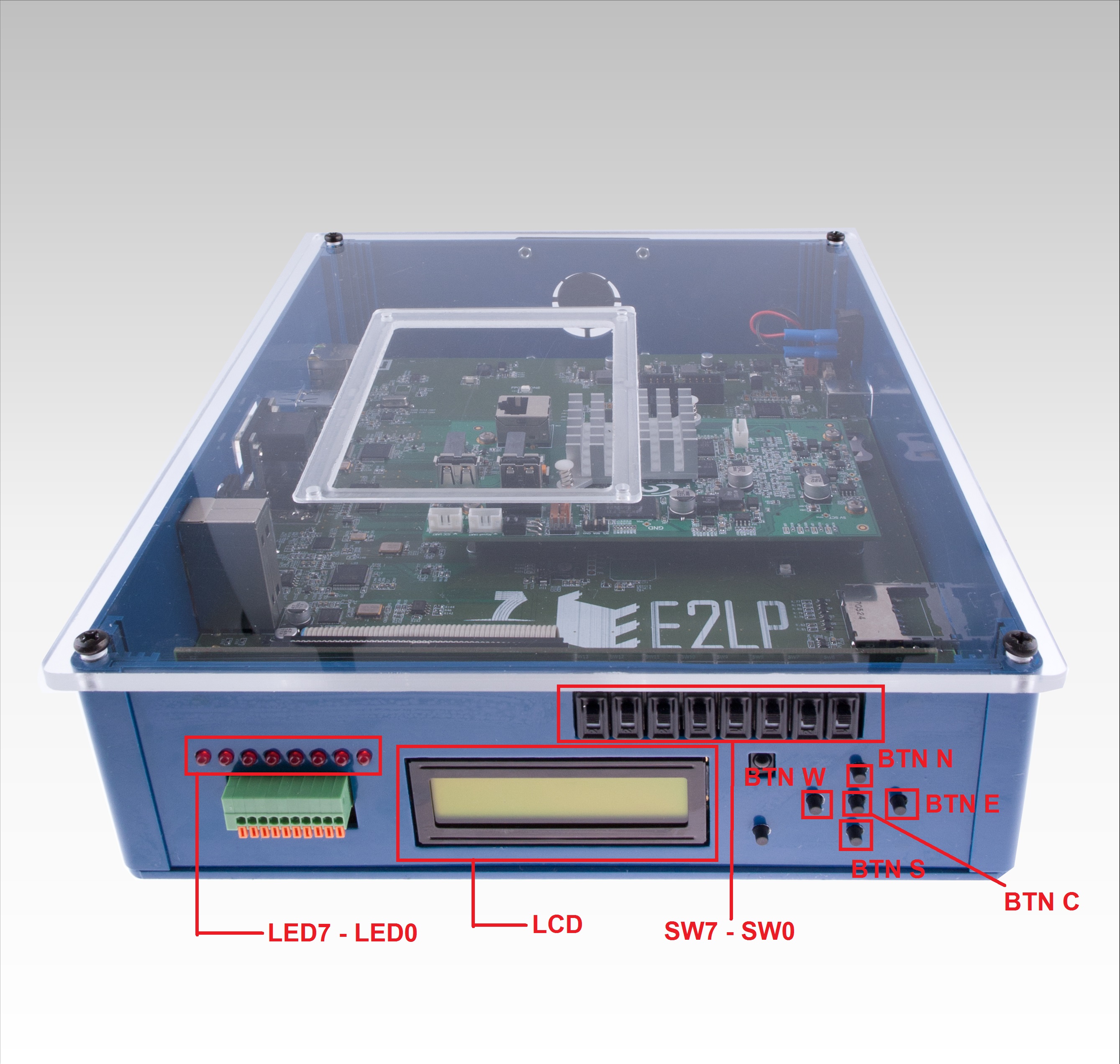

- E2LP develpoment board.

- VGA display connection for NES video output.

- RS-232 cable for communication between NES and NesDbg software.

- Piezo buzzer.

- 2 famiclone joypads.

| WIRE | PORT |

|---|---|

| Joypad latch | GPIO 3 |

| Joypad clock | GPIO 5 |

| Joypad 1 data | GPIO 1 |

| Joypad 2 data | GPIO 7 |

| Piezo buzzer | GPIO 2 |

| Sound volume | SW 0 - SW 3 |

| CPU Reset | SW 4 |

| TX indicator | LED 0 |

| RX indicator | LED 7 |