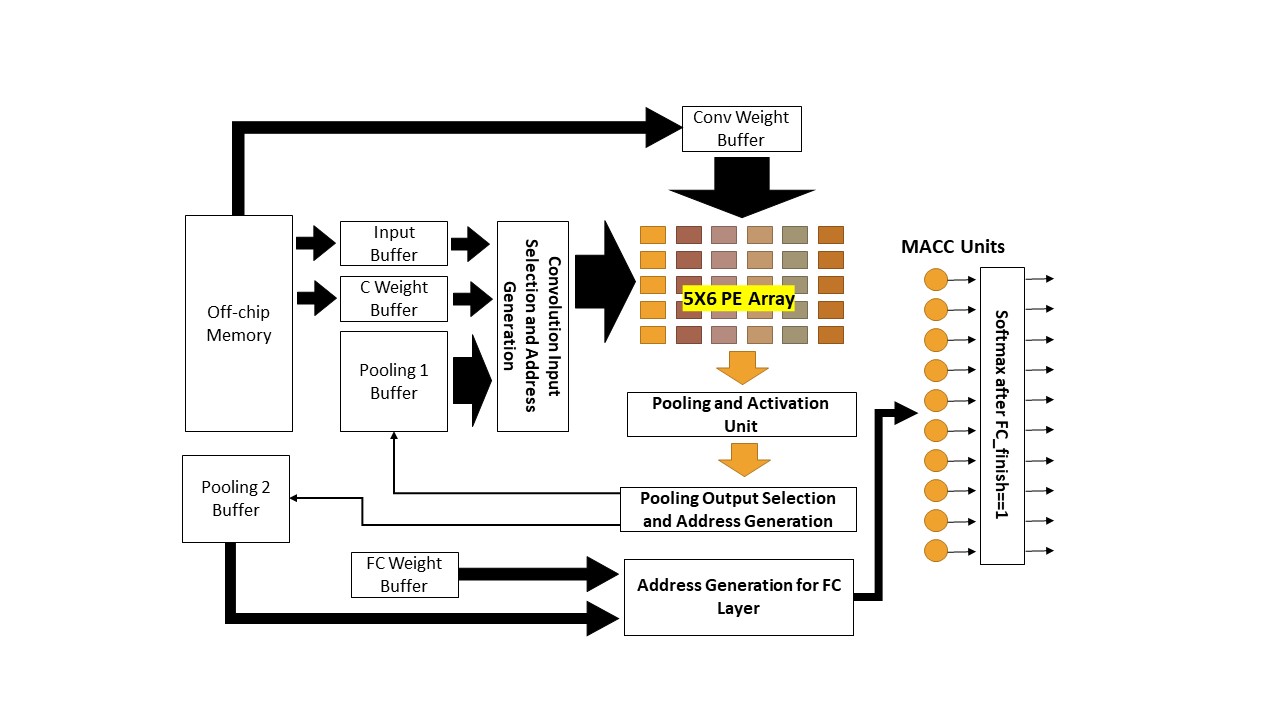

An open source Verilog Based LeNet-1 CNNs Accelerator for FPGAs. Trained weights of the model are in "W.mem" file in "Other-files" directory.

for more details on theory you can refer to https://arxiv.org/ftp/arxiv/papers/1901/1901.04986.pdf.

Please cite as: {Hazoor Ahmad, Muhammad Tanvir, Muhammad Abdullah, Muhammad Usama Javed, Rehan Hafiz, and Muhammad Shafique. "Systimator: A Design Space Exploration Methodology for Systolic Array based CNNs Acceleration on the FPGA-based Edge Nodes." arXiv preprint arXiv:1901.04986 (2018).}

Vivado 2017.1 or above (as I have used)

- Make a new project in vivado

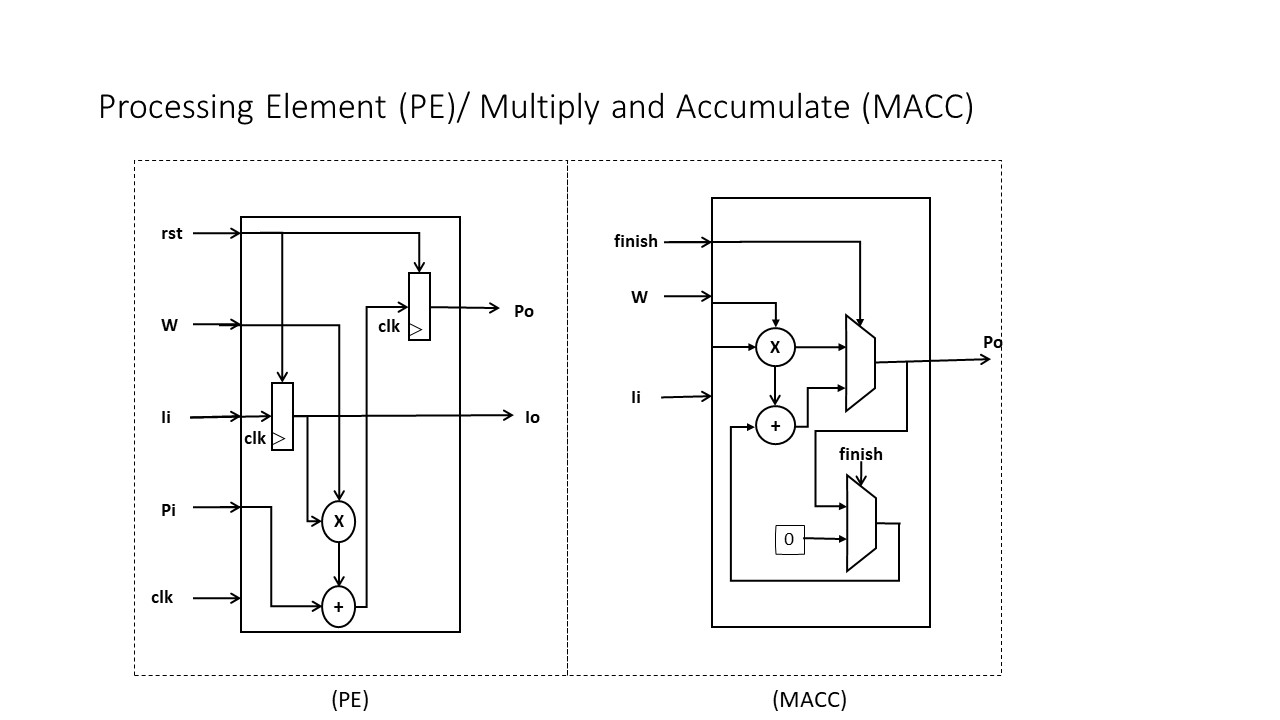

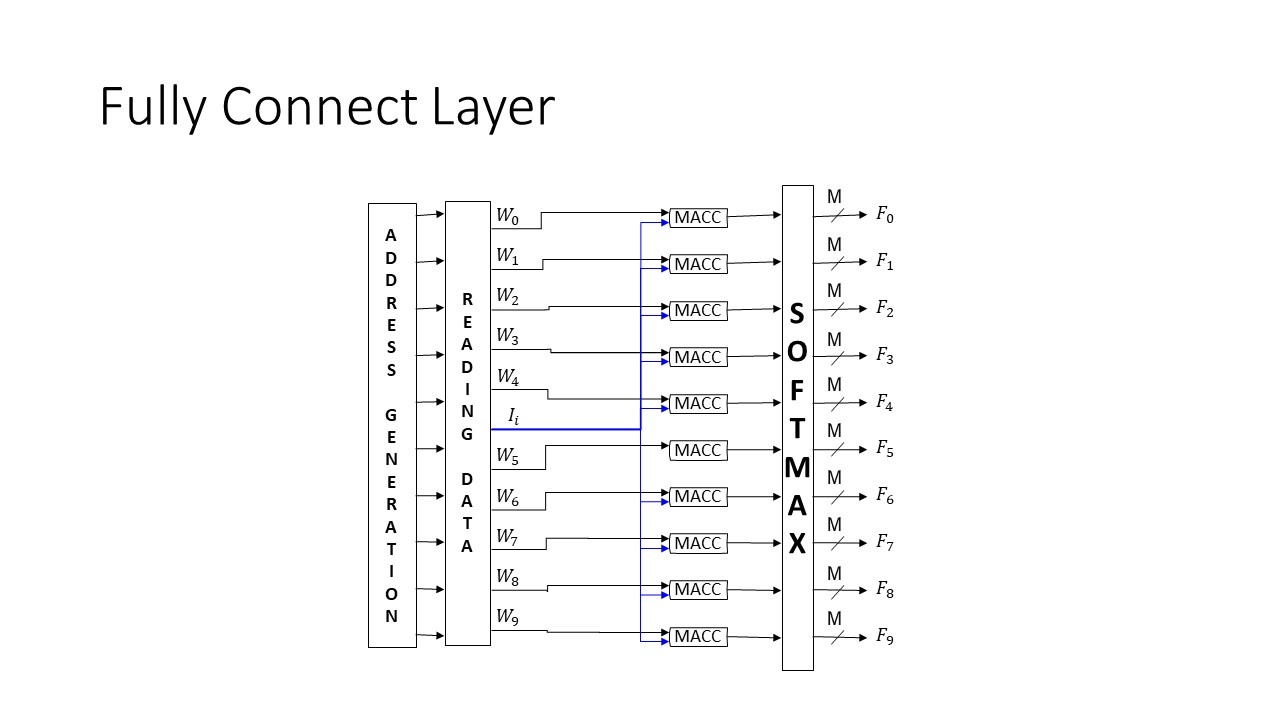

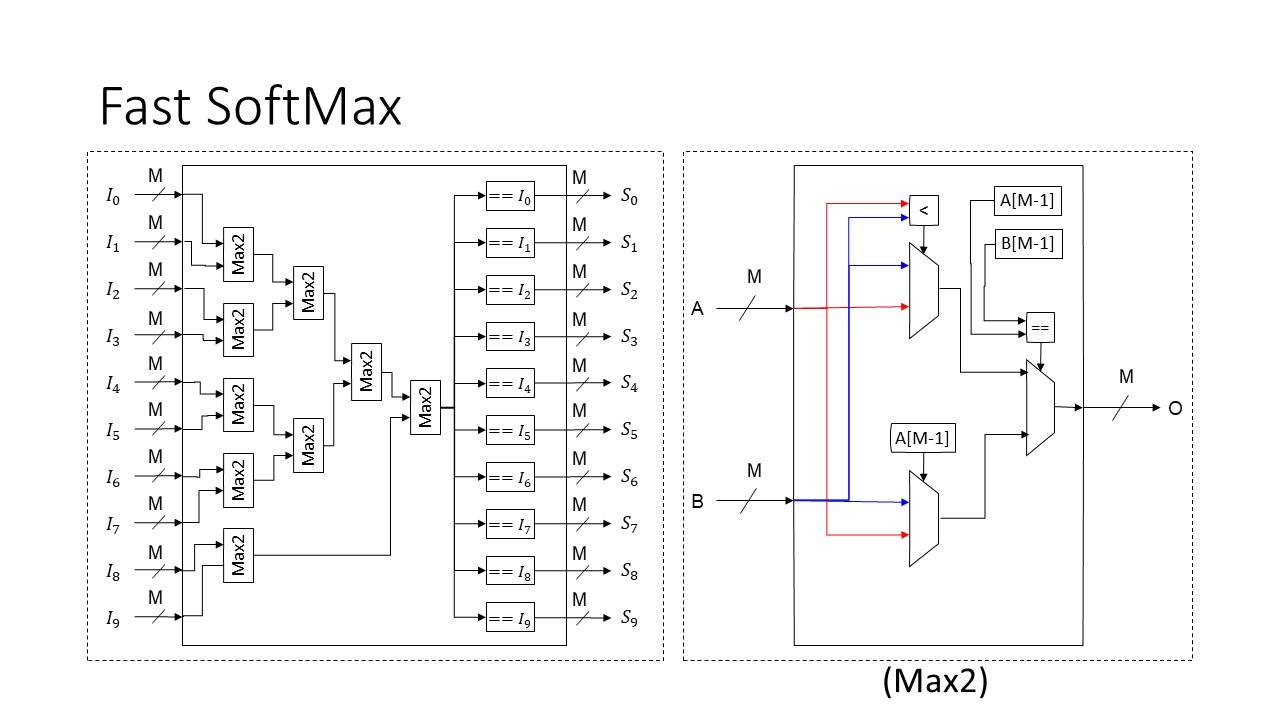

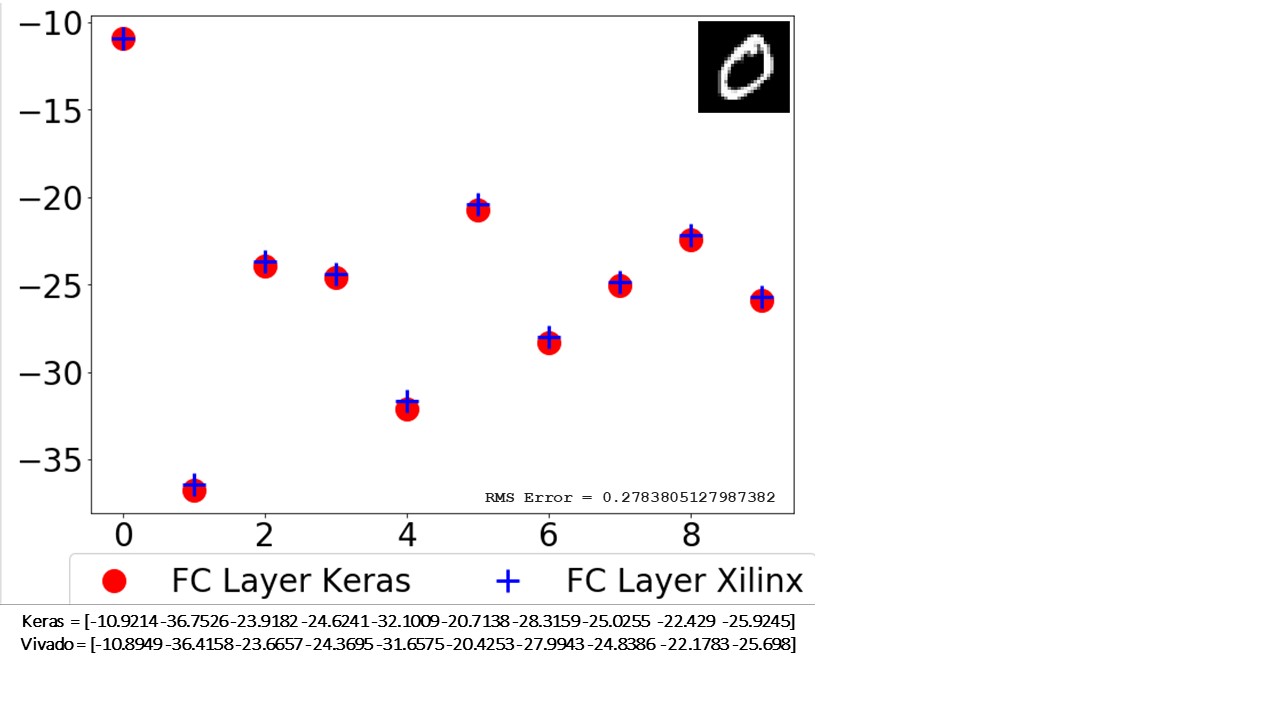

- Add files (Conv3D.v, FC.v, LeNet.v, MACC.v, Multiplication.v, PE.v, PE_Array.v, max2.v, softmax.v) from folder (Verilog-Source-Files) to your project as 'design sources'.

- Add file (tb_LeNet.v) from folder (Other-Files) to your project as 'simulation sources'.

- Add files (I0.mem, I1.mem, I2.mem, I3.mem, I4.mem, I5.mem, I6.mem, I7.mem, I8.mem, I9.mem, W.mem) from folder (Other-Files) to your project as 'design sources'.

- Change inputs from line 56 of LeNet.v in folder (Verilog-Source-Files). [like I4.mem instead of I3.mem]

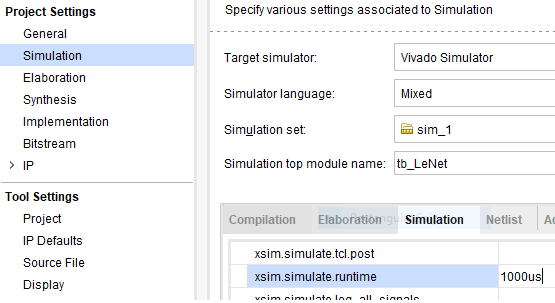

- Before simulation confirm simulation time should be more than 10000ns to do it go to:

Project Manager -> Settings -> Project Setting -> Simulation -> Find Simulation tab -> change xsim.simulate.runtime from 1000ns to 1000us

set_property -name {xsim.simulate.runtime} -value {1000us} -objects [get_filesets sim_1]

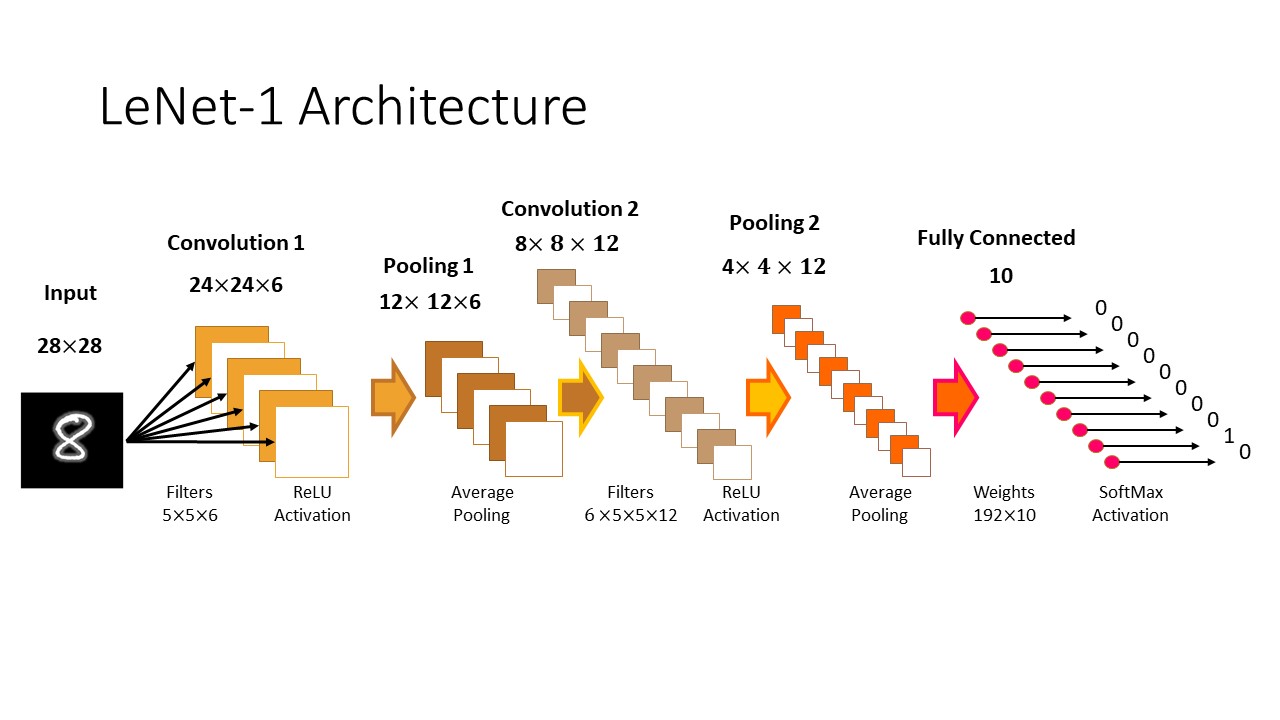

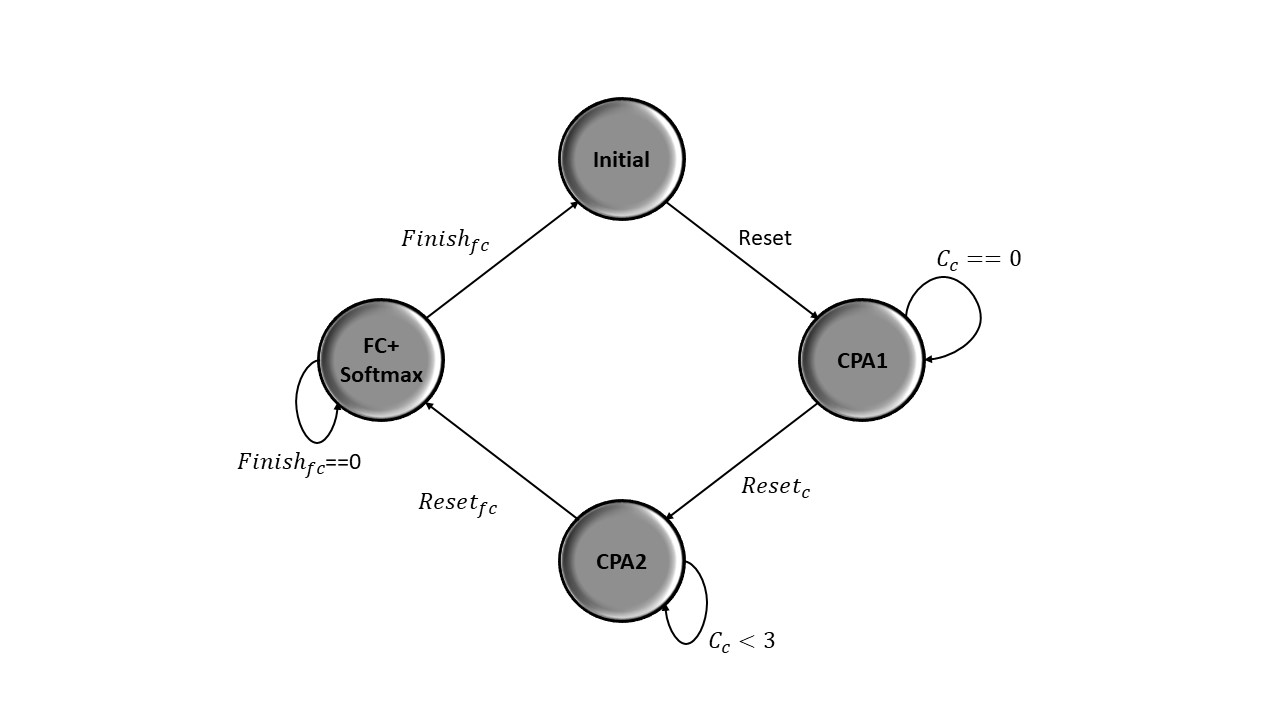

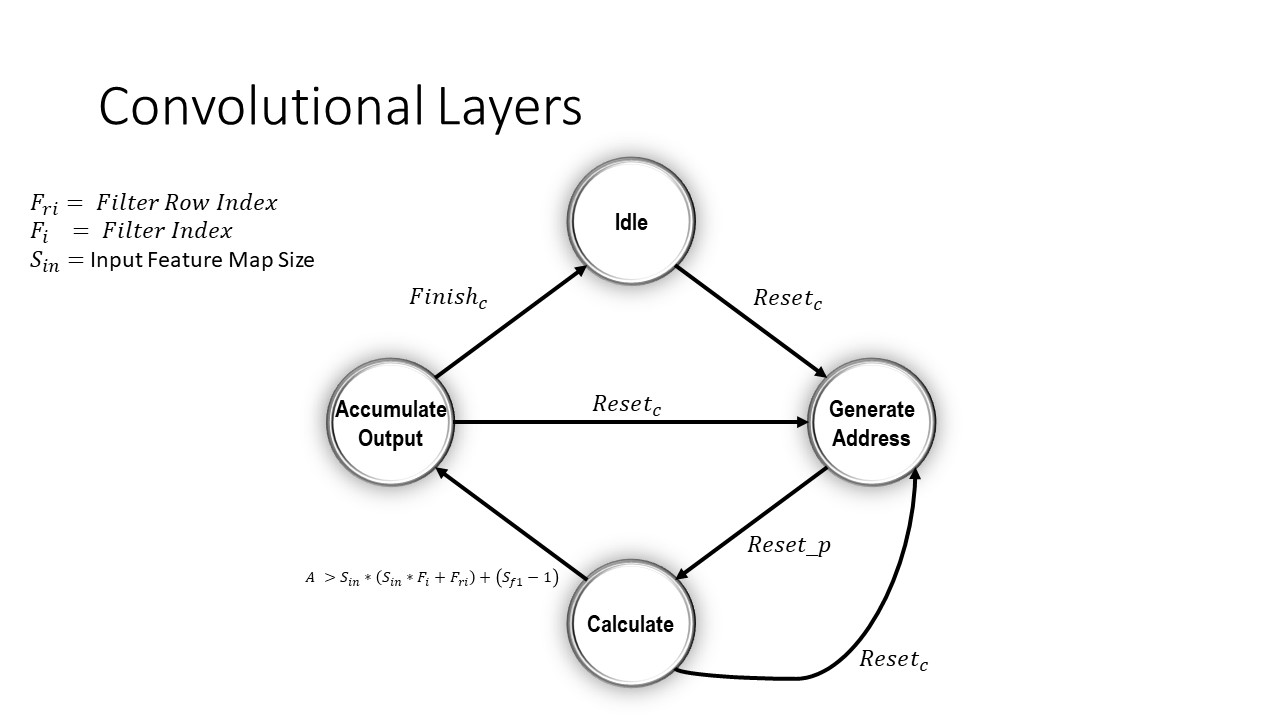

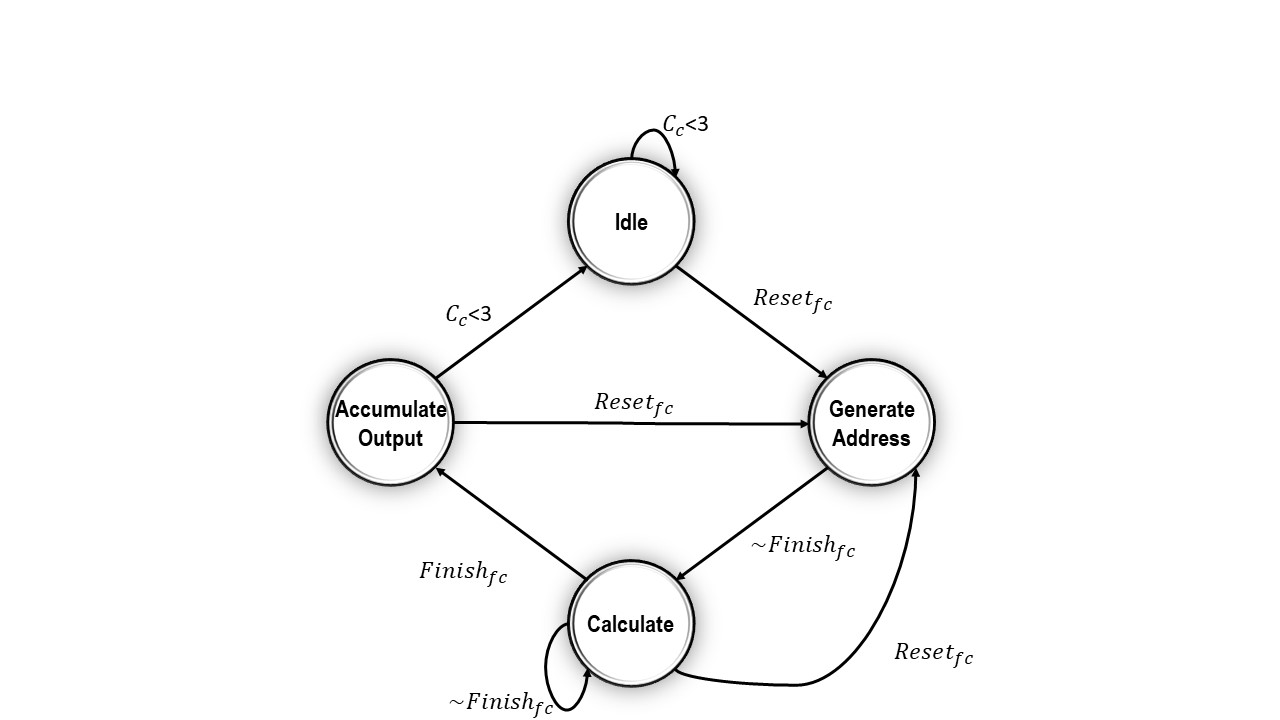

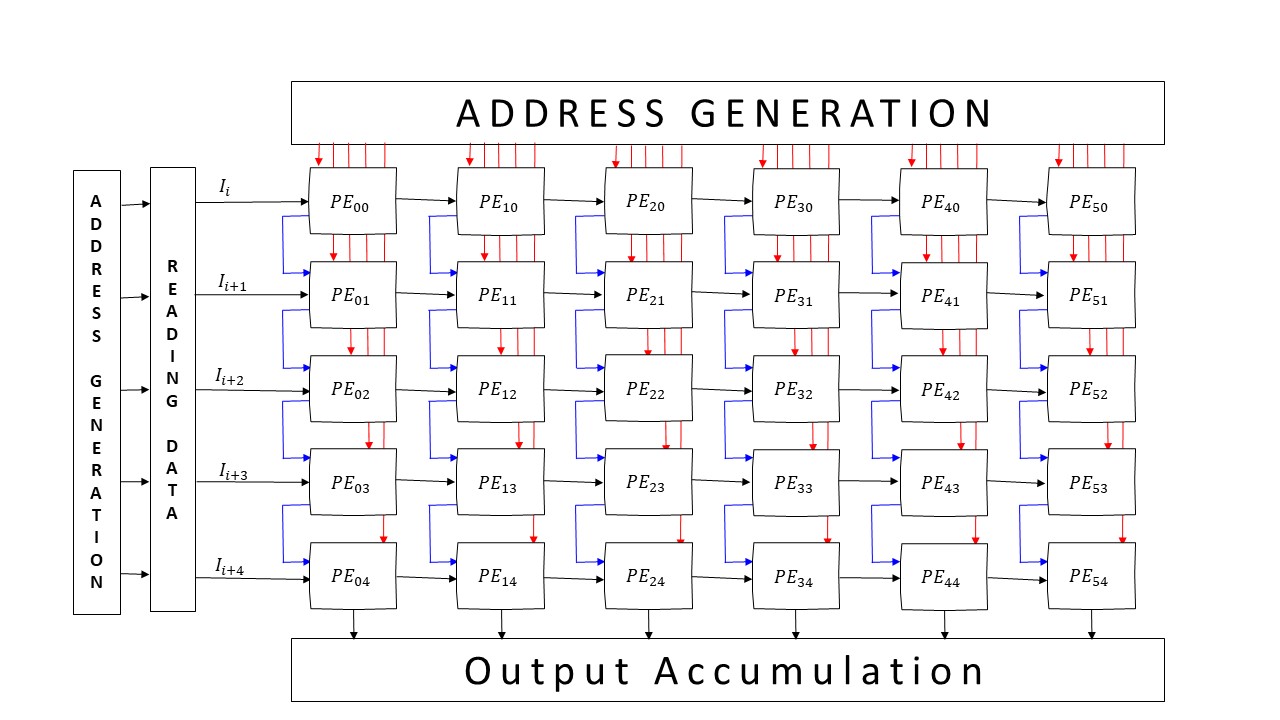

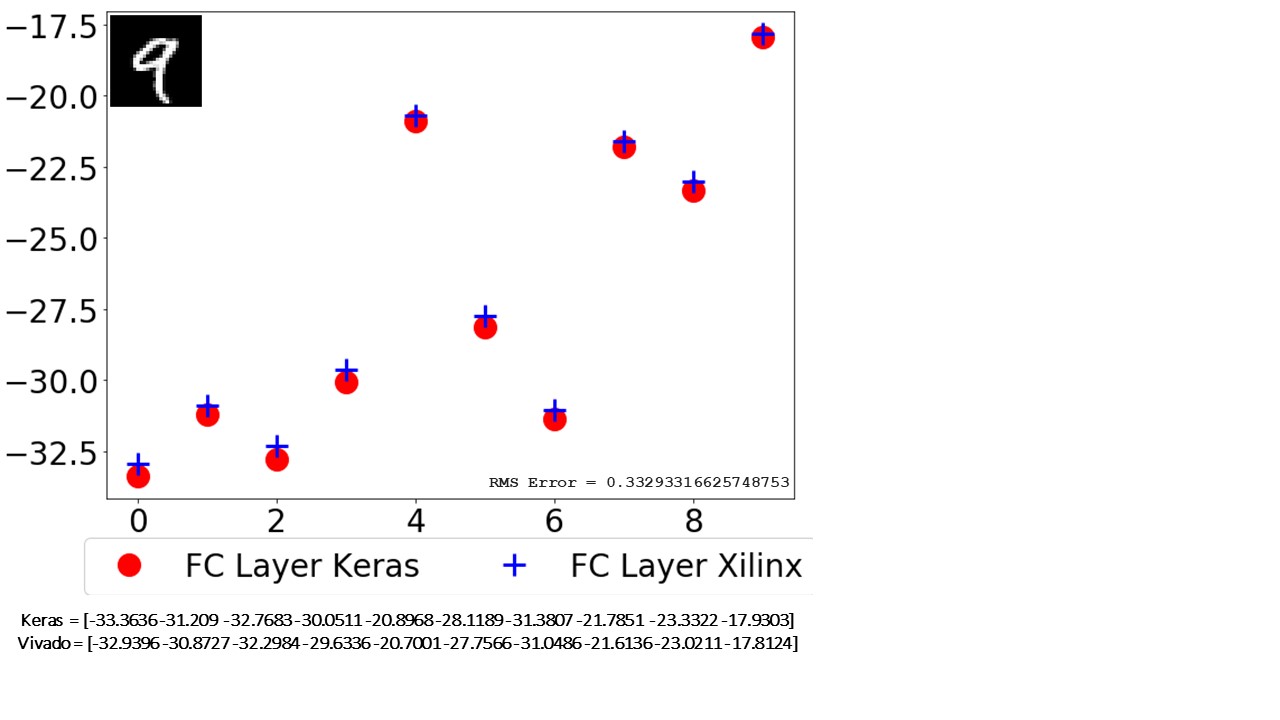

LeNet-1 Architecture for handwritten digit recognition is given by