This project uses the hardware platform about Edgeboard Lite (Baidu), and the chip is xazu3eg-sfvc784-1-i, which has 360 DSPs and 216 BRAM_36Ks.

Hardware schematic.

Hardware configuration script file for Zynq UltraScale+ MPSoC IP core in Vivado.

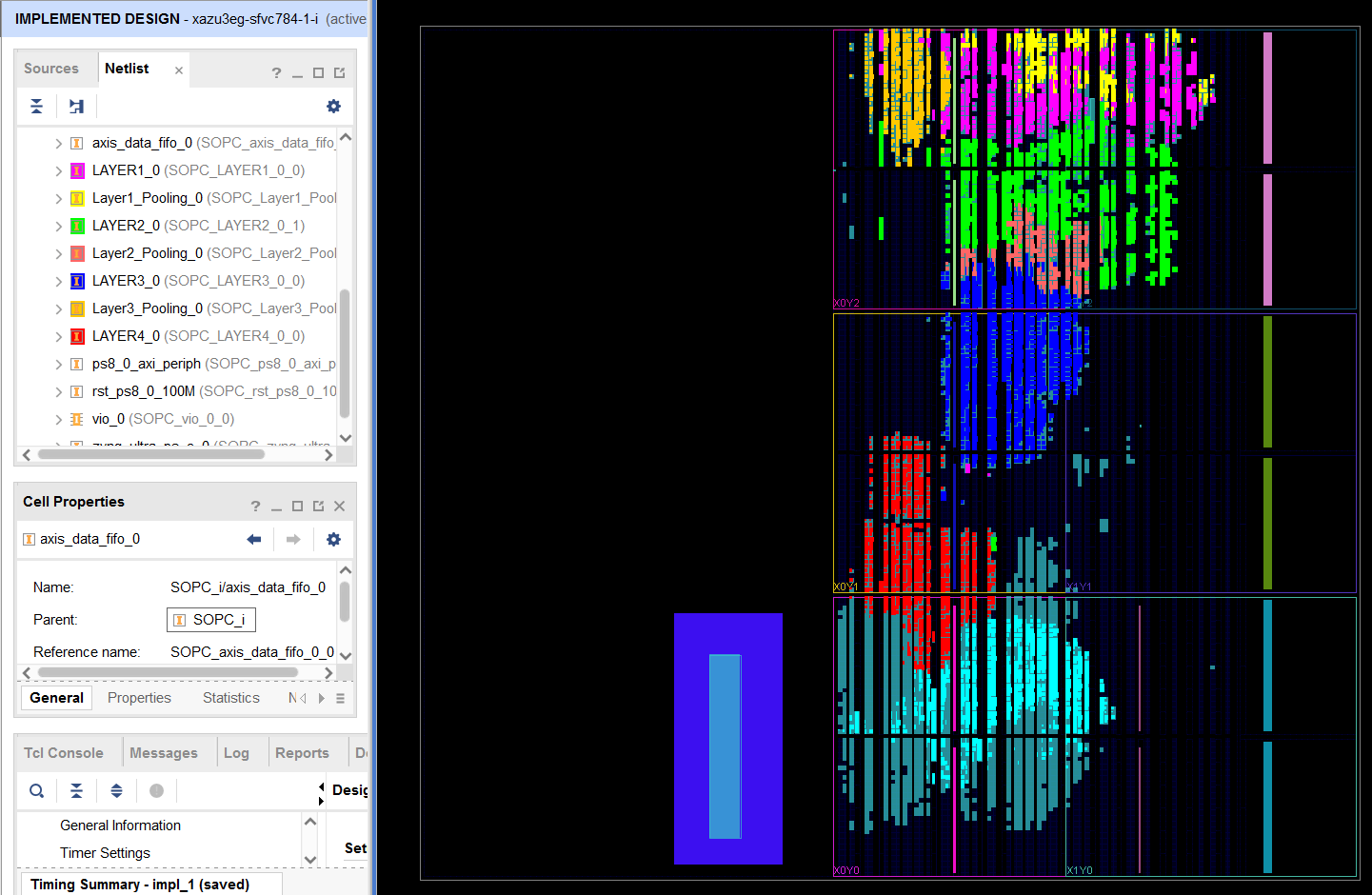

First implementation result is used to verify our research, and the board device is implemented as following:

It is abviously that the implementation result can not make full use of hardware resources.

Then we should make a balance of inter layer.

An inter layer balance is implemented after design space exploration, and the new result of board device implmentation is following:

/Impl%20of%20Device2.png)

From the above result, we can conduct that new implementation make full use of hardware resources.

Similary, CNN-SVM of inter layer balance is also deployed in this platform.

/Impl%20of%20Device3.png)

This result is the optimal accelerator for CNN-SVM hybrid network based on FPGA.

The standlone program of CNN-SVM. It is running on the PS of Edgeboard Lite. An external SD Card (FAT32) is necessary for storing the Mnist dataset files. The xilffs lib driver (FATFS) should be added when creating project board support package(BSP).

This includes two examples for illustrating the quantification process. The quantization process is also applicable for SVM, and the accurancy remains unchanged.