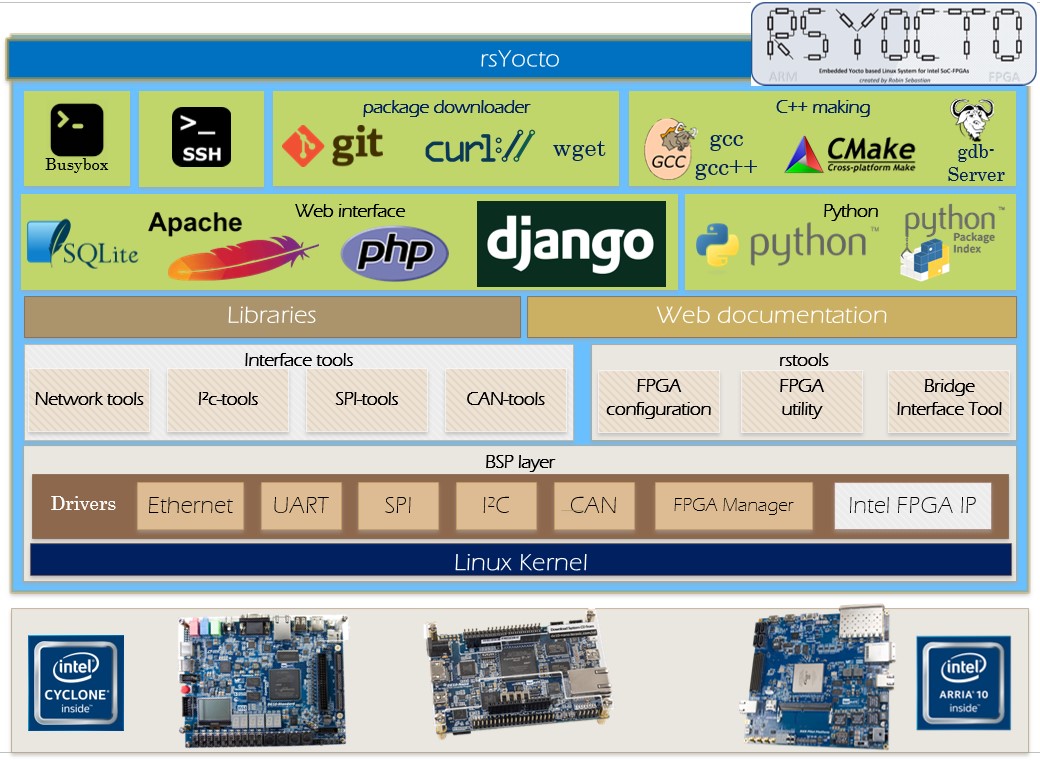

rsyocto is an open source Embedded Linux Distribution designed with the Yocto Project and with a custom build flow to be optimized for Intel SoC-FPGAs (Intel Cyclone V and Intel Arria 10 SX SoC-FPGA with an ARM Cortex-A9) to achieve the best customization for the strong requirements of modern embedded SoC-FPGA applications.

rsyocto implements a modern Linux Kernel (linux-socfpga 5.11) and brings a set of today fundamentally needed components to Intel SoC-FPGAs to help to simplify the complex process of development for FPGA-, Industrial 4.0-, Internet of things- (IoT), automotive- and deep learning (AI) accelerator- applications.

To realize that Python3 with the Python Package manager pip (PyPI) and the Apache Webserver with PHP are already included. Thereby it is really easy to install Python applications from the Raspberry Pi on a powerful Intel SoC-FPGA. rsyocto is for its best optimization complete console based, but the Apache Webserver can bring any modern GUI to Computers, Smartphones or Tablets, by hosting for example a monitor web interface. For that the Python Web framework Django 3.0 is pre-installed.

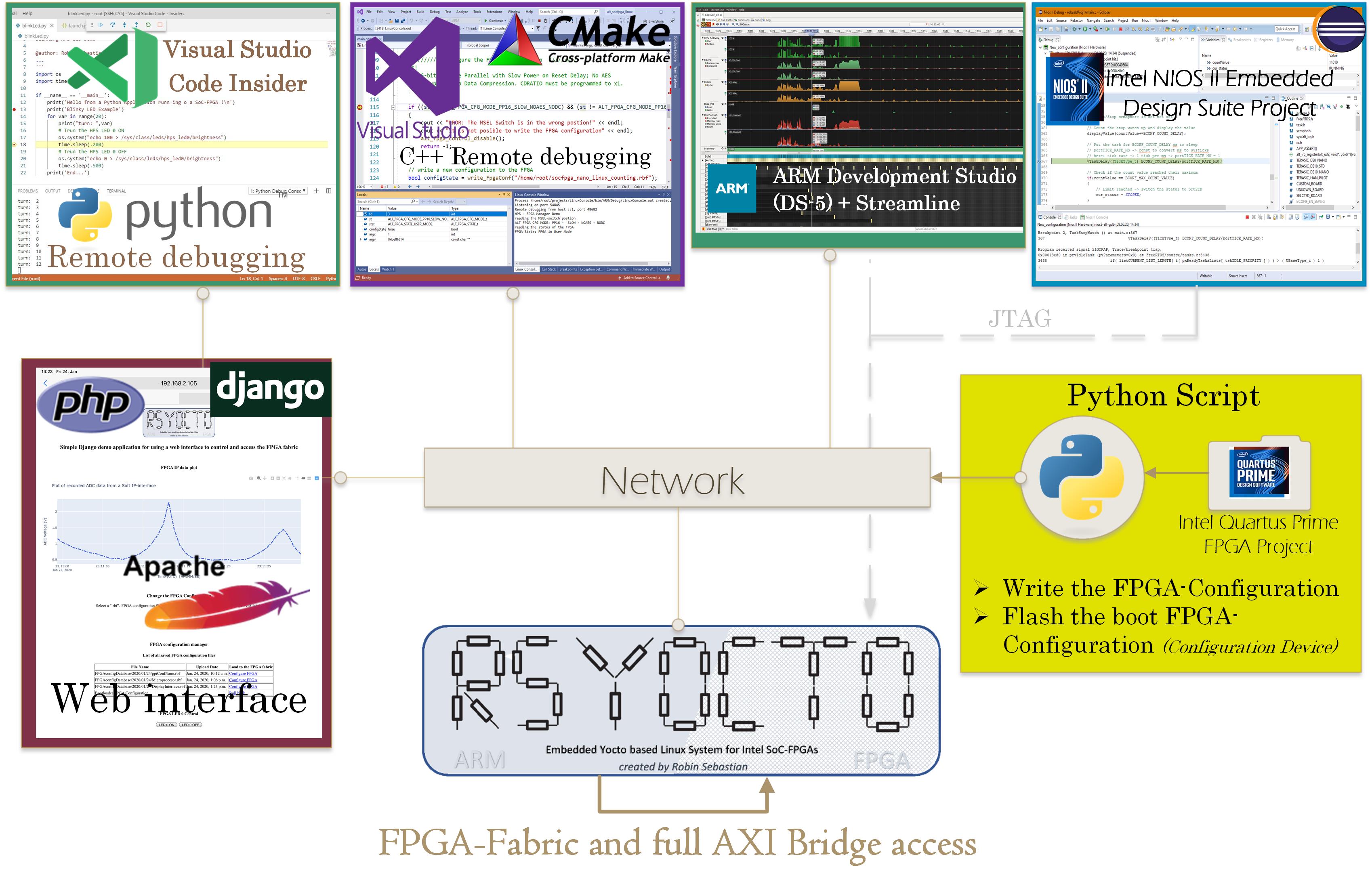

During development, a major concern was placed on the integration of powerful and simple to install development IDEs that do not require a JTAG-connection or any cross-building environment. All kinds of rsyocto applications and parts can be build, deployed and even debugged over the network (fully routable over the Internet). With the implementation of Microsoft Visual Studio and Visual Studio Code a simple installment and quick jump start in the development process is possible, because all required compilers run directly on rsyocto. The custom developed build system goes even a step further.

rsyocto was designed with an automatically Python based build system. That generates a highly optimized customized rsyocto-image with the installment of users private applications, boot configurations, scripts, FPGA-Configuration files, that will be configured on the FPGA Fabric before the Linux boots and a lot more with only an Intel Quartus Prime FPGA project. This feature enables users, without the requirement of deep Linux knowledge, to design own rsyocto flavors with it own FPGA projects for complex Intel SoC-FPGAs. The build system generates the 3-stage bootloader, finds the right Embedded Linux Distribution files, configures the partitions of the final image in the right way, configures theOpenSSH Server and automates a lot more with only an single shell command.

For FPGA developers, a Python script has been developed that allows the FPGA-Configuration to be written over the network (SSH/SFTP) by simply running it in an Intel Quartus Prime FPGA project folder. The script can compile the FPGA project and change the FPGA-Configuration of the bootloader (u-boot) to start the FPGA-Configuration after a restart. This has the same effect as a classic FPGA-Configuration device.

rsyocto is with the implementation of drivers for all Hard-IP Interfaces (e.g. I²C-, CAN-BUS,…), all Interfaces between hard processor system (HPS) and the FPGA Fabric and simple Linux test commands (e.g. i2c-tools or can-utils) ready for the development of industrial connected solutions. For instance, with a single command rsyocto is capable to load a new FPGA-Configuration (FPGA Manager) or to read and write the ARM AXI-Bridge Interface to the FPGA Fabric. The Linux test commands allow in a simple fashion to communicate with the FPGA Fabric via all available interfaces, such as Lightweight HPS-to-FPGA- (lwhps2fpga) , HPS-to-FPGA-Bridge (hps2fpga) , shared-memory (hps2sdram) or general purpose signals (gpi and gpo). Python- and C++- demo applications show a powerful way with a high throughput to interact with FPGA Soft-IP.

The final rsyocto-Image can be installed on a SD-Card with any commonly used Boot-Image creating tools. Versions are available for the Terasic DE10 Standard- (Intel Cyclone V SoC-FPGA), Terasic DE10 Nano- (Intel Cyclone V SoC-FPGA), Terasic Han Pilot (Intel Arria 10 SX SoC-FPGA) and Terasic DE0-Nano SoC (Intel Cyclone V SoC-FPGA).

On the Terasic DE10 Nano board the Arduino Uno header can be used to connect external devices to a Hard-IP Bus, because the HPS interfaces with the pre-installed configuration are routed to FPGA I/O-Pins. An example shows how to use rsyocto, the FPGA-to-HPS-Bridge to access Hard-IP of the HPS with a NIOS II Soft-Core Processor running FreeRTOS. NIOS II Eclipse platforms can also be generated automatically.

I noticed that right now only desktop Linux systems, like Ubuntu, are available for free. In my opinion they are not designed for embedded SoC-FPGAs and therefore, they cannot be considered for long-term embedded systems.

That was for me the starting point to try to develop my own fully optimized Linux distribution. Shortly after, I announced that the Intel development tools and documentations for HPS development are not nearly as good as those for the FPGA part. At the beginning it was really complicated to get anything running. After a hard time, I'm able to present this first working project. To get there, I had to develop my own approach which I think is the best for embedded use-cases by designing my own build flow with my own Python scripts.

I think nearly everybody will have the same problems I had during the development. For that reason, I try to give everybody a solution for their rapid prototyping. Within this repository I have also integrated a step by step guide to show my solution with the openEmbedded Yocto project and the Intel SoC EDS.

With my first versions I got only positive feedback from the community.I will continue my work and upload newer versions. I invite everybody to submit issues, comments and ideas and to support me in other ways...

Build, debug and deploy your applications over the network

Ready for powerful remote development IDEs and fitted with a Web server to host modern web applications

Ready for powerful remote development IDEs and fitted with a Web server to host modern web applications

-

Embedded Linux specially developed for Intel SoC-FPGAs

- Linux Kernel 5.11 (Source)

-

Full usage of the Dual-Core ARM (ARMv7-A) Cortex-A9 with

- The ARM (SIMD) NEON-Engine

- The Vector Floating Point Unit (VFP)

- The ARM Thumb-2 Instruction Set

- The ARM PL390 Generic Interrupt Controller (GIC)

- The ARM TrustZone for ARMv7-A and Arteris FlexNoC Network-on-Chip Interconnect for the Intel Arria 10 SX

- The ARM CoreSight Debug and Trace Engine with ARM Development Studio (DS-5) support

- The external memory interface controller (EMIF) (SDRAM DDR3/DDR4 controller) of the Intel Arria 10 SX with Early I/O enabled

-

For the best performance completely custom optimized

-

Console based (GUI less) with

Busybox -

Watchdog timer is enabled

-

FPGA Fabric configuration during the boot (u-boot script) and with a single Linux command

-

All Bridge Interfaces between the HPS and FPGA are tested, enabled and ready for use!

-

Tools to interact with the FPGA Fabric via the ARM AXI HPS-to-FPGA bridges

-

Access the FPGA Fabric with Shell scripts, C++-, Python-Applications or PHP or Django web applications

-

HPS Hard IP components (I²C-,SPI-, CAN-BUS or UART) are routed to FPGA I/O

- Ready for connecting different devices

- e.g. Arduino Uno shields

- Ready for connecting different devices

-

Accelerometer and ADC can be accessed via Python or C++ (Demos available) (only for the Cyclone V boards)

-

socketCANpre-installed and pre-configured (examples available!) (Only for Cyclone V SoC-FPGAs) -

Console based Bus test tools (e.g.

can-utils) -

USB Host support with test tools (e.g.

lsusb) -

Console memory dump tools (e.g.

devmem2) -

Full

Linux Network stackwith dynamic and static iPv4 is supported -

OpenSSH-Serverstarts automatically during boot and is configured for user authentications -

UTC Time is synced during bootup with

htpdateand a HTTP Time server -

A virtual software random number generator (RNG) is used (This SoC-FPGAs have no build in TRNG.)

-

resolvconfthe Linux DNS network tool is pre-installed -

Pre-installed development tools and DevOps

gcccompiler 9.3.0glibcandglib-2.0(The GNU C Library)cmake3.16.5Python 3.8Python3-devandPython-devgit2.31,wget1.20.3,curl7.69.1

-

Support for remote based development IDEs pre-installed

- Visual Studio Code for remote Python debugging

- Visual Studio Code for remote Interface development

- Visual Studio for remote C++ debugging

- Visual Studio Code for remote C++ debugging with

cmake - ARM Development Studio (DS-5) for remote- (Ethernet) and JTAG- C++ debugging

•gcc-compilerandgdb-server

-

ARM Development Studio (DS-5) Streamline is pre-installed and immediately after boot is ready for trace analysis

-

The "

NIOSII_EclipseCompProject" can generate custom Eclipse for NIOS II projects with for instance the real-time operating system (RTOS) FreeRTOS -

Python,Python3 -

Apachewebserver withPHPandSQLite -

git,curlandwgetdownload manager -

Latest

Djangoversion is pre-installed for Python-based web framework development -

udate-rc.dandcrontabfor startup- and time-triggered shell script scheduling -

Full integrated Python

pip3(Python-pip) package manager -

opkgpackage manager 0.4.2 enables to add some packages from different Linux Distributions. -

Custom designed

Build Systemto generate the entire bootflow for Intel SoC-FPGAs automatically- Allows to design highly optimized rsyocto flavors for your specific requirements

- Overview of the main feature of the "socfpgaPlatformGenerator" Build System:

- Automatically generate a bootable image file with configuration provided by a Quartus Prime FPGA project

- Cloning and compiling of the u-boot bootloader for Intel SoC-FPGAs

- Allows a highly optimization of the u-boot (e.g. via Linux

menuconfig) - In case of the u-boot script is configured to load a FPGA configuration the depending FPGA configuration will be generated

- Allows to pre-install any files or operating systems to a SD-Card image

- Boot image (.img) file generation for distributing Embedded Linux Distributions

- Dynamic mode: Partition size = Size of the files to add to the partition

- Linux Device Tree (.dts) -files inside a partition can be automatically compiled and replaced with the un-compiled file

- Compressed files (e.g. "tar.gz") containing for instance the Linux rootfs can be unzipped and automatically added to the partition

- To add the following to a deployable and shareable image file

- Custom bootloader configuration

- FPGA configuration files

- u-boot boot script

- Files/Applications

- Software Libraries

- Web sites

- Linux Shell Startup scripts

- Network Interface settings

- Python script to write the FPGA-Configuration over the Network and via JTAG

- Just executed inside the Intel Quartus Prime FPGA project folder

- JTAG mode allows to write the FPGA-Fabric with unlicensed IP (e.g. NIOS II Core) for test purposes

- Communicates with the SoC-FPGA board over the network by using SSH and SFTP

- Compiling the Intel Quartus Prime FPGA project

- Changing the running FPGA-Configuration of the FPGA-Fabric

- Changing the bootloader (u-boot) FPGA-Configuration

- After a restart, u-boot writes the new FPGA-Configuration into the FPGA-Fabric

- Behavior like a classical FPGA configuration device

- Full supported boards

- Terasic DE10-Standard (Intel Cyclone V SoC-FPGA)

- Terasic DE10-Nano (Intel Cyclone V SoC-FPGA)

- Terasic DE0-Nano SoC Kit (Atlas-SoC Kit) (Intel Cyclone V SoC-FPGA)

- Terasic HAN-Pilot (Intel Arria 10 SX SoC-FPGA)

| Level | Objective | Guide |

|---|---|---|

| 1 | Booting rsyocto on your Board | Getting started Guide |

| 2 | Use of Hard-IP, FPGA-IP and FPGA-Configuration of the FPGA-Fabric | Step by step guide 1 |

| 3 | Debugging C++ applications remotely with Microsoft Visual Studio | Step by step guide 2 |

| 4 | Debugging Python applications remotely | Step by step guide 3 |

| 5 | Analyzation of applications with ARM Development Studio (DS-5) Streamline | Step by step guide 4 |

| 6 | Developing a custom FPGA-Configuration with Intel Quartus Prime | Step by step guide 5 |

| No. | Objective | Guide |

|---|---|---|

| 1 | Changing the FPGA-Configuration of rsyocto over the network with your FPGA project | Guide |

| 2 | Designing of custom rsyoto versions with your content and FPGA project | Guide |

| 3 | Build your own custom Linux Distribution for Intel SoC-FPGAs with the Yocto Project | Guide |

| No. | Objective | Guide |

|---|---|---|

| 1 | Transmitting CAN-Bus packages with Python | Guide |

| 2 | Developing a Django web application for interacting with the FPGA Fabric | Guide |

| 3 | Writing a Linux Startup script | Guide |

| 4 | Examples of using Microsoft Visual Studio for C++ development | Guide |

| 5 | Using the Intel NIOS II Soft-Core Processor, running FreeRTOS, to interact with HPS Hard-IP | Guide |

| Folder | Content |

|---|---|

doc |

Documentation |

fpga |

Quartus Prime projects |

examples/python |

rsyocto Python examples |

build_system |

rsyocto build scripts |

The C++-Demo Project for Microsoft Visual Studio is available here.

The final rsyocto boot images (img) are available inside the packages-Part of this repository!

- Intel SoC FPGA Embedded Development Suite (EDS) 20.1 - Linux

- Intel Quartus Prime 20.1 Lite Edition - Cyclone V

- Intel Quartus Prime 18.1.0 Standard Edition - Arria 10

- LinuxBootImageFileGenerator

- socfpgaPlatformGenerator

- pydevmem

- PiP2Bitbake

- The Yocto Project

- meta-intelfpga

- meta-openembedded

The first version of rsyocto (release december of 2019) was developed with the Intel Embedded Development Suite (SoC EDS) version 18.1 and a custom Yocto Project meta-layer.

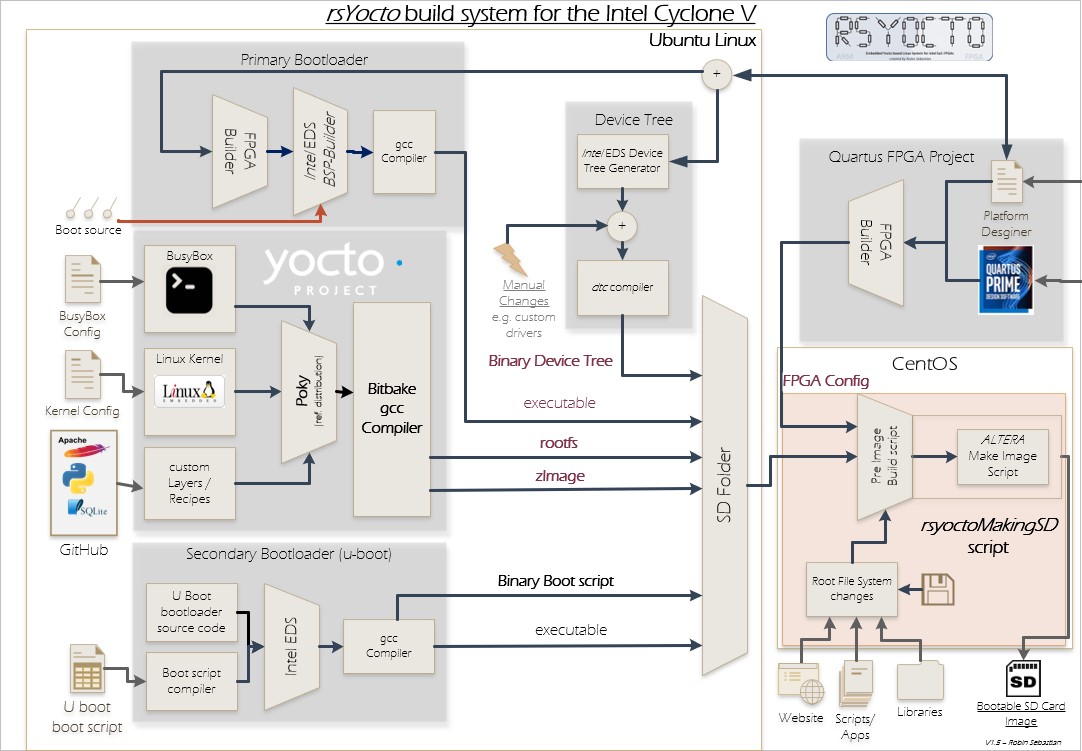

By default the specifications of these two development tools are not compatible to each other. To handle this issue I designed a custom build flow to progress the output Linux files of the Yocto project and to create all necessary boot stages.

This build system consists of an Ubuntu Linux and a CentOS Linux part. On CentOS was an Altera script used to generate the boot images.

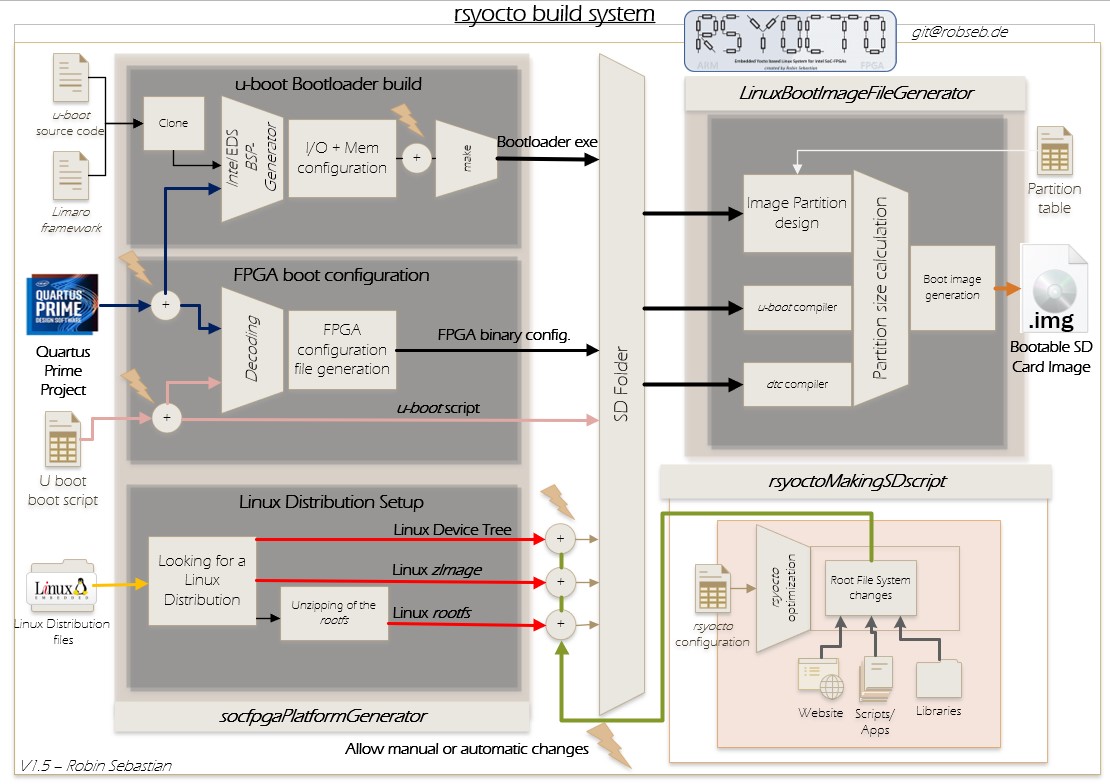

With re-design of the bootflow of Intel SoC-FPGAs with the SoC EDS Version 19.1 it was essential for me to design a new build system that can run on a single development computer (Ubuntu Linux or CentOS) and generate all required bootloaders fully automatically. My implementation has the big benefit, that it enables the generation of complete custom Linux versions with own FPGA Projects just by running a Python script. A deep Linux knowledge is for this process not required.

My first approach to design this Linux Distribution

Build Flow to create the first rsyocto version

Build Flow to create the first rsyocto version

Block diagram of the fully automated build system to design new releases

Block diagram of the fully automated build system to design new releases

This illustration shows my new development procedure and the required complexity to create rsyocto. I entirely automated the required complex bootflow to generate with a Intel Quartus Prime FPGA project and Linux Distribution files (e.g. zImage,rootfs,...) a bootable image file (.img). The script uses the Intel Embedded Development Suite (SoC EDS) in version 20.1 (2020) to design the necessary bootloaders based on the project settings for a Intel Cyclone V and Intel Arria 10 SX SoC-FPGA. It was designed to allow a high optimization of all components, such as the u-boot boot script or the Linux Device Tree. With this project I want to give other developers a full-functional system to reduce their development effort.

For designing custom rsyocto Versions it is only necessary to copy the "socfpgaPlatformGenerator"- Folder (available inside Repository's Releases part) into a Quartus Prime FPGA project folder. The included Python script can then generate the entire platform and can output a shareable and a bootable image file (".img").By the way, it is also possible to use this script with your own Linux Distribution files as I will show later.

My build flow consists of three stages to enable the support for other Embedded Linux platforms or with different Embedded Linux Distributions.

In the following table these three stages are visible. Stage one is on the lowest level and its classes will be used by the next stage.

| Stage | Python Script Name | Description | Output |

|---|---|---|---|

| 1 | LinuxBootImageFileGenerator | Class to automatically generate a bootable Image file with a specifiable partition table | Image file for enabling booting for almost all Embedded Linux distributions |

| 2 | socfpgaPlatformGenerator | Class to generate all necessary components for booting an Embedded Linux on Intel (ALTERA) SoC-FPGAs to build the bootloader (u-boot) and bring all components to a bootable image | Image for booting any Intel SoC-FPGA |

| 3 | makersyoctoSDImage.py | Python script to generate a custom rsyocto version with for instance rootfs changes (SSH configuration) | Image with a custom rsyocto flavor |

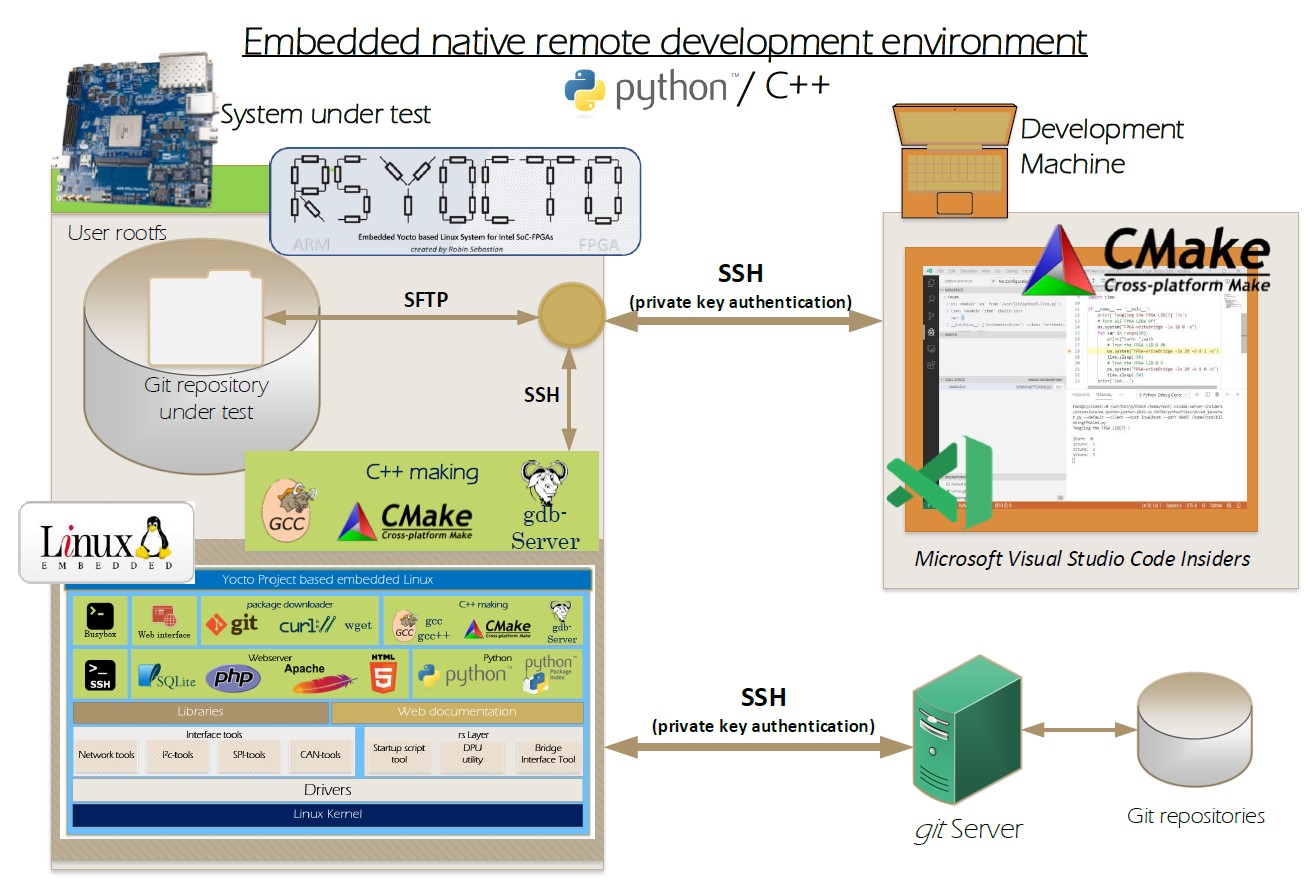

As described, I attach great importance to easy-to-use and powerful integrated development environments (IDE) for the Linux application development, due to the fact that the requirement and complexity of embedded applications grows exponentially year after year and the only way to counter act this trend are simple to install and use IDEs.

On the Linux generation site, I could simplify the complex multi-stage bootloader and Linux generation process with my Python scripts and pre-installed Bus-tools and the ARM Development (DS-5) Studio integration can help with hardware-level development and trace debugging. For the Linux Desktop application development, I used the following approach for my project:

My pre-configured and preferred Linux application development approach for C++,Python and Web

My pre-configured and preferred Linux application development approach for C++,Python and Web

This replaces the complex Eclipse- and Visual Studio IDEs and annoys all essential components on the Embedded Linux itself. In this concept the development projects are located for the best code tracking inside a git- (GitHub or GitLab) repository. This repo can be directly cloned to the rootfs of the Embedded Linux via a secure shell (SSH) interface over the network. A developer can use an another SSH connection to his development machine.

The development machine can be any computer that runs the compact code editor Microsoft Visual Studio Code Insider. The Microsoft Visual Studio Code Insider version allows the remote connection to an embedded ARMv7-A and ARMv8-A Linux distributions, such as rsyocto. Via SSH established VS Code a connection to the Linux Shell of Embedded Linux and via SFTP it is enabled to access the root file system (rootfs). The code editor uses the existing development tools on the target platform, such as the native gcc-compiler or Python for the application engineering and debugging (e.g. gdb-server).

A difficult to install and configure cross-compiler or Python framework are on the development machine not required, because everything runs directly natively on the development board. This makes the complex design and usage of a Linux Framework for this Linux Distribution unnecessary, due to the fact that the source code runs directly on the right location and can access all interfaces, files and libraries natively. This brings a high optimization in terms of feature usage of rsyocto and it can help to reduce the code size.

VS Code and rsyocto enable in this way to develop Python, PHP, HTML,CSS,C++ with cmake and a lot more. I wrote for these use cases examples. The ARMv7-A CPU of the Intel Cyclone V- and Intel Arria 10 SX- SoC-FPGA-devices are more than powerful enough to notice no major difference between cross-compilation- and native compilation-time. For cloning a git repo is only some user space on the rootfs required.

Yes, of course all HPS drivers are properly installed and tested. Demo applications and step-by-step guide are available, as well.

Yes, of course all bridge interfaces between the ARMv7-A- and FPGA- world are for both Intel SoC-FPGAs enabled and tested. Demo applications and step-by-step guide are available, as well.

Inside my meta-intelfpga BSP layer I described in details how to get started with the Yocto project for Intel SoC-FPGAs.

Also I published inside this layer the source code and documentation to bring tools to update the FPGA configuration with the running Linux and to interact with simple commands with the FPGA Fabric to the Yocto Project.

Yes, the build system enables to bring a custom Intel Quartus Prime Intel Cyclone V- or Intel Arria 10 SX- FPGA project to a bootable image with rsyocto installed. The u-boot will write the FPGA Configuration of the Intel Quartus Prime FPGA project to the FPGA Fabric. Please follow the instructions of this guide: "Designing of custom rsyoto versions with your content and FPGA project"

Yes, you can run rsyocto on almost every Intel Cyclone V- and Intel Arria 10 SX SoC-FPGA board with a SD-Card as boot source. My build system enables this feature. Please consider the guide: "Build your own custom Linux Distro for Intel SoC-FPGAs with the Yocto Project"

I designed a simple Python script to pre-install Python pip (PyPI)- Packages within a final Yocto Project Linux Image (see here).

I wrote Python Script to automatically generate an Intel NIOS II Eclipse Project with custom software components (e.g. FreeRTOS).

I will continue my work and upload newer versions. I invite everybody to submit issues, comments and ideas.

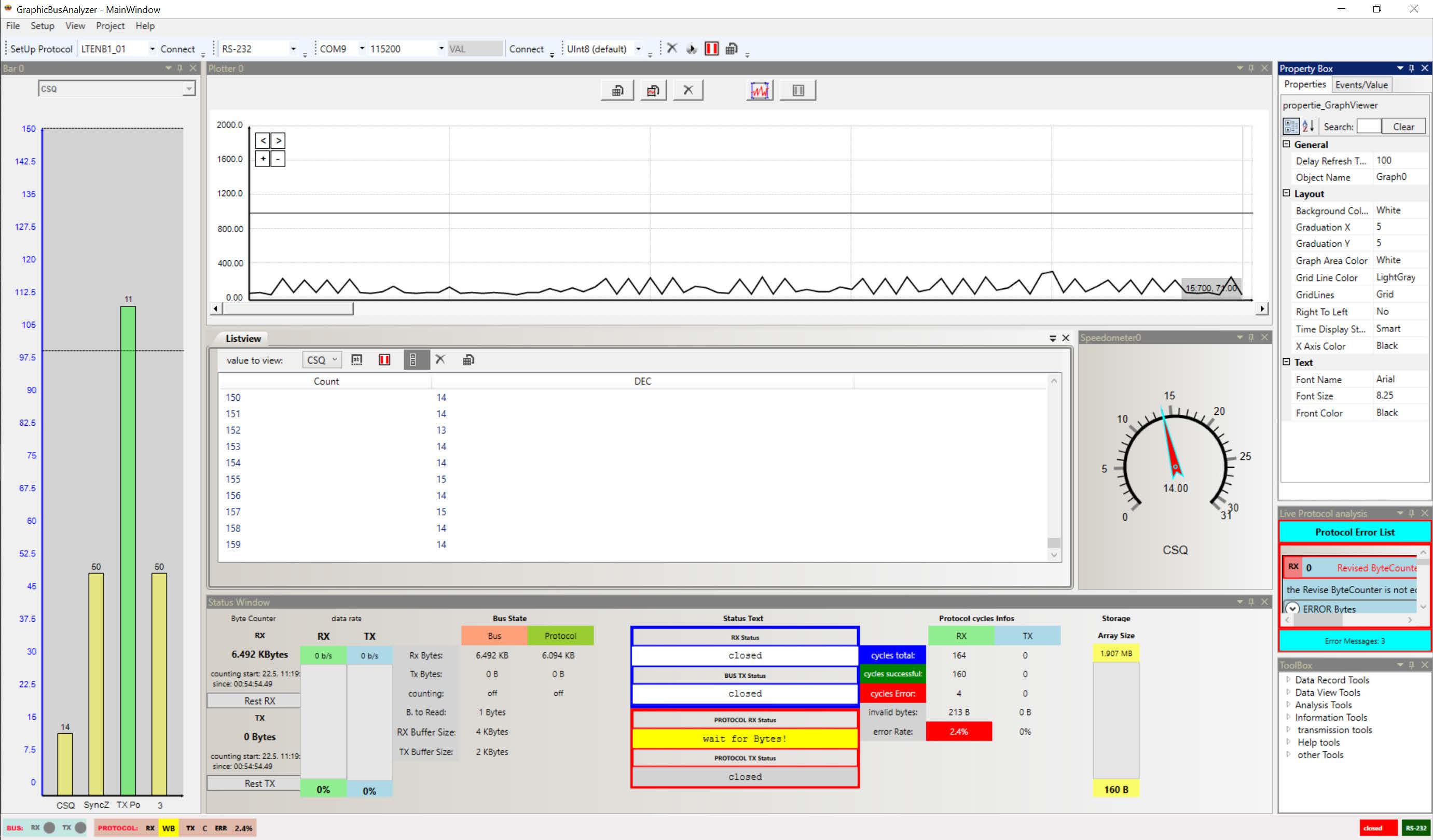

Currently I am working on a Windows 10 .net Desktop application to manage FPGA configurations and to allow to record data via the network. To release that I will design a server task, running on rsyocto, that can send Python- or C++-values with TCP to the desktop. The following screenshot shows the development state of this project.

- rsyocto; Robin Sebastian,M.Sc. (LinkedIn)

rsyocto is a self-developed project in which no other companies are involved. It is specifically designed to serve students and the Linux/FPGA open-source community with its publication on GitHub and its open-source MIT license. In the future, rsyocto will retain its open-source status and it will be further developed.

Due to the enthusiasm of commercial users, special features for industrial, scientific and automotive applications were developed and ready for the implementation in a highly optimazed closed commercial version. Partnerships as an embedded SoC-FPGA design service to fulfil these specific commercial requirements are offered. It should help, besides students with the rsyocto open-source version, commercial users, as well.

For commercial users, please visit the rsyocto embedded service provider website:

rsyocto.com