Author: Michael Köfinger, 2023, Johannes Kepler University (JKU) Linz, Austria, Institute for Integrated Circuits (IIC). This case study was performed in the context of a master thesis, which is published on the JKU ePUB repository.

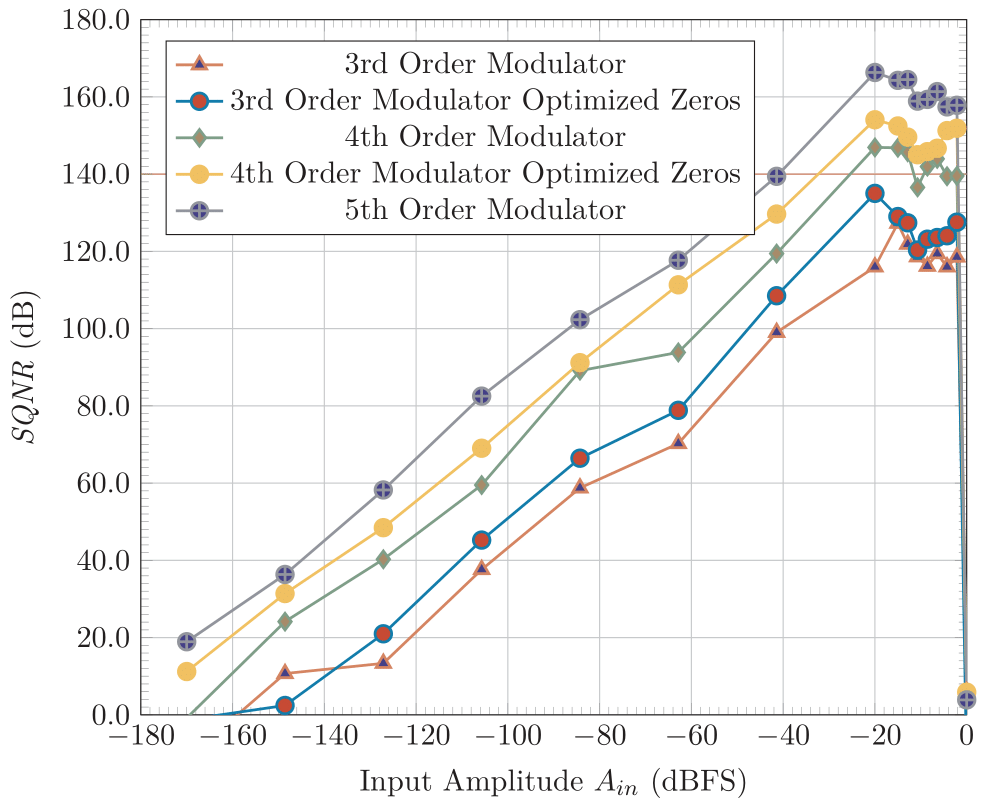

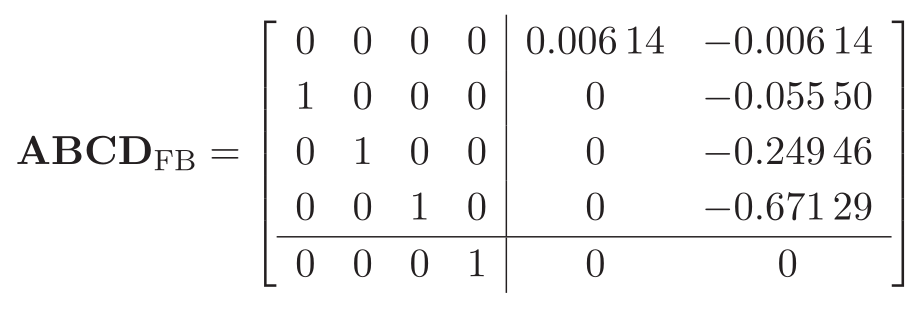

This thesis performs a case study on an ultra-low-power (ULP) Delta-Sigma analog-to-digital converter (DS-ADC) for biosignal acquisition utilizing the Institute for Integrated Circuits (IIC) Open-Source IC (OSIC) tools for the Skywater 130nm (SKY130) process development kit (PDK). The system-level simulations were based on Richard Schreier’s ∆Σ toolbox, and loop-filter non-idealities were separately modeled in MATLAB based on the difference equations of a Delta-Sigma modulator (DSM). The aim is to identify an alternative system to an existing implementation based on a cascade of a pre-amplifier and a successive approximation register analog-to-digital converter (SAR-ADC), see Fig. 1. The scope of this work was set on the DSM and the decimator was omitted throughout most parts.

Figure 1: Existing system, PRE-AMP [1] and SAR-ADC [2], and the alternative structure, a CT DS-ADC.

- Input-referred noise

$<1~\mu\mathrm{V}_\mathrm{rms}$ - Input impedance

$>100~\mathrm{M}\Omega$ - Input voltage range

$\pm260~\mathrm{mV_{peak}}$ $(\pm250~\mathrm{mV_\mathrm{dc}}\pm10~\mathrm{mV_\mathrm{signal}})$ - Power consumption

$<1~\mu \mathrm{W}$ - Signal bandwidth of

$128~\mathrm{Hz}$ - Max. oversampling ratio of

$256$ - ADC resolution (LSB)

$<0.2~\mu\mathrm{V}_\mathrm{pp}$ - Signal-to-Quantization-Noise-Ratio (SQNR) of

$>140~\mathrm{dB}$ - Signal-to-Noise-Ratio (SNR) of

$130~\mathrm{dB}$

The input-related specifications stem from the target application, which is biosignal acquisition.

The rather slow signals have a large source impedance and are in the

The fact that the DS-ADC should directly interface with the signal source, requires the implementation of a continuous-time (CT) DSM, due to its inherent anti-aliasing property.

Since circuit noise should dominate the noise floor, the SQNR was chosen

Figure 2: High-level system design exploration.

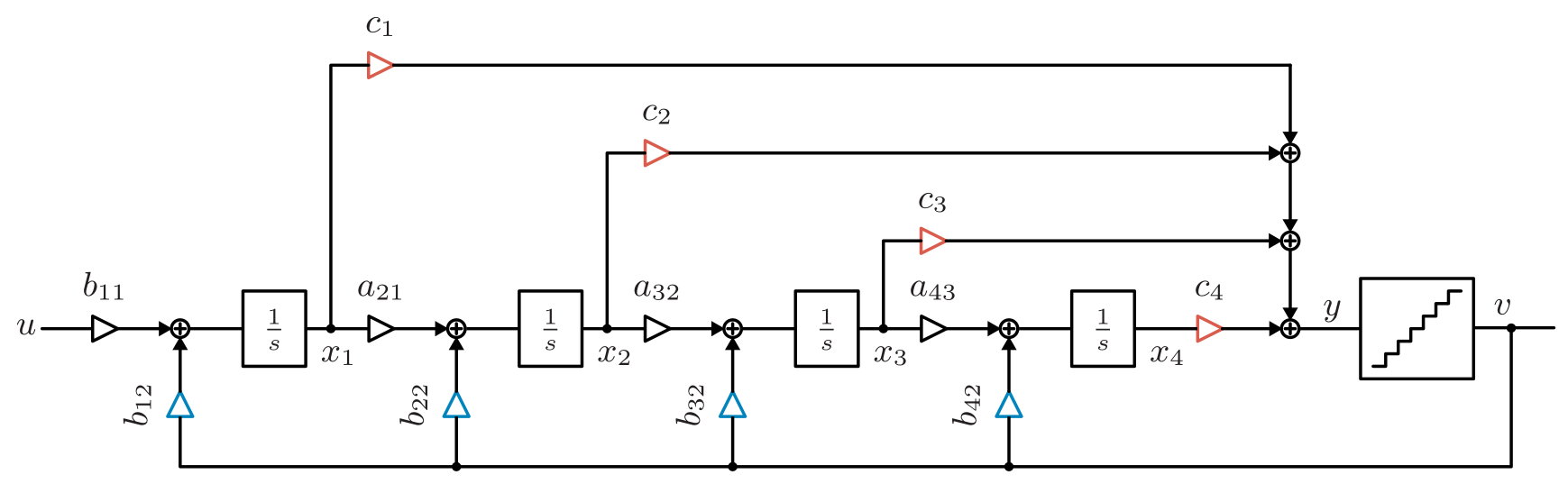

Figure 3: Block diagram of a DSM with feedback (blue) and feedforward coefficients (red).

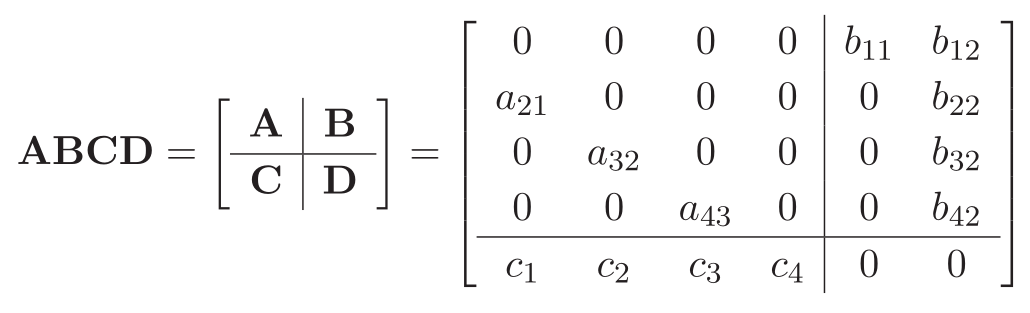

This 4th-order CT-DSM may be either implemented by a feedback (FB), or a feedforward (FF) structure. The block diagram, which depicts both structures is shown in Fig. 3. The corresponding state-space description is:

In the case of a FB modulator (blue coefficients), the ∆Σ toolbox gave the following set of coefficients:

However, the output of the integrators

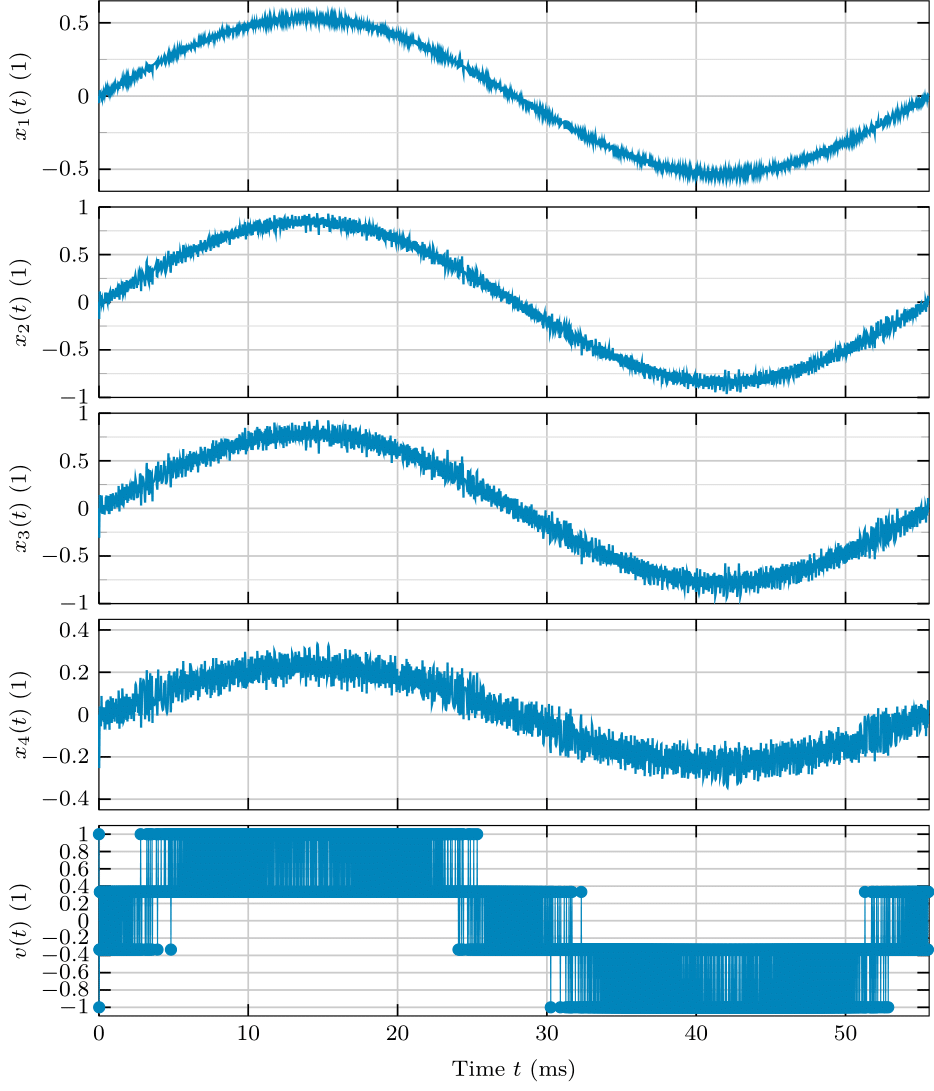

Figure 4: Internal states of the CIFB CT-DSM after dynamic range scaling, given an input tone with the maximum stable amplitude (MSA).

However, the 2-bit output sequence

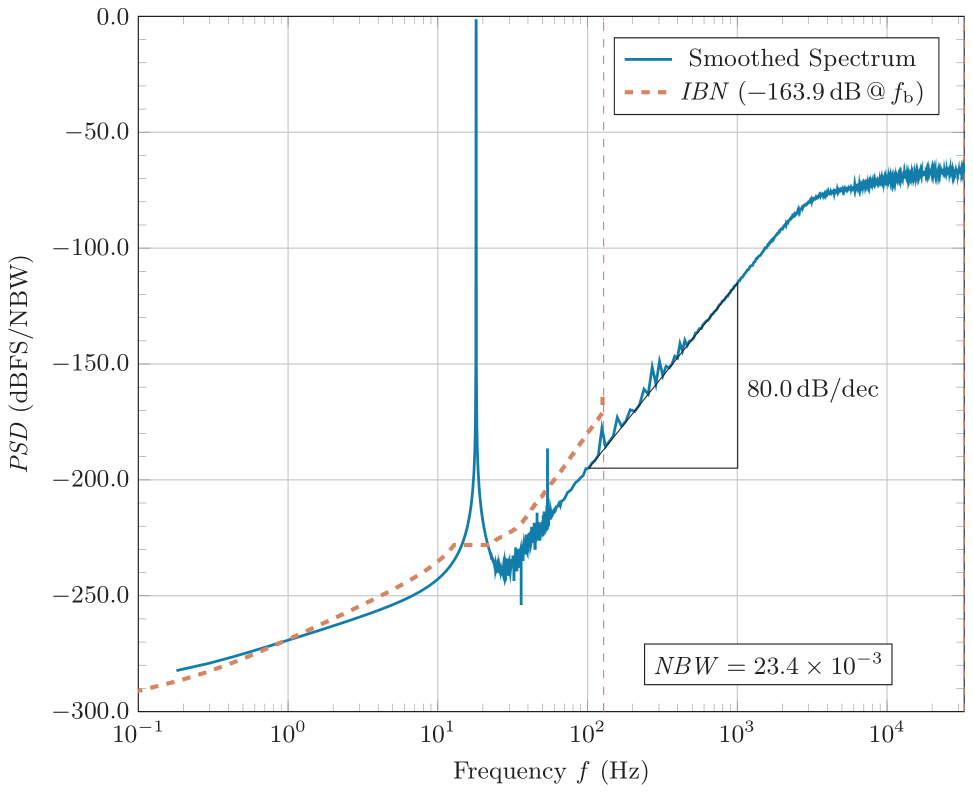

Figure 5: PSD of the output of the modulator

The most important result from system-level simulations is the need for a third-order distortion ratio

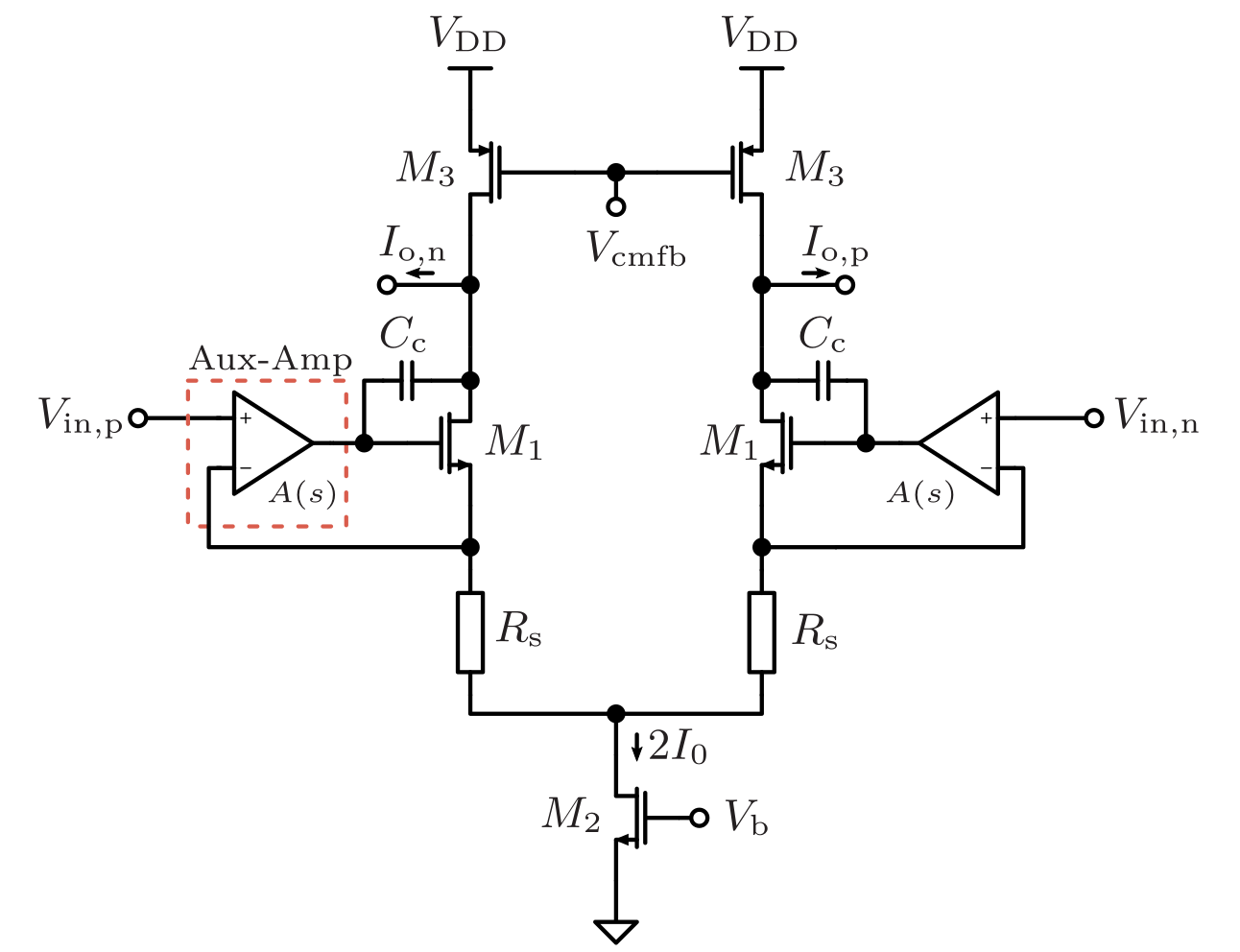

Figure 6: Schematic of the frontend transconductor.

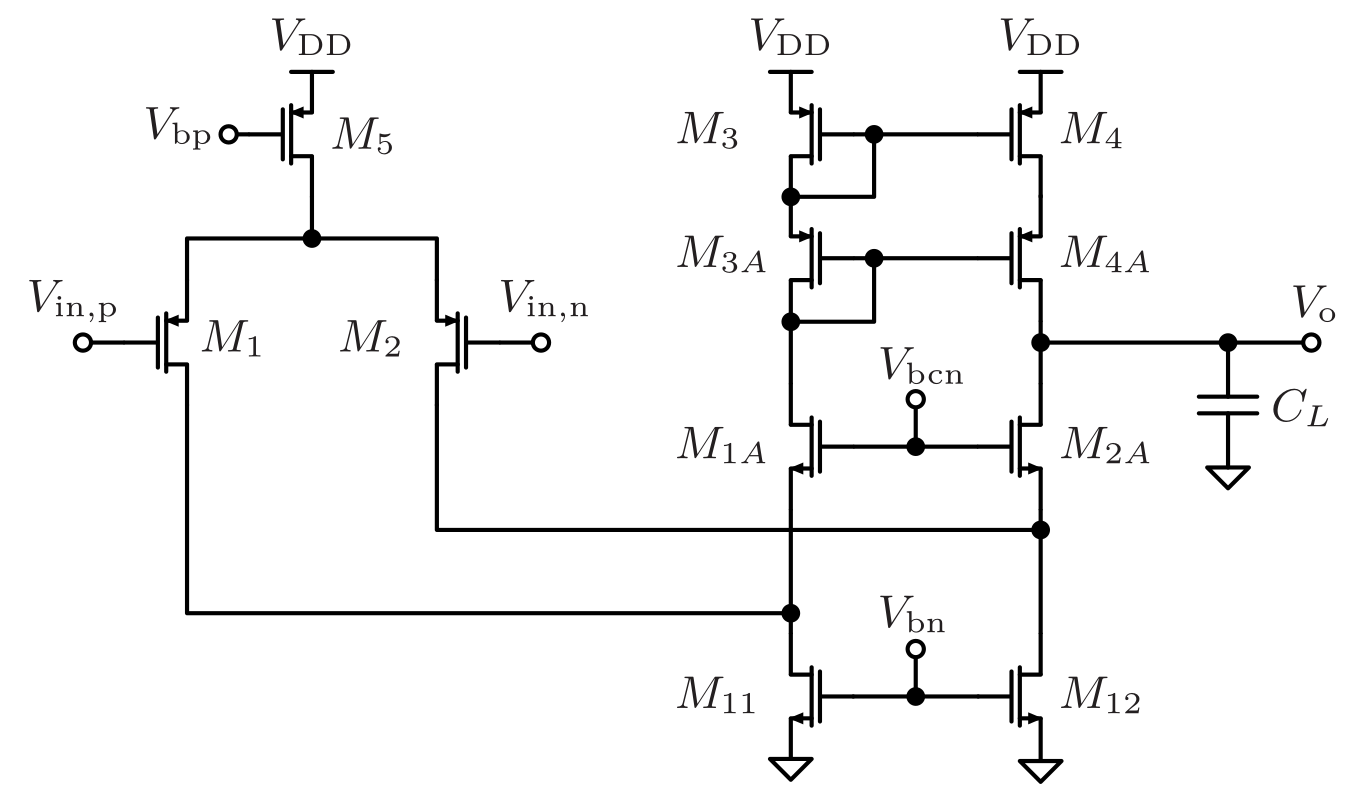

Figure 7: Schematic of the auxiliary amplifier of the frontend transconductor.

The 2-bit output

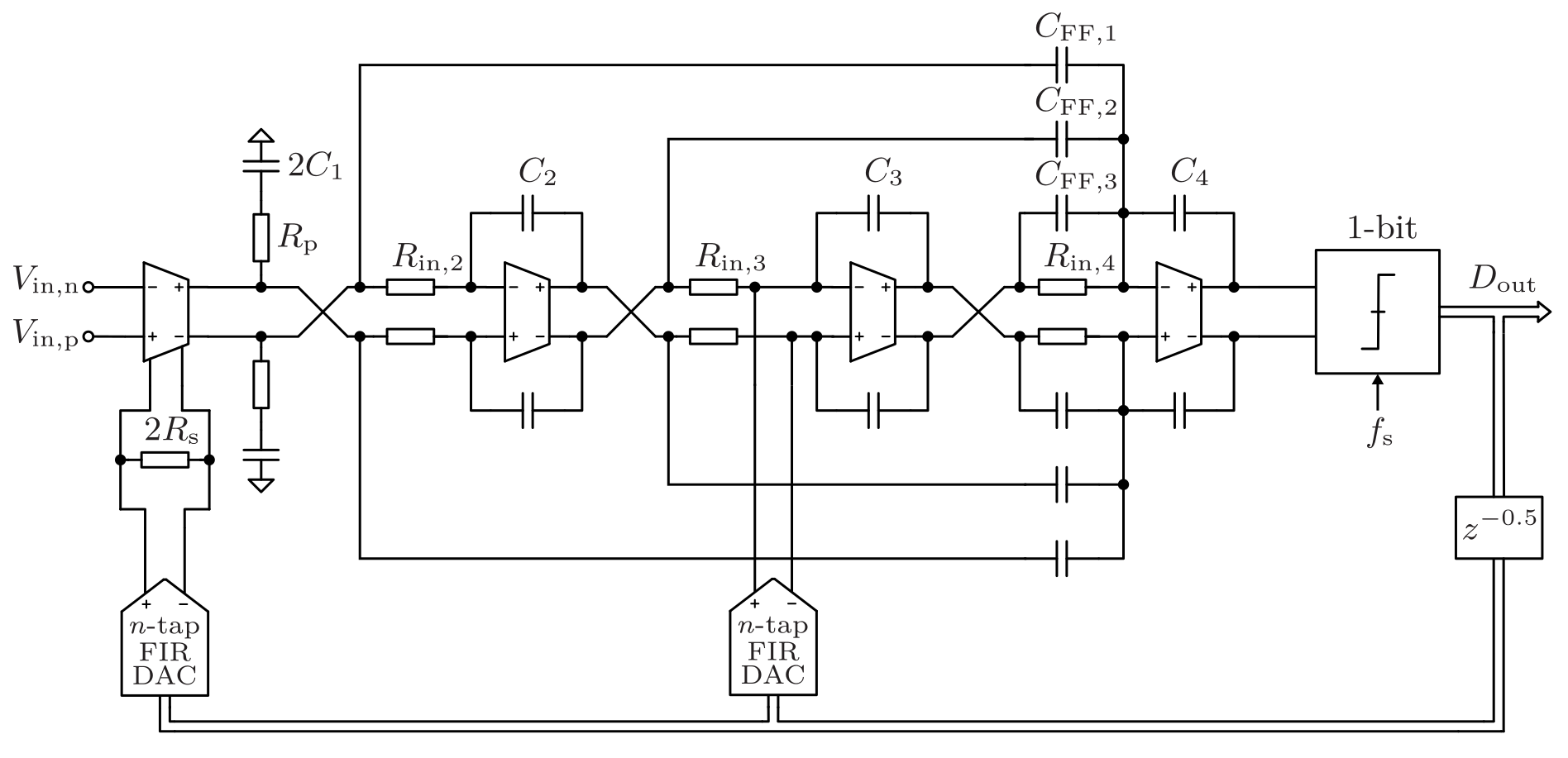

A thorough analysis in terms of several loop filter non-idealities was conducted and circuit-level design considerations in light of the findings were made. Overall, a FF loop filter is best suited in terms of noise budgets per stage, power and chip-area efficiency. The top-level schematic is given below in Fig. 8.

Figure 8: Top-level schematic of the proposed CT-DSM.

The main performance metrics of the implemented front-end transconductor are summarized along with system-level parameters and compared to two state-of-the-art neural recording ICs in Table 1.

Table 1: A comparison with state-of-the-art bidirectional neural recording ICs.

| Parameter | THIS WORK | JSSC19 [3] | JSSC20 [4] |

|---|---|---|---|

| Architecture | CT-DSM | CT-DSM | CT-DSM |

| Input Type | |||

| BW |

|||

| Technology |

|||

| Open Source Technology | yes | no | no |

| Supply |

|||

| Input Signal Range |

|||

| Target SNR |

|||

| OSR | |||

| Quantizer Type | Flash | Time-based | Time-based |

| Quantizer Bits | |||

| Noise-Shaping Order | |||

| Total Input Noise |

|||

| Eq. Input Noise Density |

|||

| Aux. Amp. W/L Input Pair |

- | ||

| Aux. Amp. W/L Casc. CS |

- | ||

| Power Consumption Input |

The main issue of the designed circuit is the large flicker noise coefficient of the SKY130 PDK.

This may be counteracted by chopper stabilization or further increasing the area of

Furthermore, increasing the OSR to reduce the required order of noise shaping may also be beneficial in terms of the tight power budget, as shown by the comparison in Table 1.

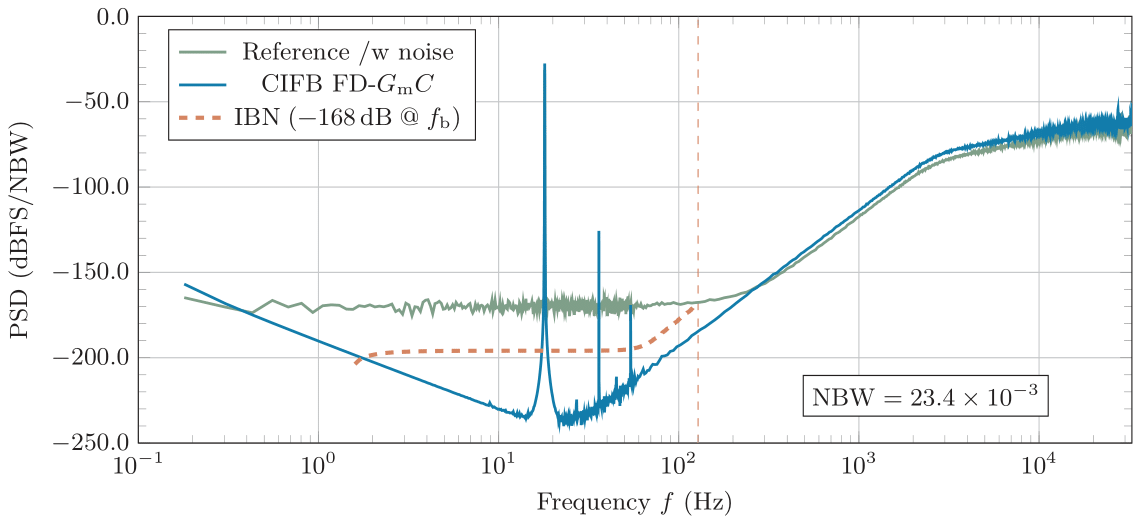

Moreover, a mixed-signal/level simulation with ideal OTA macro models was performed in Ngspice, utilizing digital XSPICE blocks. This was used to verify the calculated circuit-level components based on the state-scaled prototype coefficients, see Fig. 9.

Figure 9: PSD of mixed-signal simulation using Ngspice.

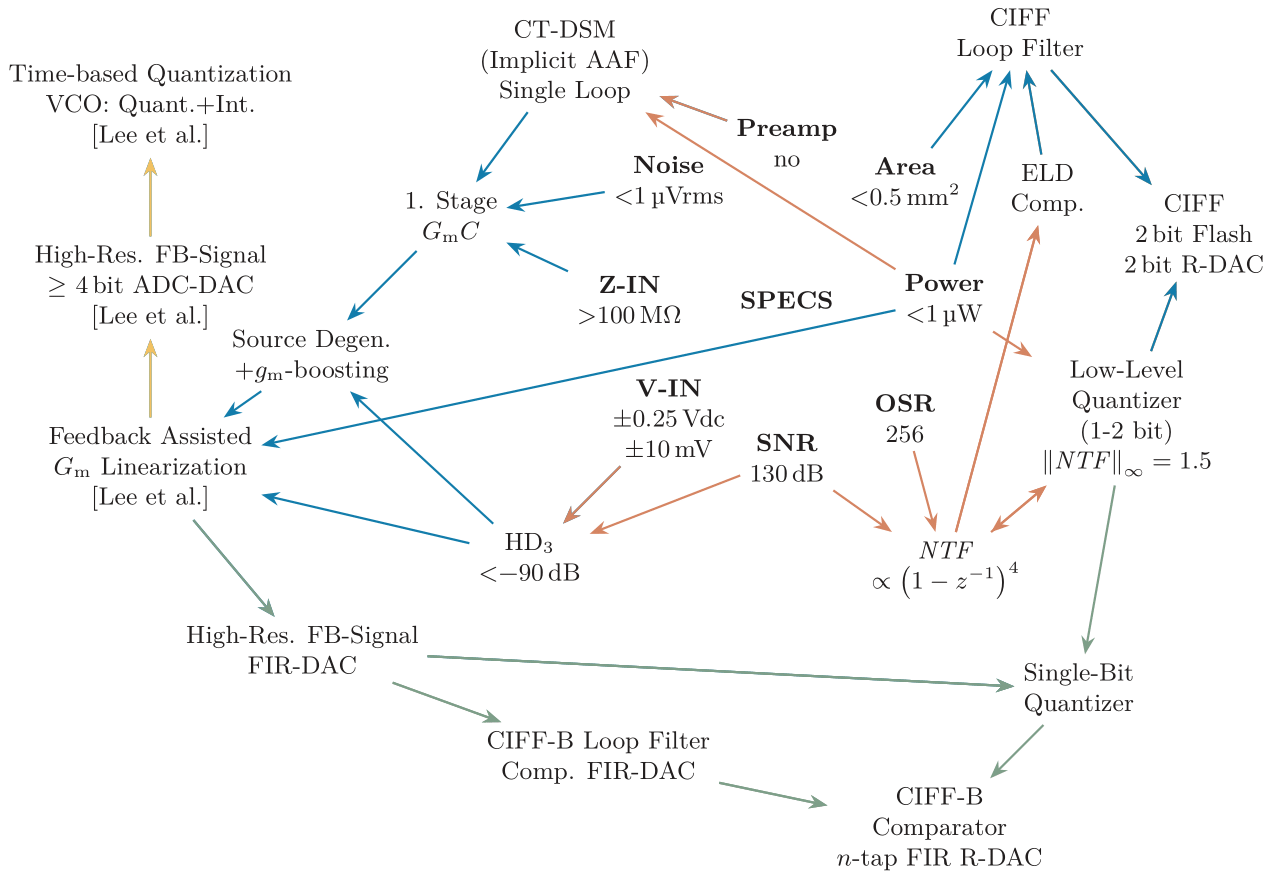

The following graph summarizes the complete design decisions of this master thesis. The most significant specification items in bold-font are the starting points.

- Red: System level

- Blue: Circuit level without improvement, coarse FB signal, conventional DSM

- Green: Circuit level with proposed front-end, FIR-DAC, single-bit quantizer

- Yellow: Circuit level alternative [4], high-level time-based quantizer

Figure 10: Summary of all major design decisions.

Due to the time limitation of this master thesis, several aspects could not be addressed in full detail:

- Excess loop delay compensation

- Simulation and implementation of the FIR-DACs

- Circuit design and layout of stages 2 to 4

- Circuit design and layout of the quantizer

- Further improvements and layout of the front-end transconductor

- Verification of the ''Feedback Assisted

$G_\mathrm{m}$ Linearization'' technique [4] - Implementation of the decimator

Moreover, the influence of a larger OSR, which would reduce the loop filter order, should be reassessed. However, the system clock was fixed in the context of this work, which required a 4th order CT-DSM.

[1] S. Schmickl, T. Schumacher, P. Fath, T. Faseth and H. Pretl, "A 350-nW Low-Noise Amplifier With Reduced Flicker-Noise for Bio-Signal Acquisition," 2020 Austrochip Workshop on Microelectronics (Austrochip), Vienna, Austria, 2020, pp. 9-12, doi: 10.1109/Austrochip51129.2020.9232981.

[2] S. Schmickl, T. Faseth and H. Pretl, "An Untrimmed 14-bit Non-Binary SAR-ADC Using 0.37 fF-Capacitors in 180 nm for 1.1 µW at 4 kS/s," 2020 27th IEEE International Conference on Electronics, Circuits and Systems (ICECS), Glasgow, UK, 2020, pp. 1-4, doi: 10.1109/ICECS49266.2020.9294971.

[3] H. Jeon, J. -S. Bang, Y. Jung, I. Choi and M. Je, "A High DR, DC-Coupled, Time-Based Neural-Recording IC With Degeneration R-DAC for Bidirectional Neural Interface," in IEEE Journal of Solid-State Circuits, vol. 54, no. 10, pp. 2658-2670, Oct. 2019, doi: 10.1109/JSSC.2019.2930903.

[4] C. Lee et al., "A 6.5-μW 10-kHz BW 80.4-dB SNDR Gm-C-Based CT ∆∑ Modulator With a Feedback-Assisted Gm Linearization for Artifact-Tolerant Neural Recording," in IEEE Journal of Solid-State Circuits, vol. 55, no. 11, pp. 2889-2901, Nov. 2020, doi: 10.1109/JSSC.2020.3018478.

![Existing system, PRE-AMP [1] and SAR-ADC [2], and the alternative structure, a CT DS-ADC.](https://raw.githubusercontent.com/michaelk99/SKY130_CT-DSM/master/doc/fig/block_diag_all.png)