Fedar F1

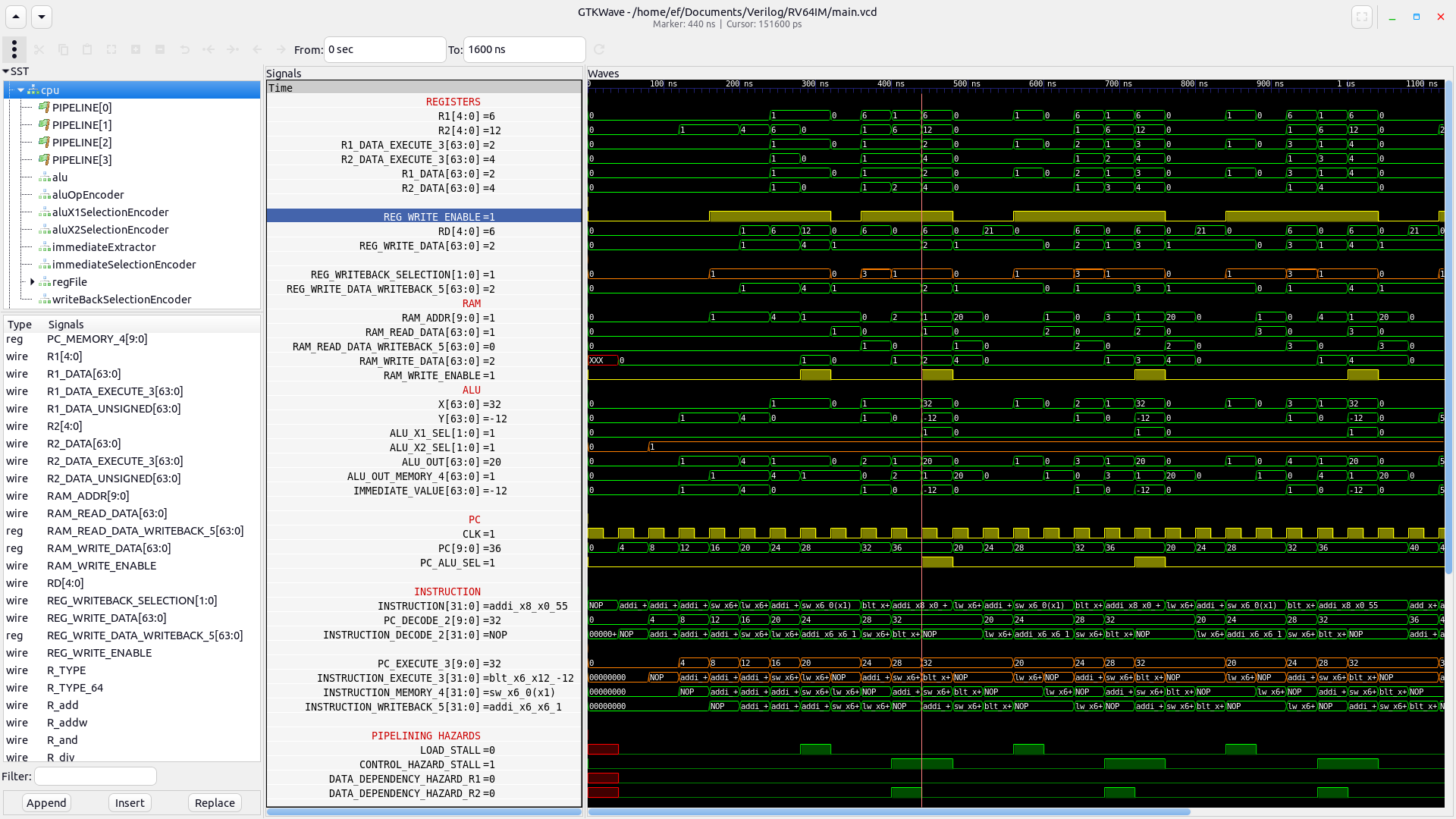

Fedar F1 is a 5-Stage Pipelined (Fetch|Decode|Execute|Memory|Writeback) RV64IM RISC-V Core written fully in Verilog.

How to compile?

- Open a terminal in

testbenchfolder. - Run:

run_tests.sh.

- The script automatically compile and create files under the

testbench/output/folder. - And will create

.vcdfiles under thetestbench/vcdfolder.

- Done!

Compilation requires iverilog verilog compiler.

You can install iverilog on Debian based distros (like Pardus GNU/Linux or Ubuntu) with this command:

sudo apt install iverilog

If you don't want to compile it again, precompiled

.vcdfiles are available under thetestbench/vcd.

How to open .vcd files?

- Use GTKWave.

You can install GTKWave on Debian based distros (like Pardus GNU/Linux or Ubuntu) with this command:

sudo apt install gtkwave

Then double click the files or open with terminal command: gtkwave file.vcd.