-

Learning how to use JTAG functionality of SpinalHDL.

-

Also written a small Python code with PyFtdi for FTDI FT232H breakout.

-

Follow this site and install tinyprog.

-

Also follow this site and install required software SpinalHDL.

-

Install Python3 and PyFtdi.

-

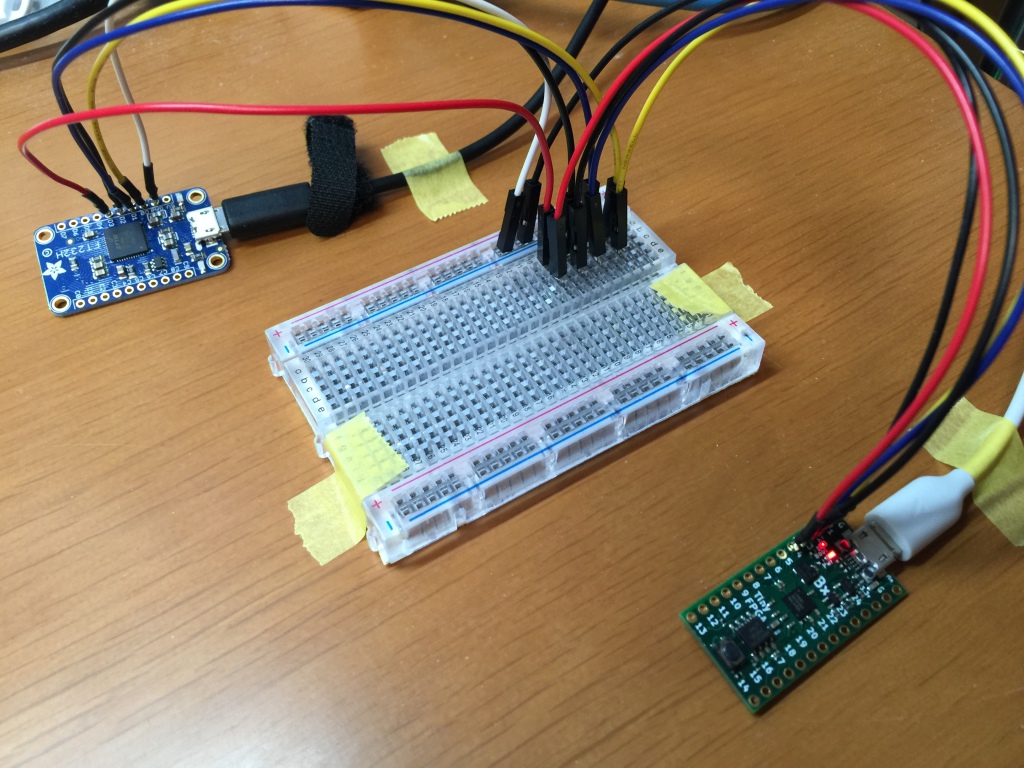

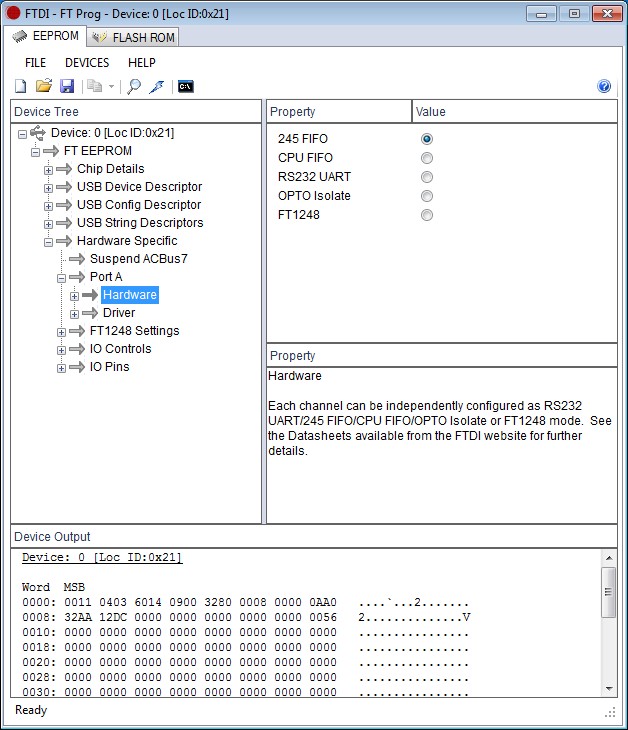

You need an FT232H or FT2232H breakout. I chose Adafruit FT232H Breakout. You should carefully disable UART mode to configure JTAG TDO pin (D2) as input. ("245 FIFO" mode is my recommendation. Please find the following screen capture.) Regarding EEPROM programming on the breakout by FTDI FT_PROG, this page is also helpful.

First, connect your TinyFPGA to a USB port.

$ make uploadDone.

FPGA side: Please find this PCF file.

FT232H side:

- ADBUS0 (D0): JTAG TCK (output from FT232H)

- ADBUS1 (D1): JTAG TDI (output from FT232H)

- ADBUS2 (D2): JTAG TDO (input to FT232H)

- ADBUS3 (D3): JTAG TMS (output from FT232H)

$ python3 scripts/jtag.pyInfo: Device utilisation:

Info: ICESTORM_LC: 141/ 7680 1%

Info: ICESTORM_RAM: 0/ 32 0%

Info: SB_IO: 7/ 256 2%

Info: SB_GB: 4/ 8 50%

Info: ICESTORM_PLL: 0/ 2 0%

Info: SB_WARMBOOT: 0/ 1 0%

$ icetime -tmd lp8k jtagpwm_tinyfpga_bx.asc

Total number of logic levels: 4

Total path delay: 9.60 ns (104.17 MHz)