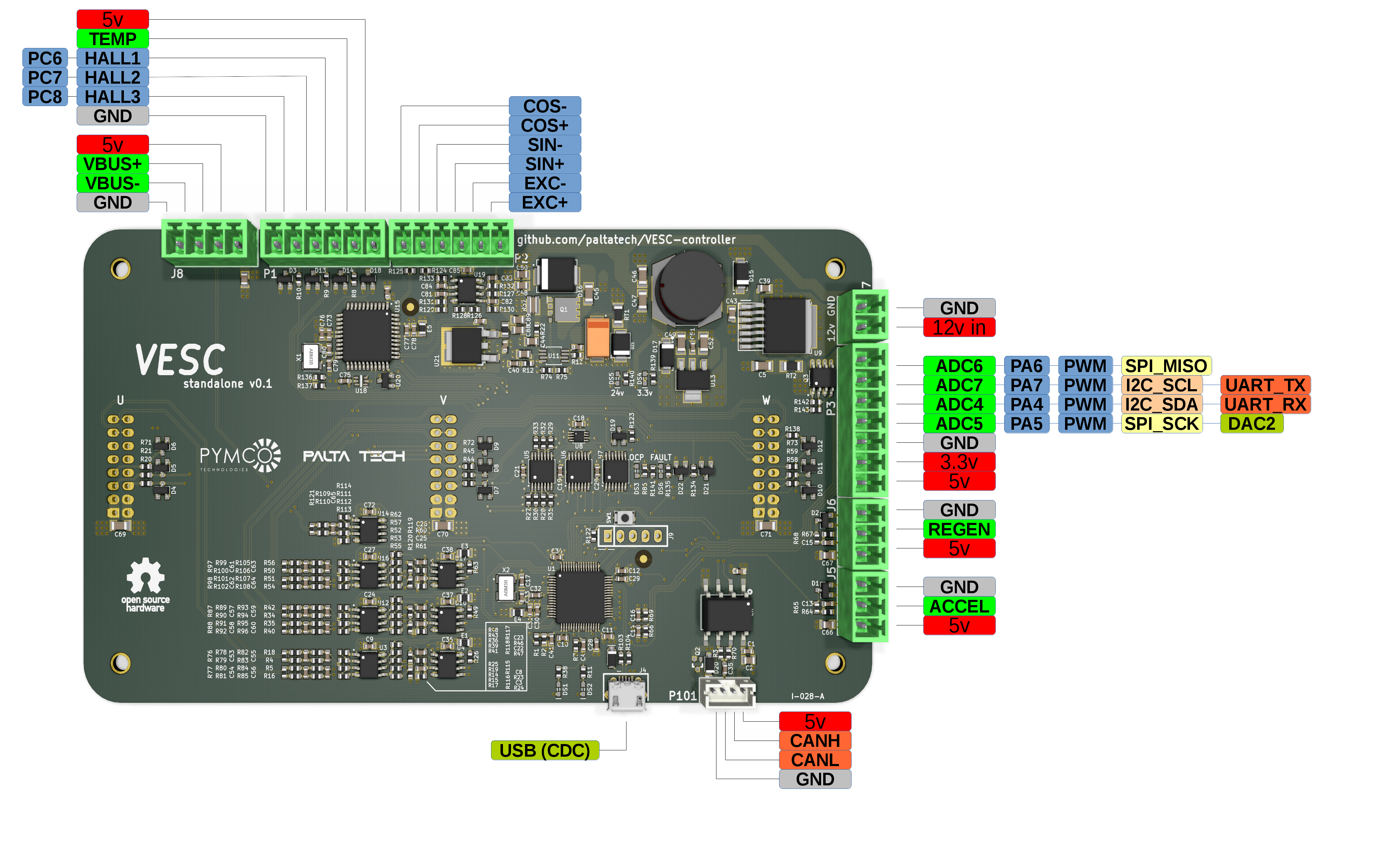

This is the hardware repository of a 3 phase inverter brain, UNTESTED but designed with the following specs in mind:

- Compatible with VESC firmware and software tools

- Embedded security features (overcurrent protection, pwm overlap elimination, etc)

The core of the system is a 32 bit ARM Cortex M4 MCU (STM32F405)

- CAN bus for control, configuration and monitoring

- USB for light usage, firmware upload/upgrade and configuration.

- UART, I2C and ADCs and GPIOs available

- Bus Voltage (differential)

- Phase current (differential)

- Phase voltage (differential)

- Gate driver fault

- Power_good from gate driver

- Motor temperature

- Hall/encoder

- Resolver

- PWM high/low

- dynamic gate drive current (pwm)

- 24v power

You can also check the layout here

Made open source with KiCAD, an open source EDA tool.

This documentation describes Open Hardware and is licensed under the CERN OHL v. 1.2