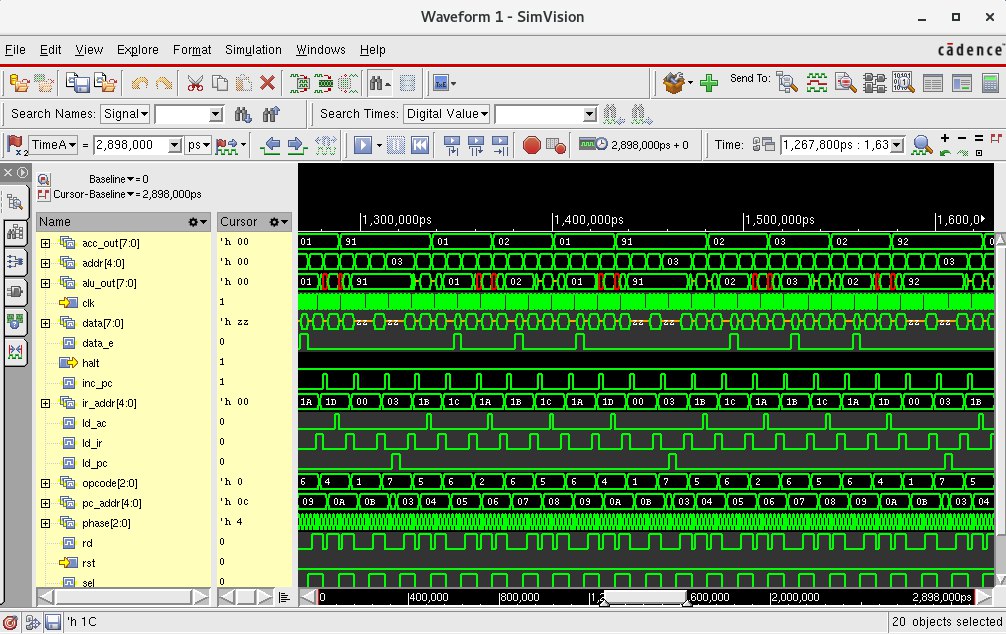

Cadence Training Services learning maps provide a comprehensive visual overview of the learning opportunities for Cadence customers. They provide recommended course flows as well as tool experience and knowledge levels to guide students through a complete learning plan.

This repository is for documentation purposes, the documents were produced by me or are documents obtained directly from the Cadence website. If you have any issues, please contact me and I'll remove them immediately.

git submodule update --init

- Verilog Language and Application v27.0

- SystemVerilog for Design and Verification v21.10

- Essential SystemVerilog for UVM (SOON)

- Essential SystemVerilog for UVM (SOON)

- SystemVerilog Assertions (SOON)

- Xcelium™ Simulator (SOON)

Contributions are what make the open source community an amazing place to learn, inspire and create. Any contributions you make are very welcome!

If you want to help by suggesting text and spelling corrections or some code tweaks, you can open a pull request and I'll love it!!! 😍

If you have a quick contribution that doesn't involve code, content or you want to report a problem without having to propose changes click here to create an issue.

- Fork this repository.

- Create a branch:

git checkout -b newResource. - Add your edits for the next commit:

git add . - Make your changes and confirm them:

git commit -m 'Message from your contribution'. - Specify a new upstream remote repository that will be synchronized with the fork:

git remote add upstream git@github.com:<USER_NAME>/<REPOSITOR_NAME>.git - Send to the original branch:

git push --set-upstream origin newResource - Create the pull request using the link that appears in the terminal.

We would like to thank the following people who contributed to this project:

|

Maurício Taffarel |