MiSTer Laggy is a display latency tester for use with the MiSTer FPGA system. It consists of a core that runs on the MiSTer DE-10 and a light sensor that connects to the MiSTer's User Port. It operates on the same principle as the Time Sleuth but takes advantage of an existing platform to generate the video signal and capture the measurements.

- Copy the latest core from the

releases/directory to your MiSTer - Connect the MiSTer Laggy sensor to the User Port with a USB A-C cable

- Launch the MiSTer Laggy core

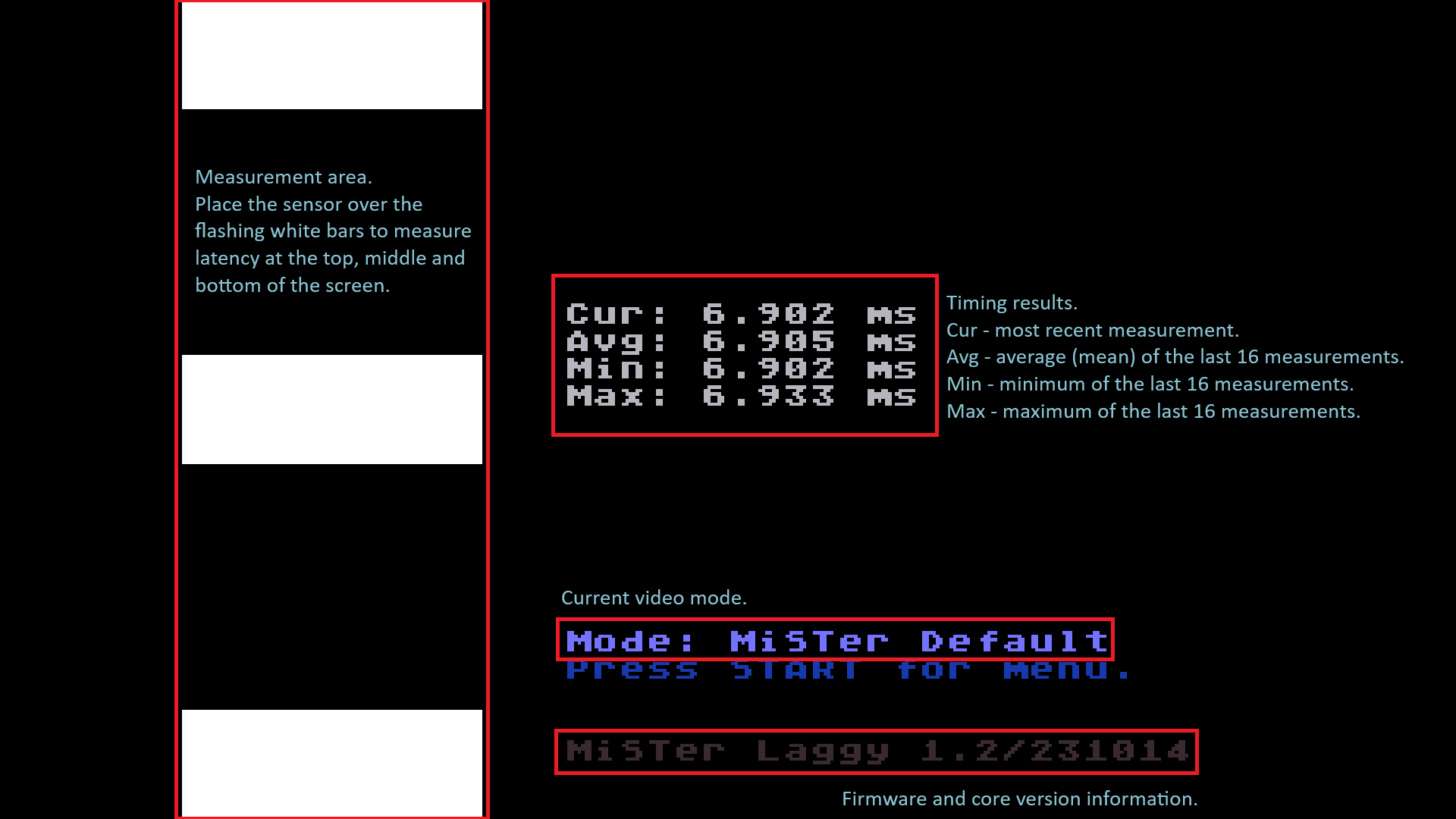

The system works by flashing a test pattern on the screen and measuring how long it takes for that pattern to be seen by the sensor. The measured latency is show in the center of the screen, along with the average, min and max measures. There are three areas in the test pattern why you can place the sensor, so you can measure latency at the top, middle and bottom of the screen.

The system works by flashing a test pattern on the screen and measuring how long it takes for that pattern to be seen by the sensor. The measured latency is show in the center of the screen, along with the average, min and max measures. There are three areas in the test pattern why you can place the sensor, so you can measure latency at the top, middle and bottom of the screen.

On startup or after a reset, the core uses whatever video mode and vsync_adjust settings you have configured in your MiSTer INI file. When running in this mode it will display Mode: MiSTer Default on the main screen. You can change the current video mode in the Video Config menu which you access by pressing the START button on your controller.

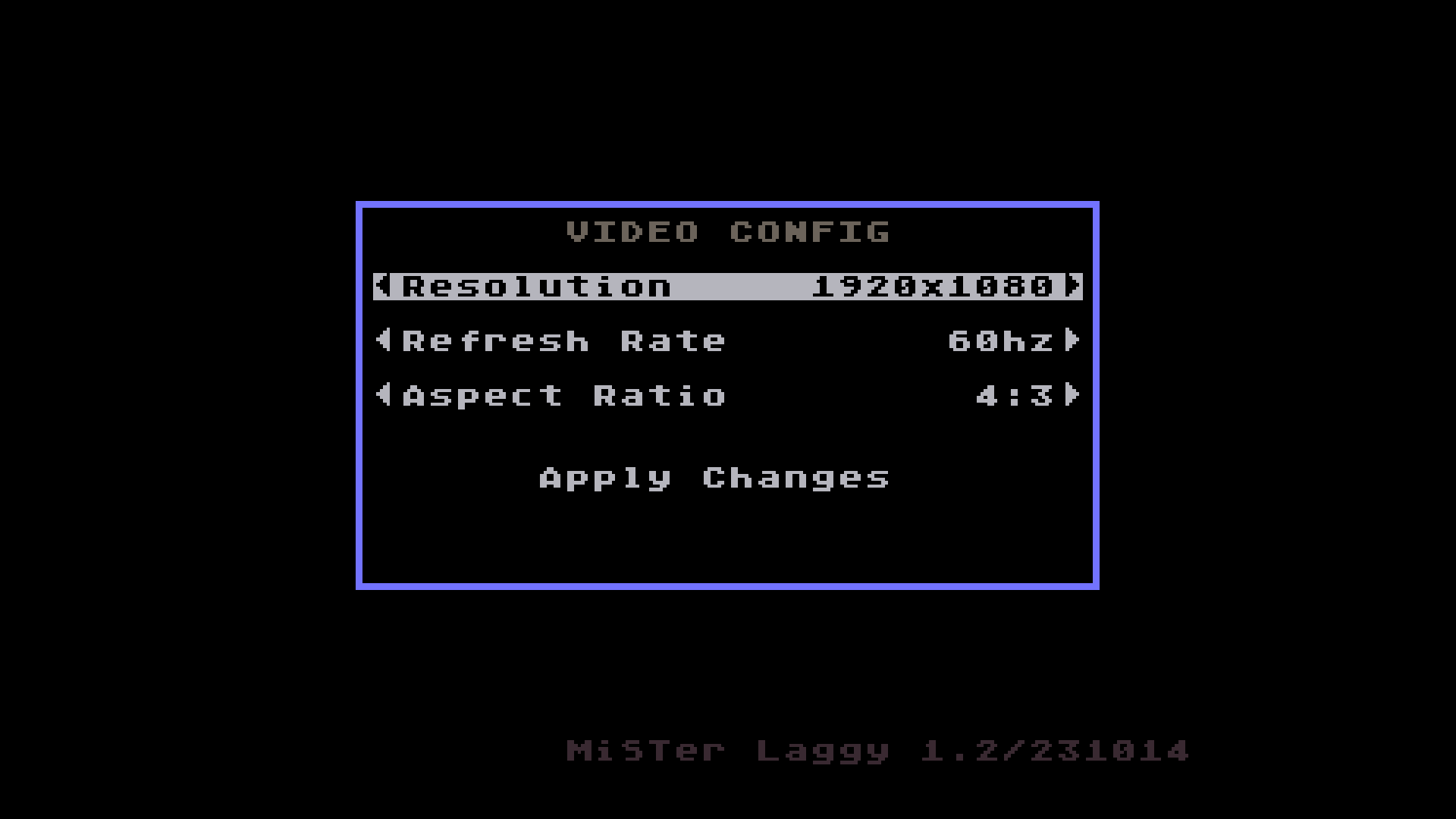

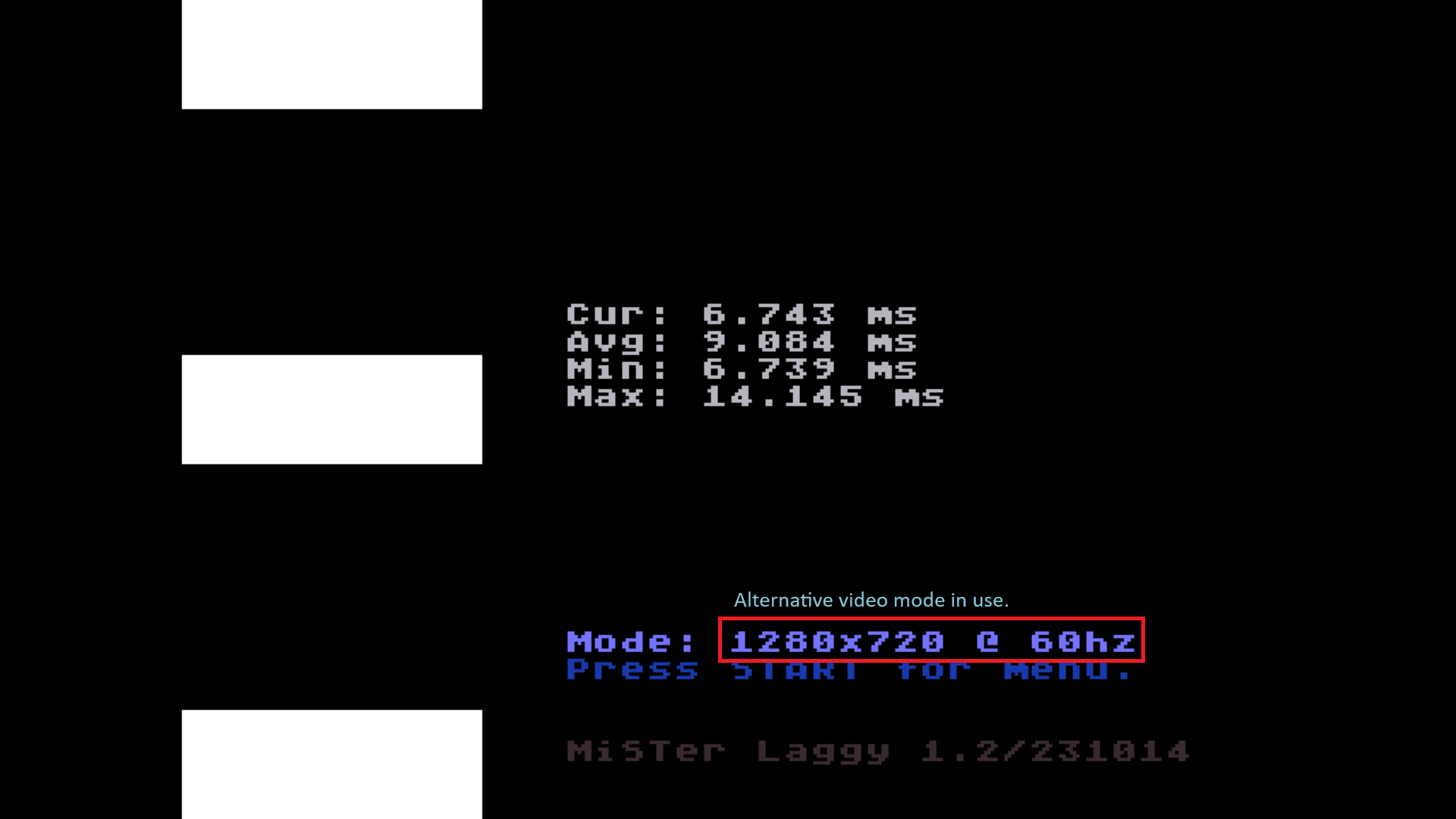

In the Video Config menu you can select between several resolutions and refresh rates. Up/Down on your controller selects between the options while Left/Right adjusts each value. You can press B or Start to back out of the menu at any time. To apply the changes and switch to the mode you have selected, highlight the Apply Changes option and press A. The core will switch to the new video mode and return to the main screen. The new mode will now be displayed in the Mode: area.

It's possible that your display does not support the display mode that you have selected. If that happens you can just reset the core by pressing the User button on your IO board or just power cycle your MiSTer. None of the changes set in the Video Config menu are permanent.

MiSTer Laggy starts counting latency from the moment the vertical blank ends. Assuming there is no overscan or other scaling enabled on your display, this will be the where the first visible line in drawn on your screen. With HDMI output on MiSTer there are two different vertical blanks, the vertical blank created by the core itself and the vertical blank created by the scaler. The scaler vertical blank occurs after the cores vertical blank, how long after depends on the vsync_adjust setting you are using in your INI.

When the MiSTer Laggy core starts up and is in the MiSTer Default video mode, it uses the end of the vertical blank from the core as the start of the measurement. This means that any latency introduced by MiSTer's ASCAL scaler will also be measured. You could, for instance, experiment with different vsync_adjust settings and see how they impact the total latency.

When you switch modes in the Video Config menu, the core will start using the end of the HDMI vertical blank, which is generated by the scaler, as the start of the measurement period. This means only the display latency will be measured, and any additional time spent in the MiSTers scaler will not be included.

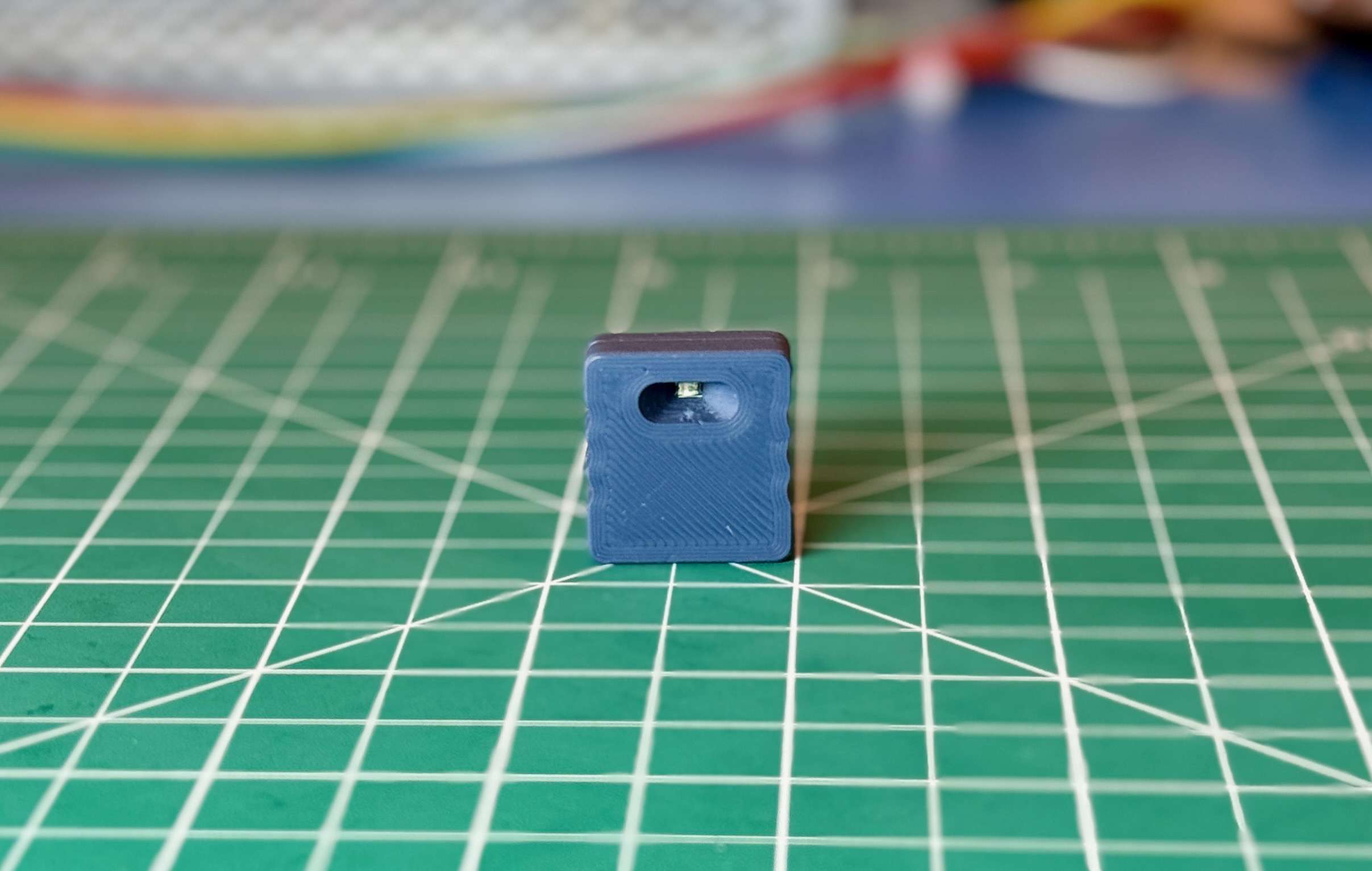

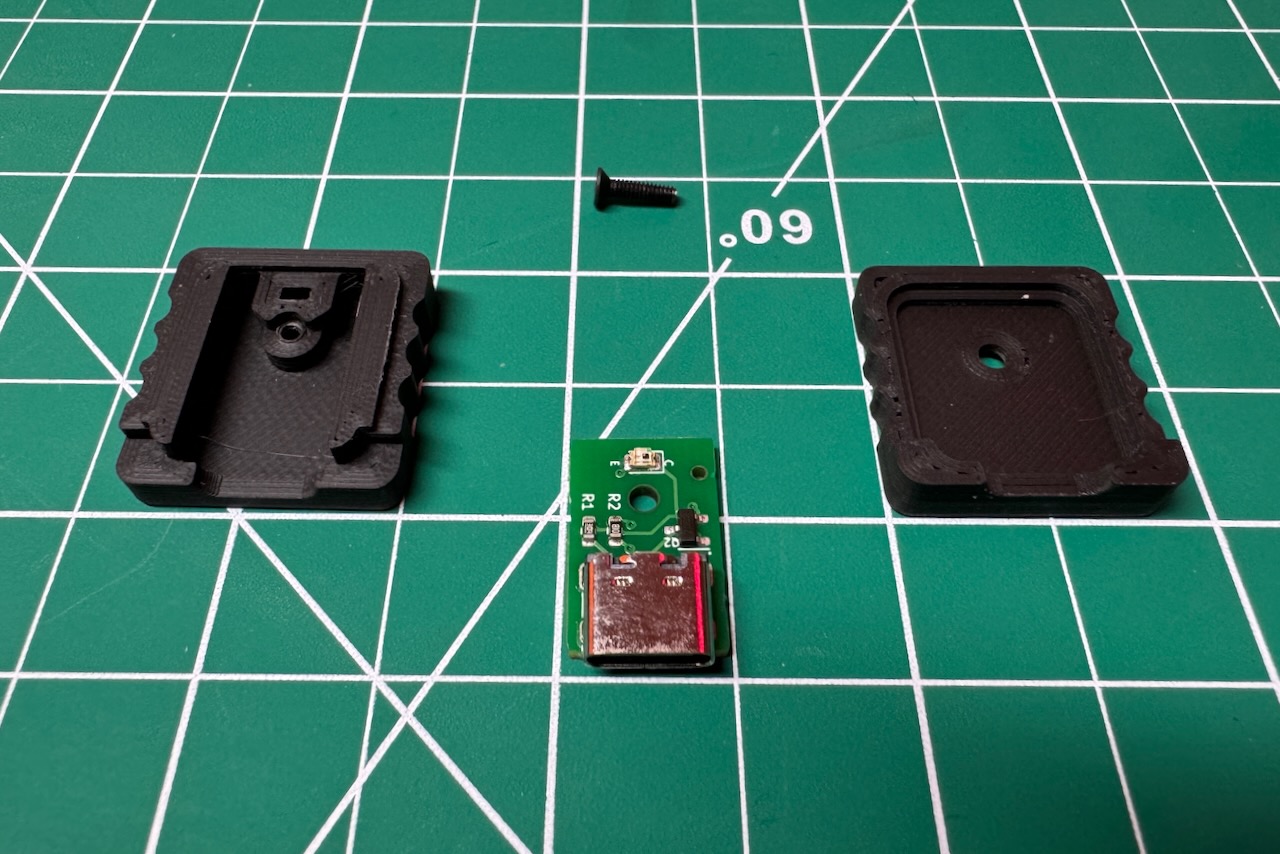

The MiSTer Laggy hardware is very simple. It consists of a small PCB with a photo transistor alongside a few components to allow it to interface with the user port, and a 3D printed case. The case is designed to prevent any external light from reaching the sensor. It snaps together tightly and is secured with a M2x8 flat head screw. The PCB is all surface mounted components and uses a compact USB-C connector.

The MiSTer Laggy hardware is very simple. It consists of a small PCB with a photo transistor alongside a few components to allow it to interface with the user port, and a 3D printed case. The case is designed to prevent any external light from reaching the sensor. It snaps together tightly and is secured with a M2x8 flat head screw. The PCB is all surface mounted components and uses a compact USB-C connector.

The hardware/ directory contains KiCAD project files for the PCB along with STEP and STL files for the case.