| Introduction | 1. Connecting to your F1 instance | 2. Experiencing F1 acceleration | 3. Developing F1 applications | 4. Wrapping-up |

Welcome to the AWS F1 Xilinx Developer Lab. During this session you will gain hands-on experience with AWS F1 and learn how to develop accelerated applications using the AWS F1 OpenCL flow and the Xilinx SDAccel development environment.

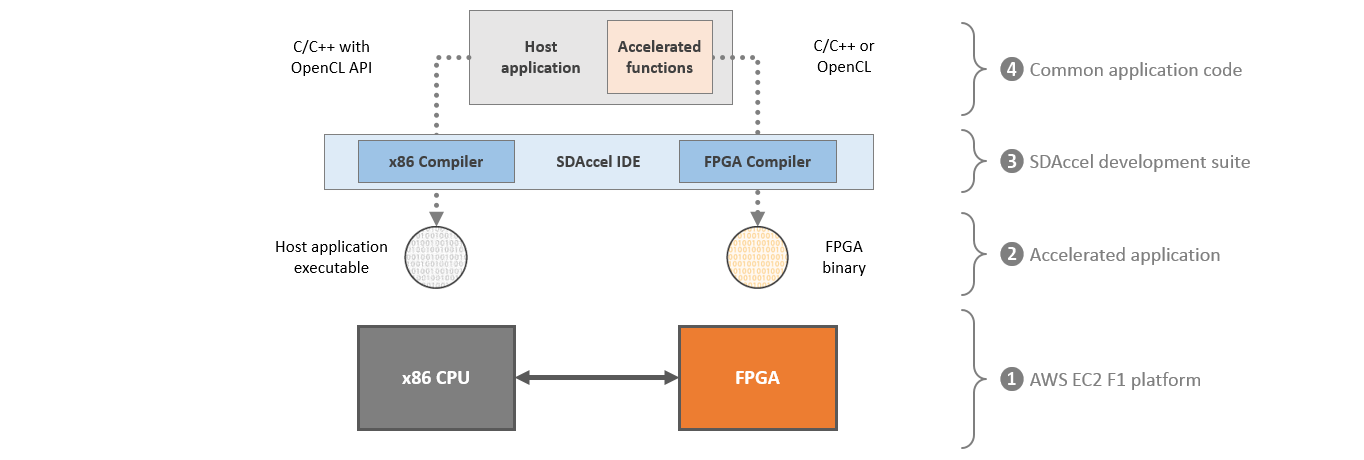

The architecture of the AWS F1 platform and the SDAccel development flow are pictured below:

- Amazon EC2 F1 is a compute instance combining x86 CPUs with Xilinx FPGAs. The FPGAs are programmed with custom hardware accelerators which can accelerate complex workloads up to 30x when compared with servers that use CPUs alone.

- An F1 application consists of an x86 executable for the host application and an FPGA binary (also referred to as Amazon FPGA Image or AFI) for the custom hardware accelerators. Communication between the host application and the accelerators are automatically managed by the OpenCL runtime.

- SDAccel is the development environment used to create F1 applications. It comes with a fully fledged IDE, x86 and FPGA compilers, profiling and debugging tools.

- The host application is written in C or C++ and uses the OpenCL API to interact with the accelerated functions. The accelerated functions (also referred to as kernels) can be written in C, C++, OpenCL or even RTL.

This developer lab is divided in 4 modules. It is recommended to complete each module before proceeding to the next.

- Connecting to your F1 instance

You will start a pre-configured EC2 F1 instance and connect to it using a remote desktop client. Once connected, you will download the lab files and confirm you can execute a simple application on F1. - Experiencing F1 acceleration

AWS F1 instances are ideal to accelerate complex workloads. In this module you will experience the potential of F1 by using FFmpeg to run both a software implementation and an F1-optimized implementation of an H.265/HEVC encoder. - Developing and optimizing F1 applications with SDAccel

You will use the SDAccel development environment to create, profile and optimize an F1 accelerator. The lab focuses on the Inverse Discrete Cosine Transform (IDCT), a compute intensive function used at the heart of all video codecs. - Wrap-up and next steps

You will to close your remote desktop session, stop your F1 instance and explore next steps to continue your F1 experience after the Xilinx Developer Lab.

Since building FPGA binaries is not instantaneous, all the modules of this Developer Lab will use precompiled FPGA binaries.

Start the next module: 1. Connecting to your F1 instance