Verilog Output Weaver Generator allows you to generate the output wave from a digital circuit using a Verilog¹ file and the input states described on a "wave in" file. If you didn't get it: check the example below! :)

¹ In case you don't know: Verilog is a hardware description language that allow us to represent digital circuits.

Try it:

python3 compiler.py [VERILOG FILE] [WAVE IN FILE]

If you have no clue about what I'm talking about, please let me give you an example:

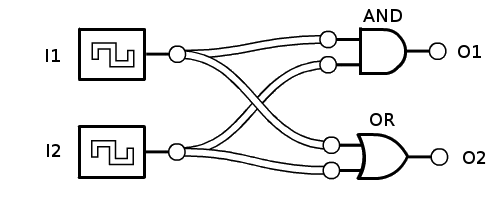

Let's use this one:

and this is the respective Verilog description file (let's name it verilog.v):

module Exemplo(I1, I2, O1, O2);

input I1, I2;

output O1, O2;

and AND(O1, I1, I2);

or OR(O2, I1, I2);

endmodule

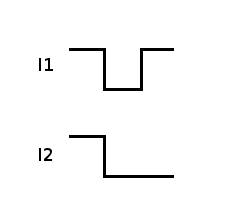

Input waves:

We can represent the waves above in a python file (let's name it wave_in.py):

wave_in_base = [

['I1', [1, 0, 1]],

['I2', [1, 0, 0]]

]

python3 compiler.py verilog.v wave_in.py

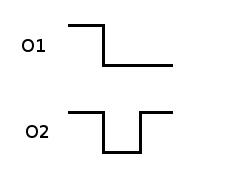

and we will get:

{'O2': [1, 0, 1], 'O1': [1, 0, 0]}

that is the same as: