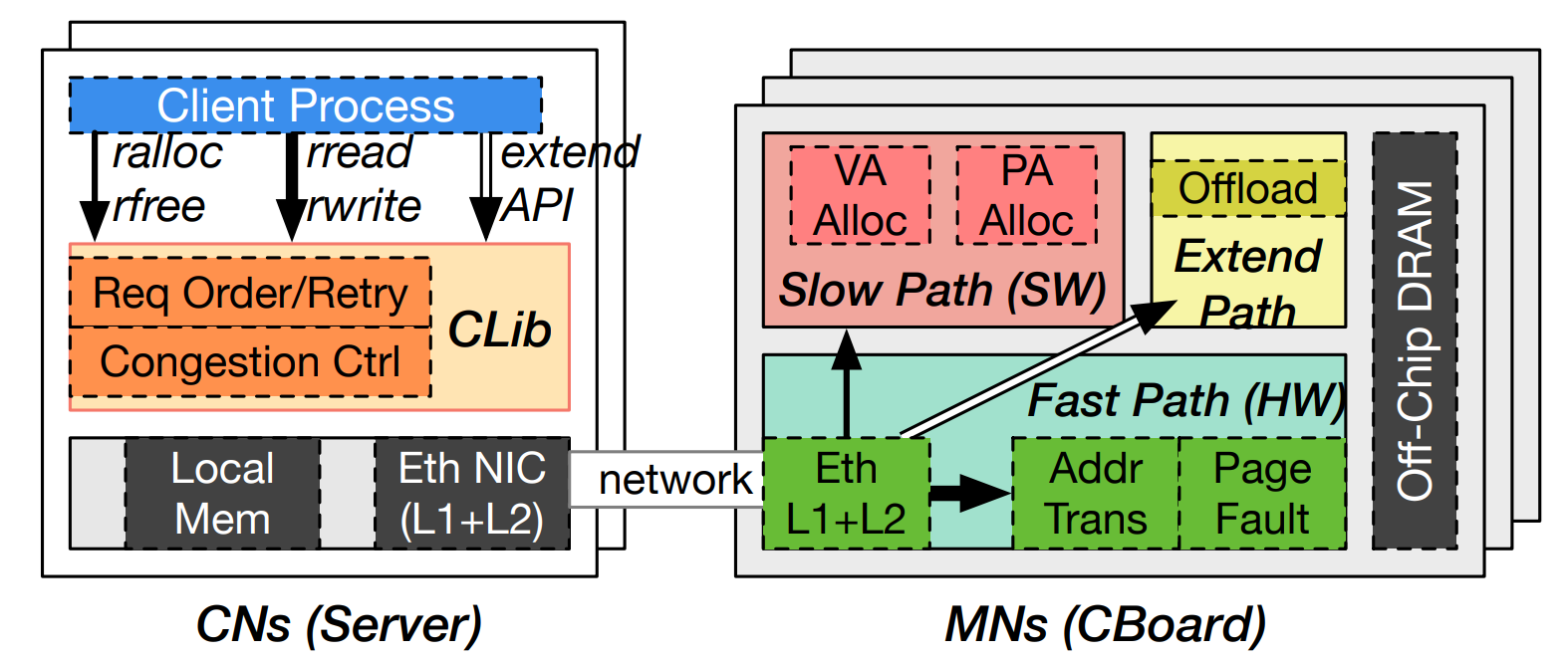

Clio is a disaggregated memory system that virtualizes, protects, and manages disaggregated memory at hardware-based memory nodes. More details in our ASPLOS'22 paper here.

This repo contains Clio's FPGA hardware design, host side software, and testing program.

The Clio hardware includes a new virtual memory system, a customized network system, and a framework for computation offloading

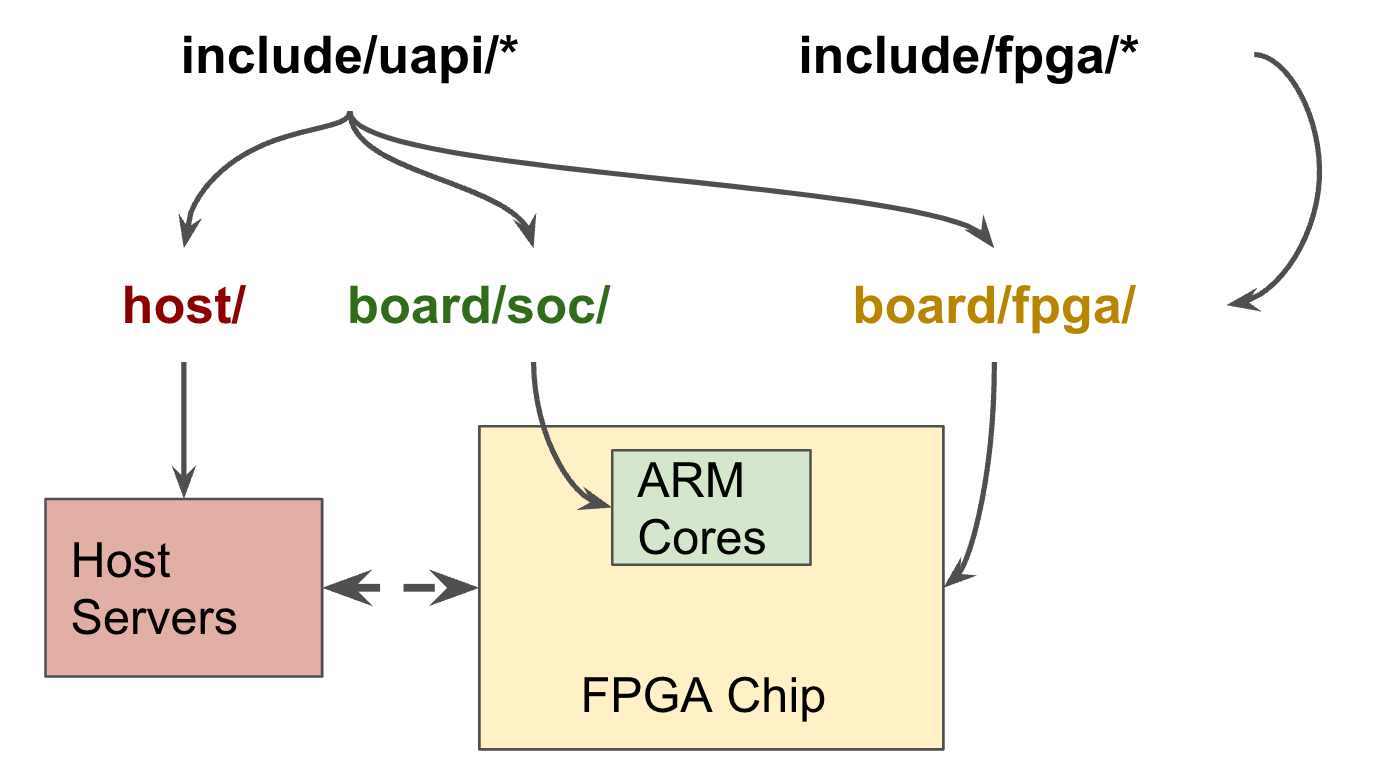

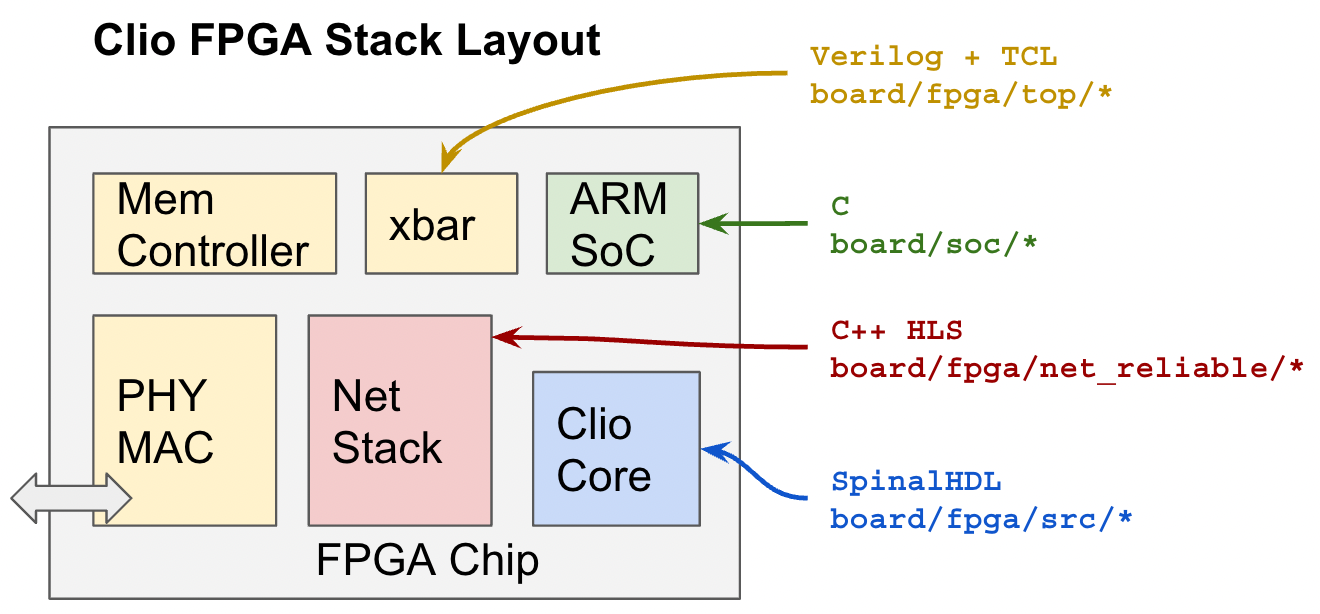

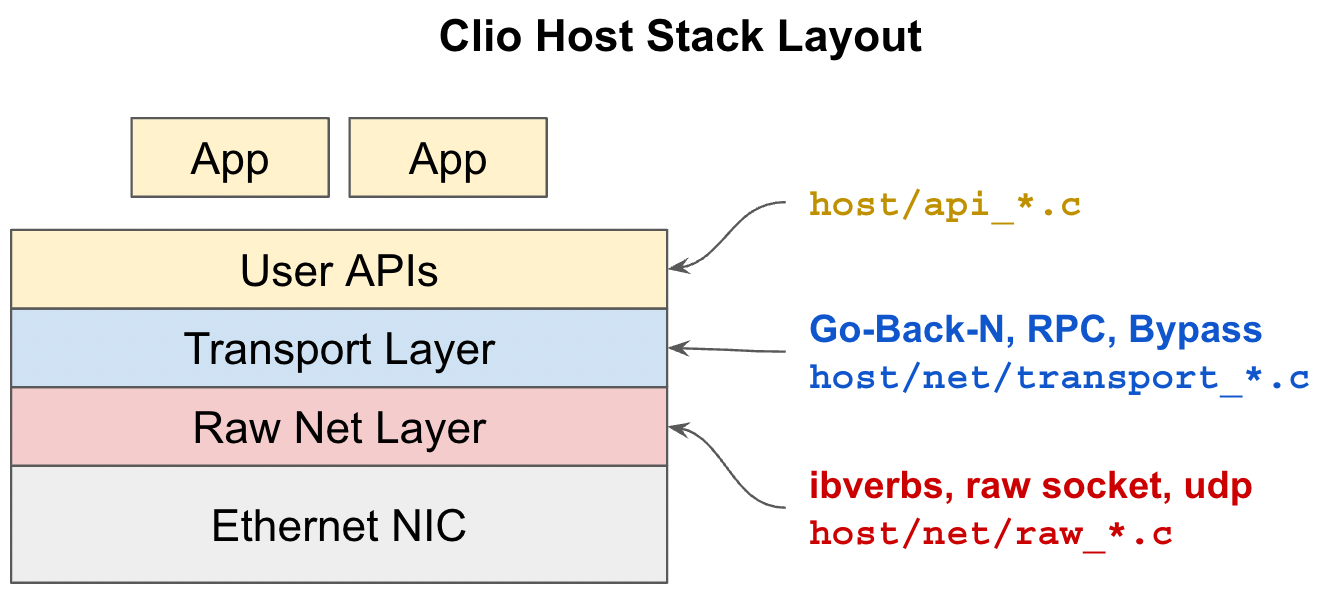

Clio system has three major parts: the FPGA bitstream part, the ARM SoC part, and the host-side software.

To compile Clio, see Documentation/compile.md.

To run Clio, see Documentation/run.md.

To debug Clio, see Documentation/debug.md.

ASPLOS'22 Artifact Evaluators, please see Documentation/asplos-ae.md.

High-level layout:

FPGA side stack layout:

Host side stack layout:

MIT

This is a research prototype. Use at your own risk.

Please use Github Issues.