Implementing 32 Verilog Mini Projects.

32 bit adder,

Array Multiplier,

Barrel Shifter,

Binary Divider 16 by 8,

Booth Multiplication,

CRC Coding,

Carry Select and Carry Look Ahead Adder,

Carry Skip and Carry Save Adder,

Complex Multiplier,

Dice Game,

FIFO,

Fixed Point Adder and Subtractor,

Fixed Point Multiplier and Divider,

Floating Point IEEE 754 Addition Subtraction,

Floating Point IEEE 754 Division,

Floating Point IEEE 754 Multiplication,

Fraction Multiplier,

High Radix Multiplier,

I2C and SPI Protocols,

LFSR and CFSR,

Logarithm Implementation,

Mealy and Moore State Machine Implementation of Sequence Detector,

Modified Booth Algorithm,

Pipelined Multiplier,

Restoring and Non Restoring Division,

Sequential Multiplier,

Shift and Add Binary Multiplier,

Traffic Light Controller,

Universal_Shift_Register,

BCD Adder,

Dual Address RAM and

Dual Address ROM

I2C and SPI Protocols

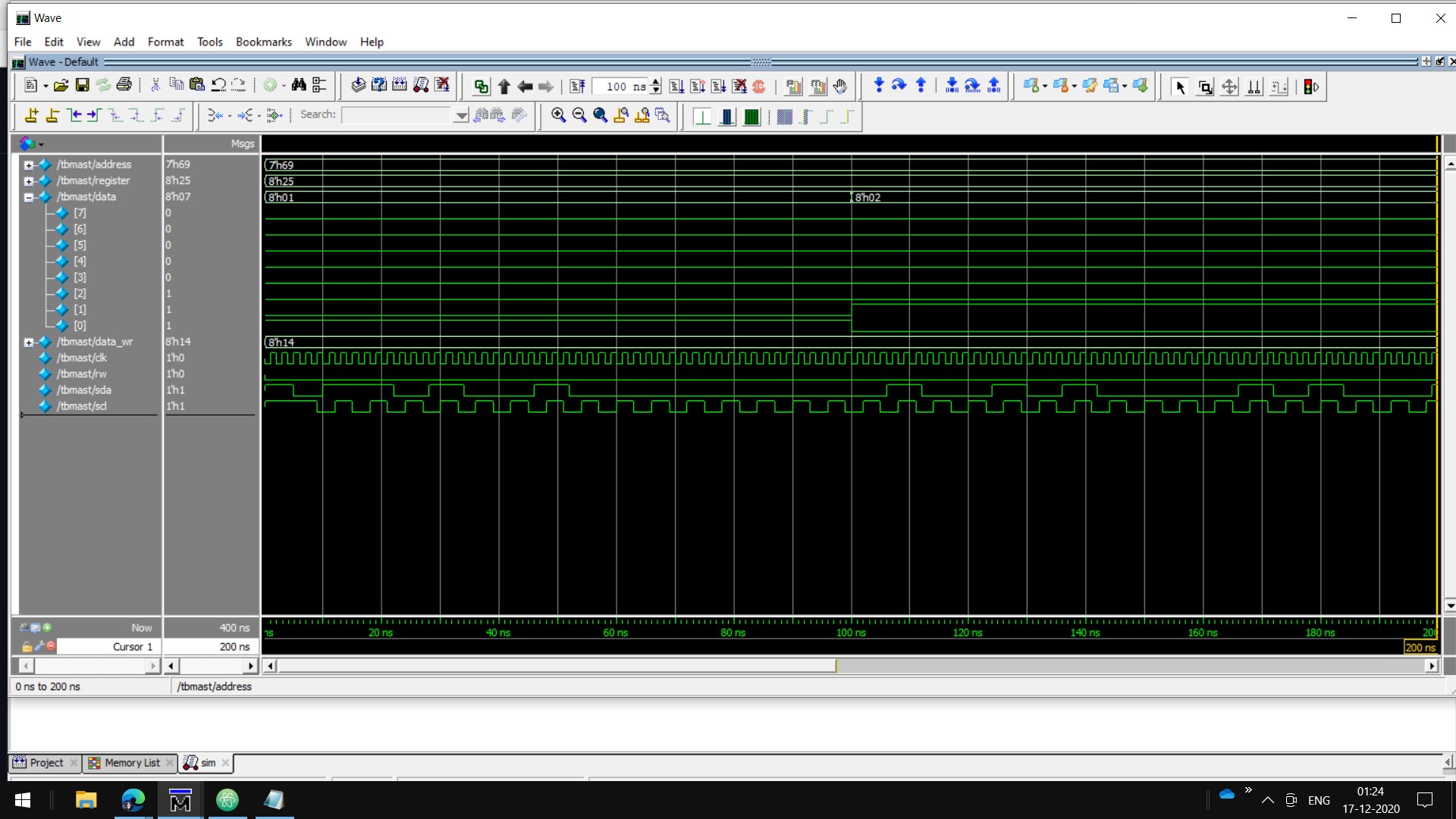

I2C Protocol

SPI Protocol

SPI Protocol

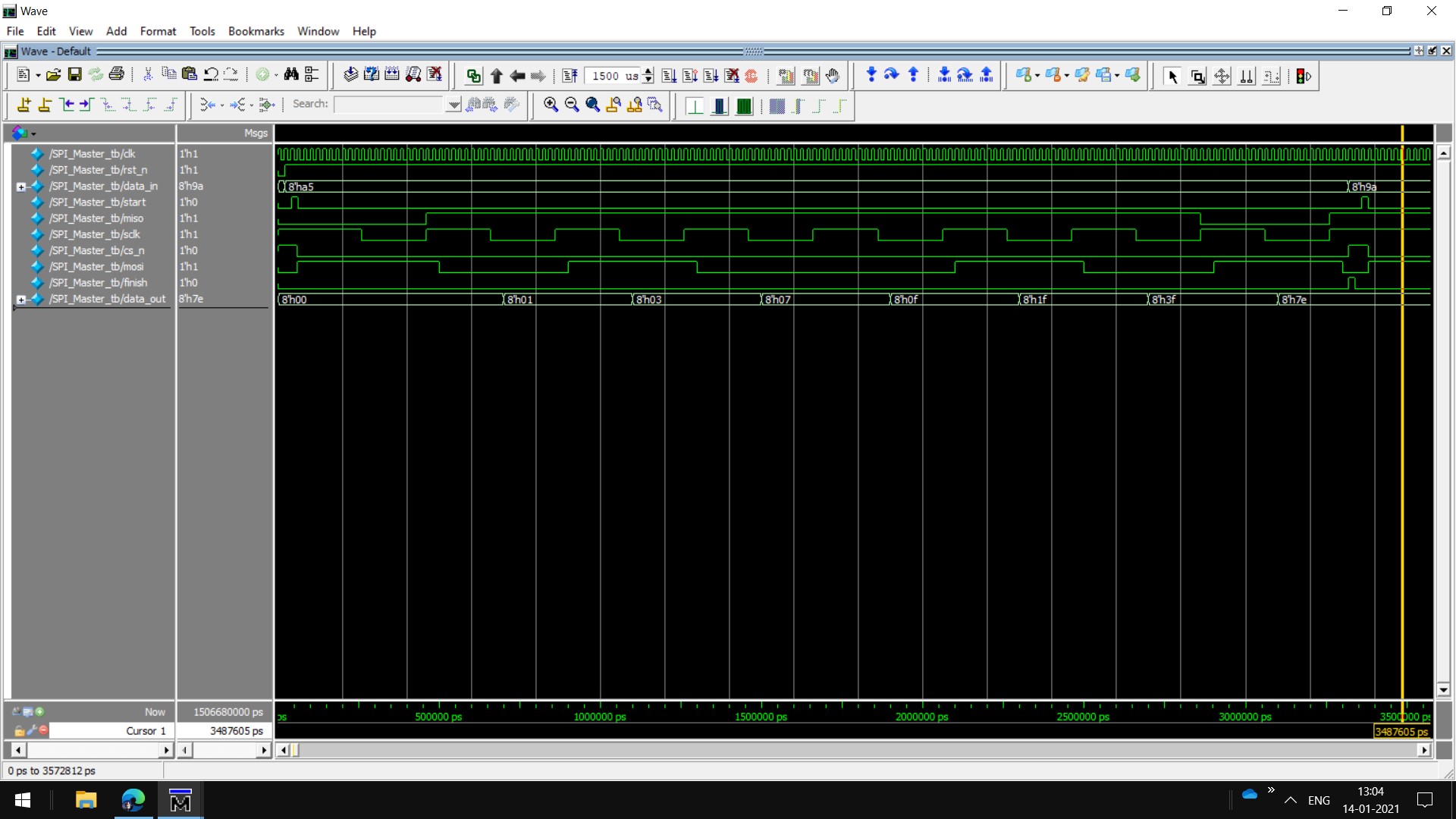

SPI_Master

SPI_Loopback

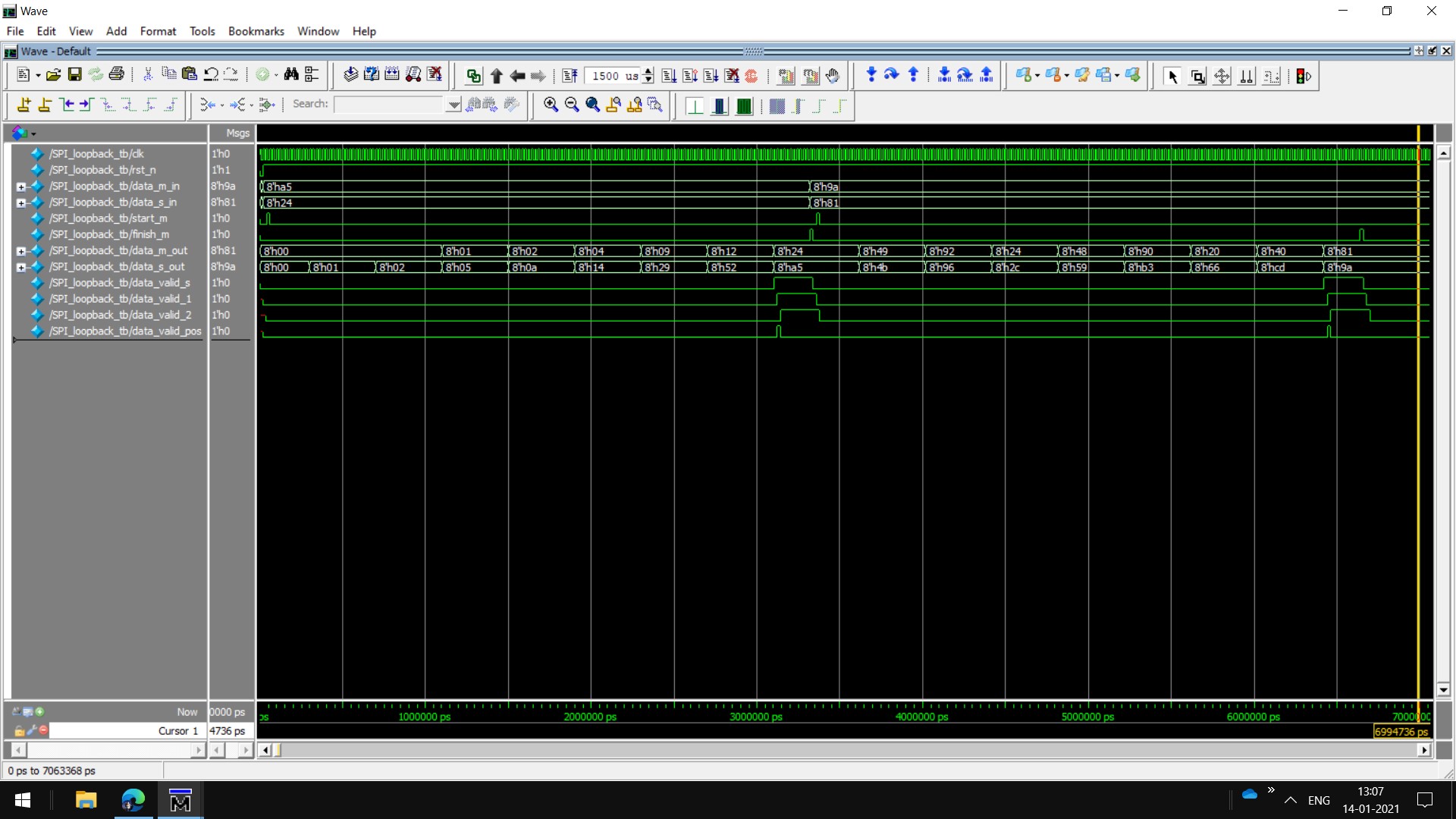

SPI_Loopback

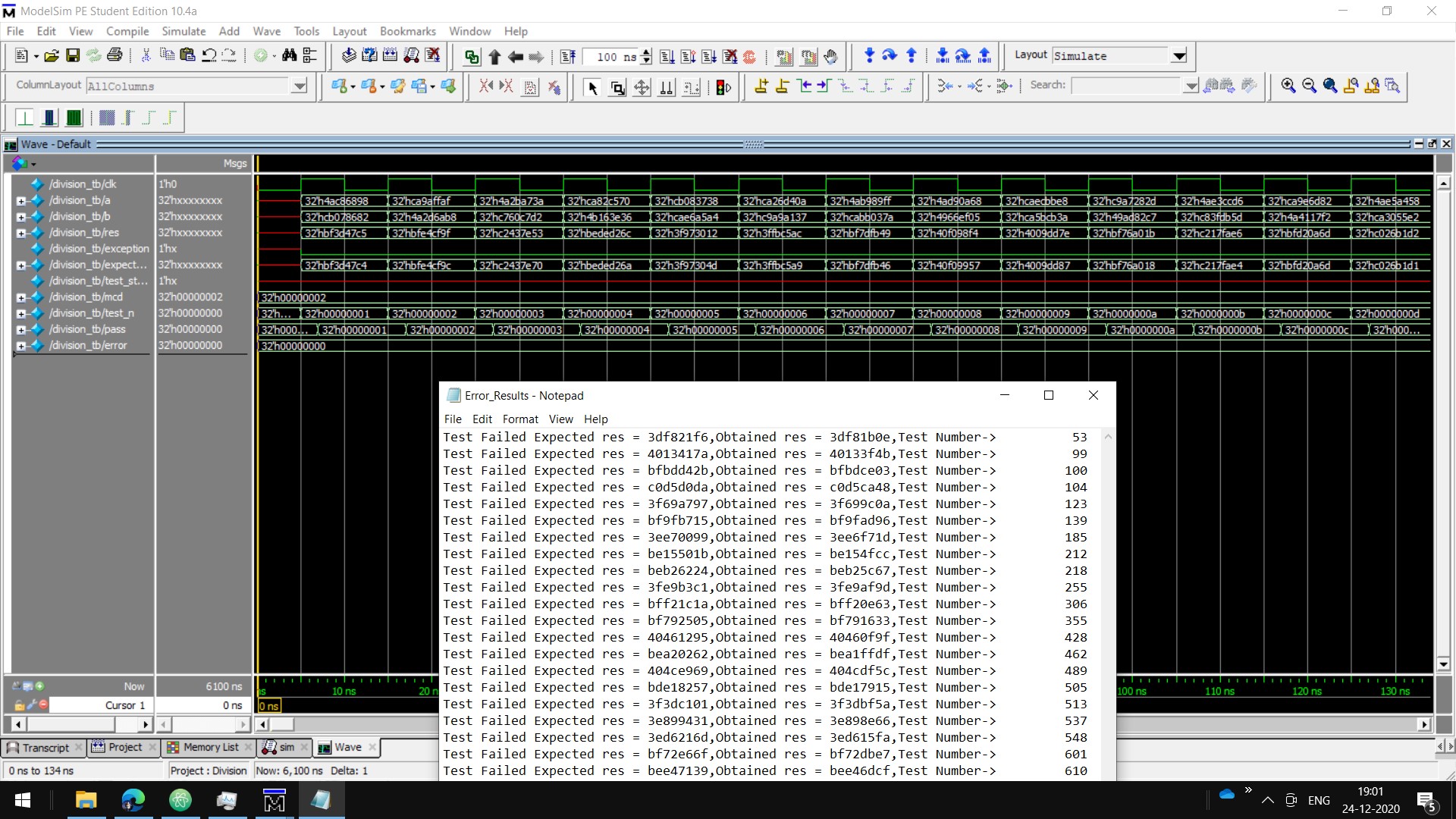

IEEE 754 Division

IEEE 754 Division

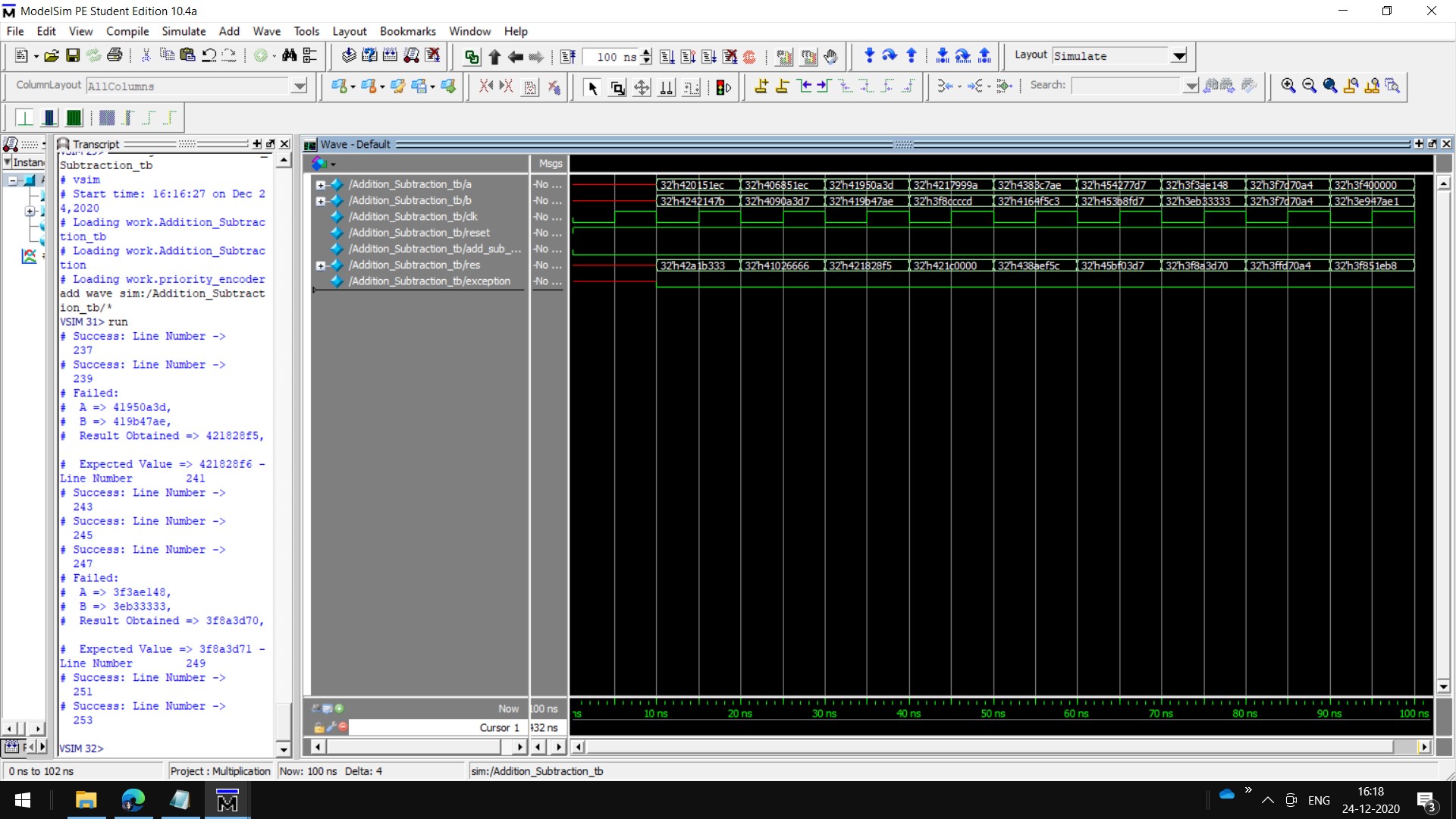

IEEE 754 Addition Subtraction

IEEE 754 Addition Subtraction

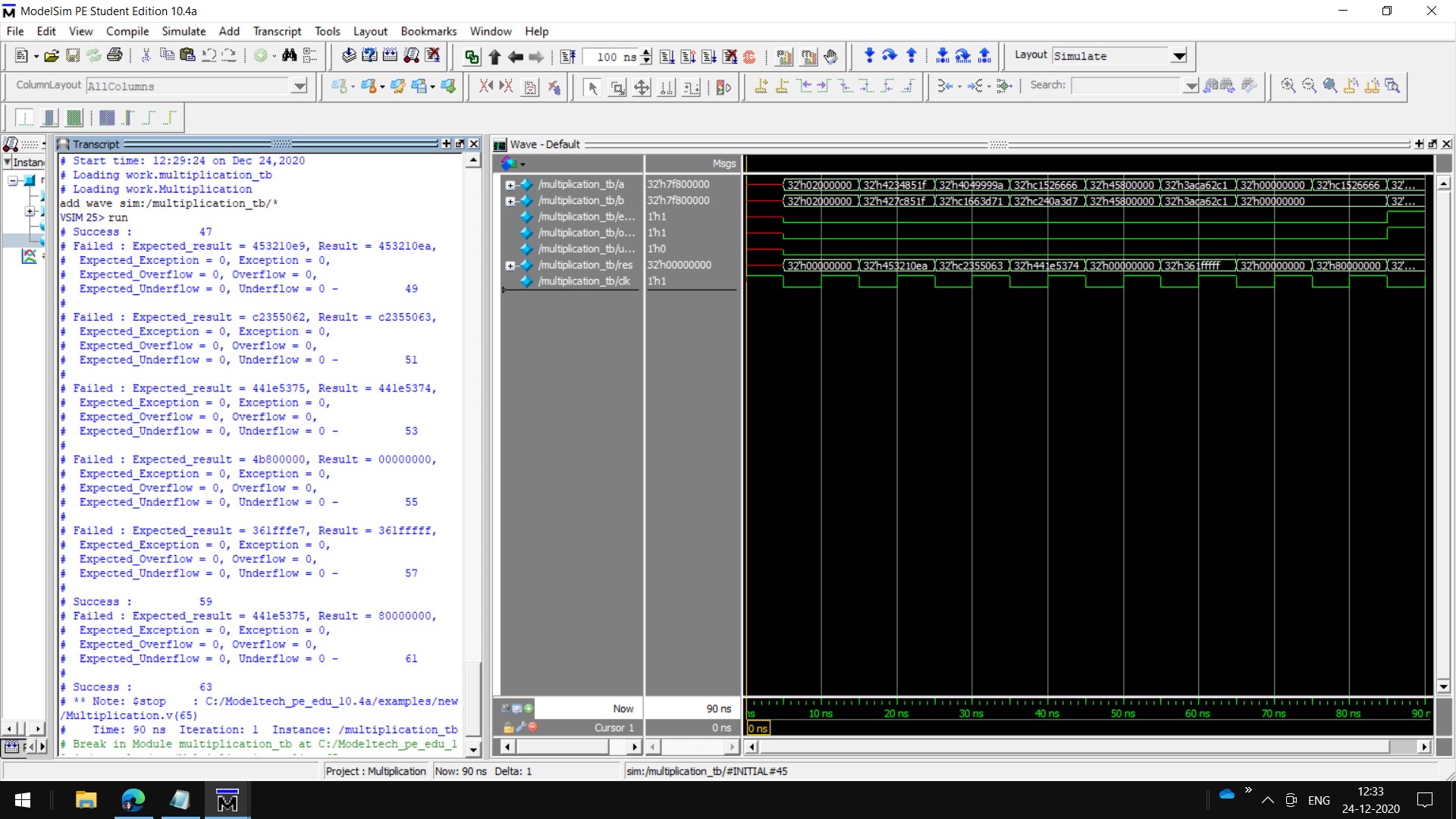

IEEE 754 Multiplication

IEEE 754 Multiplication

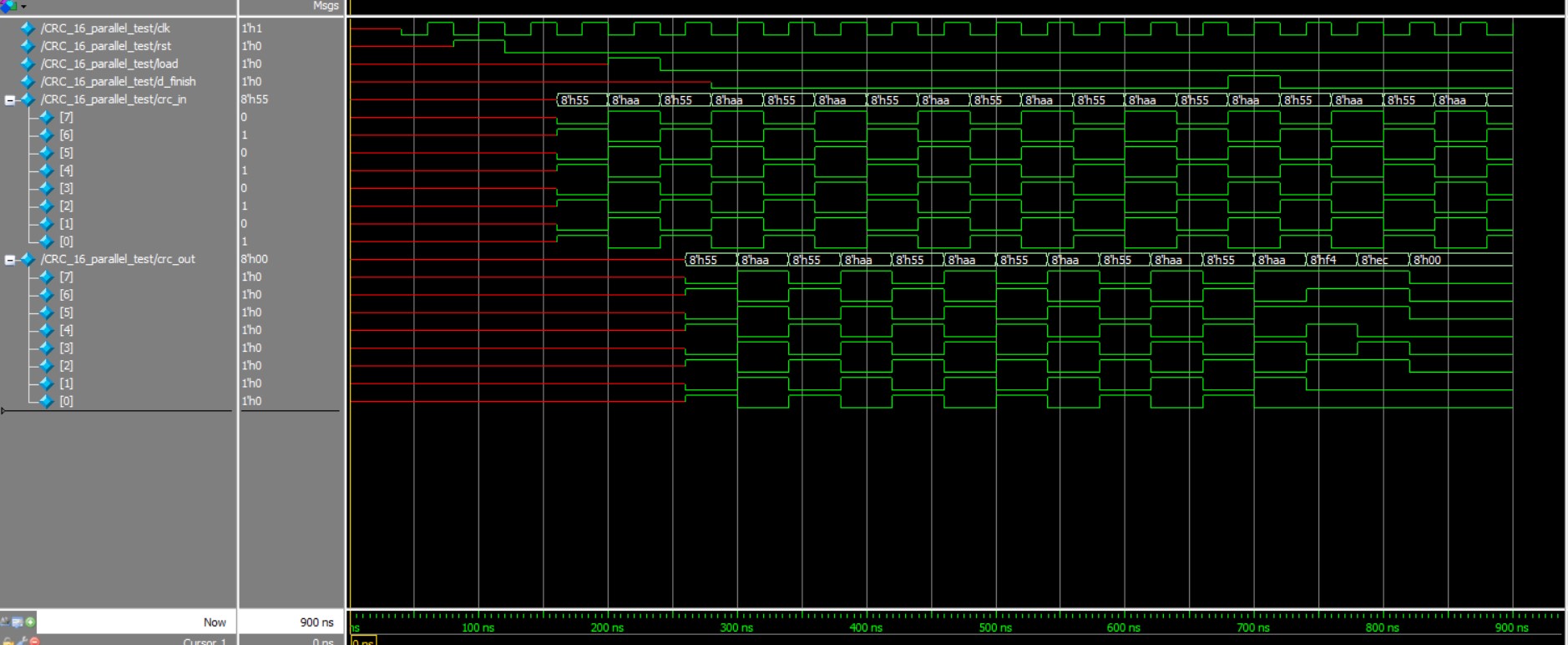

CRC Coding

CRC Coding

CRC_16_parallel

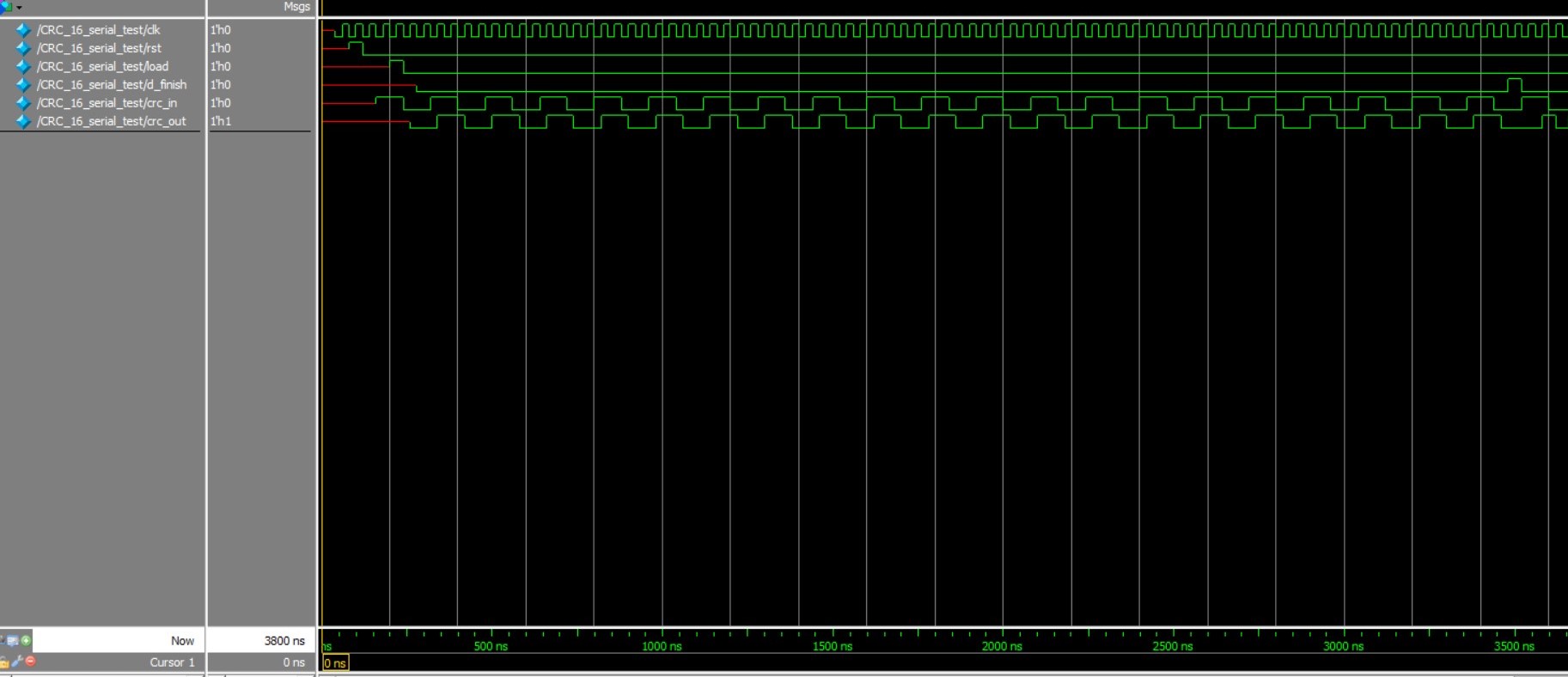

CRC_16_serial

CRC_16_serial

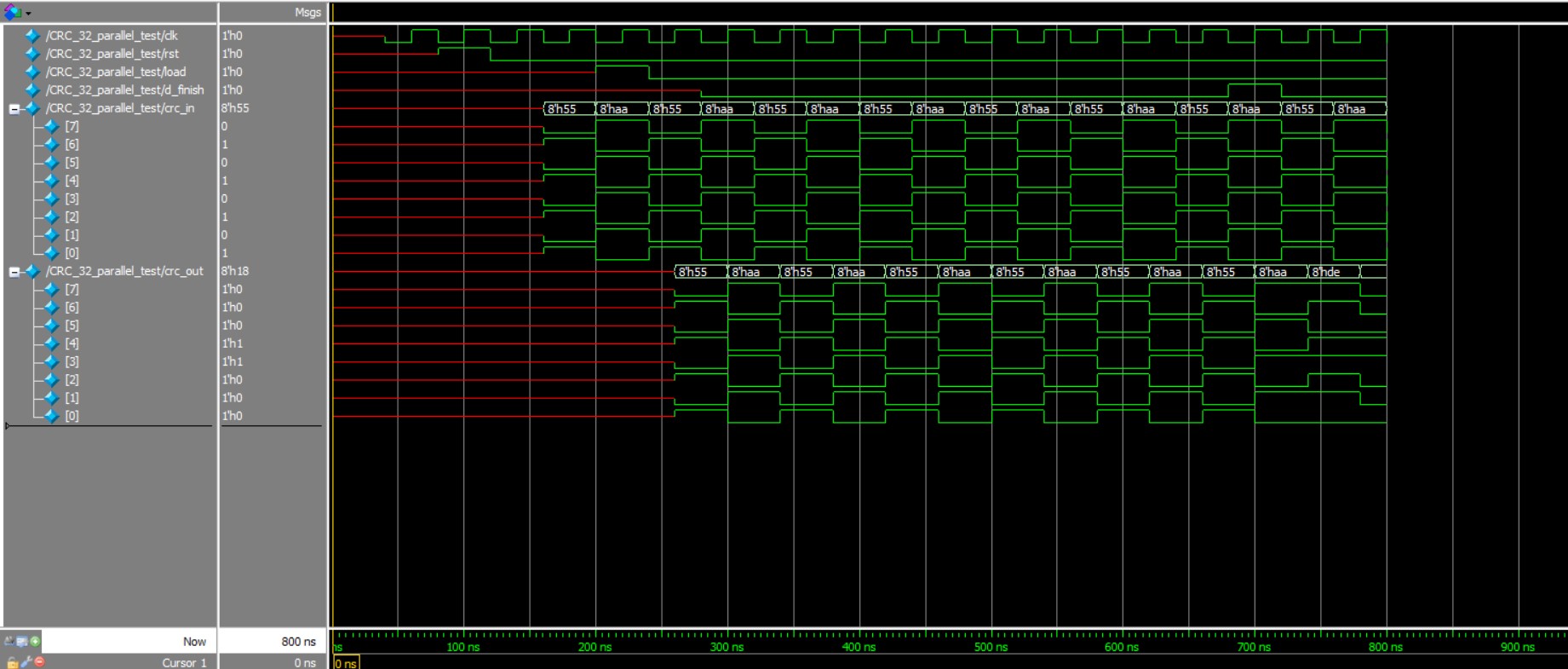

CRC_32_parallel

CRC_32_parallel

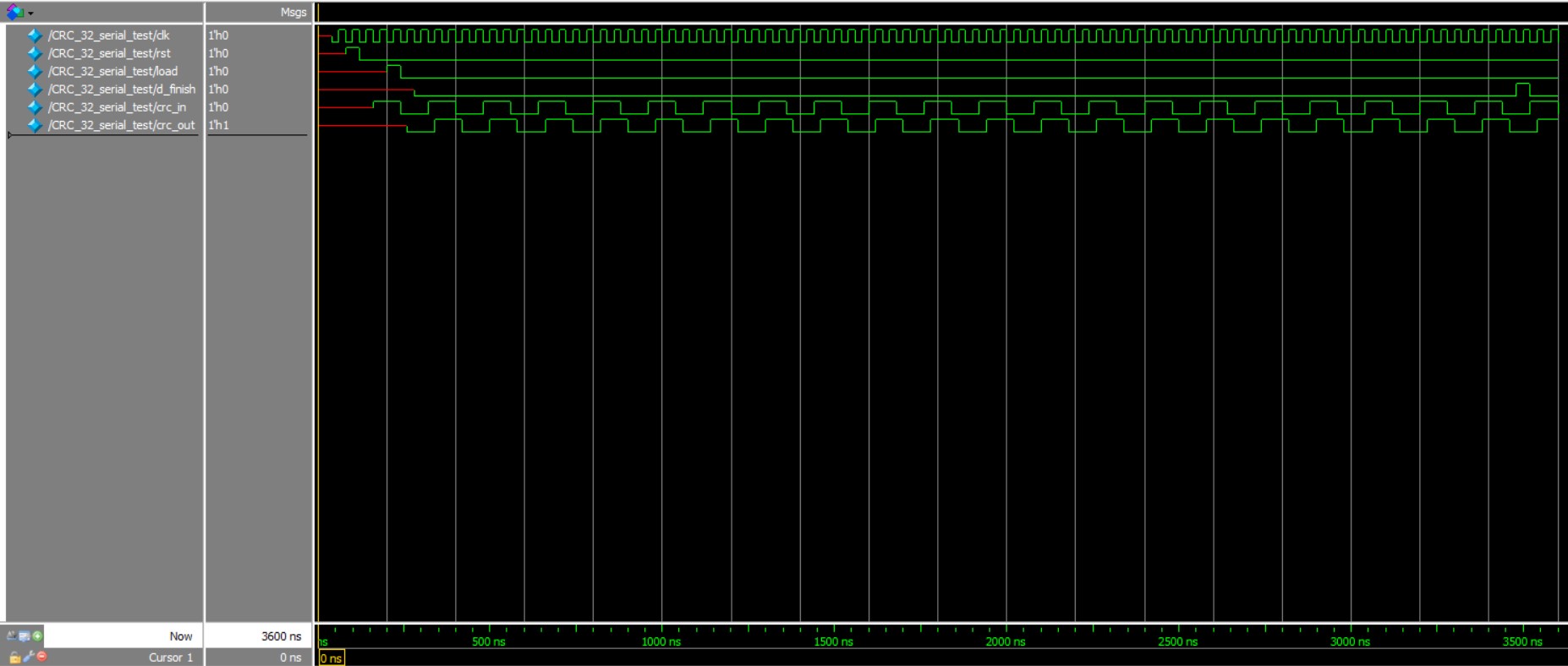

CRC_32_serial

CRC_32_serial

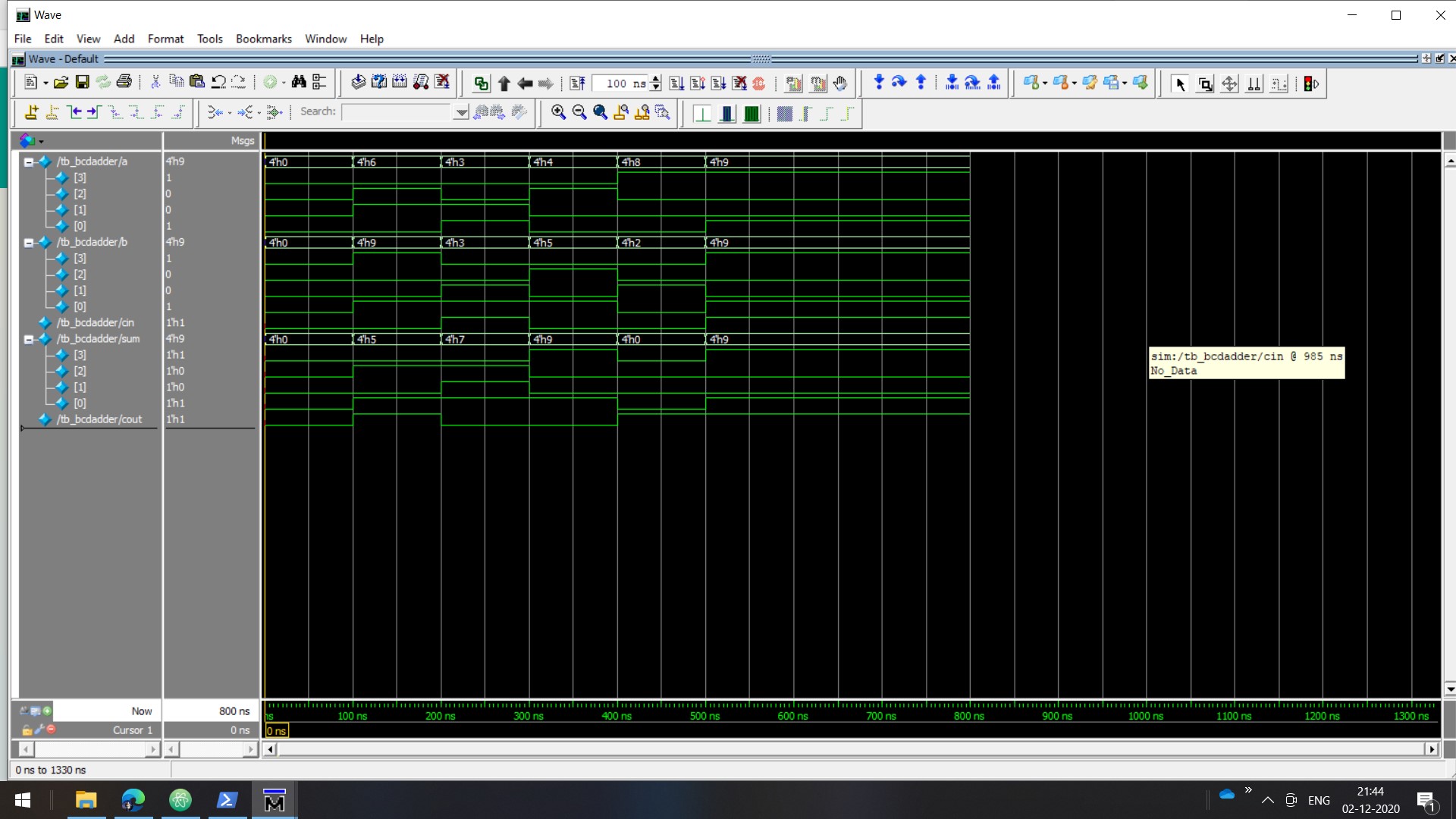

BCD Adder

BCD Adder

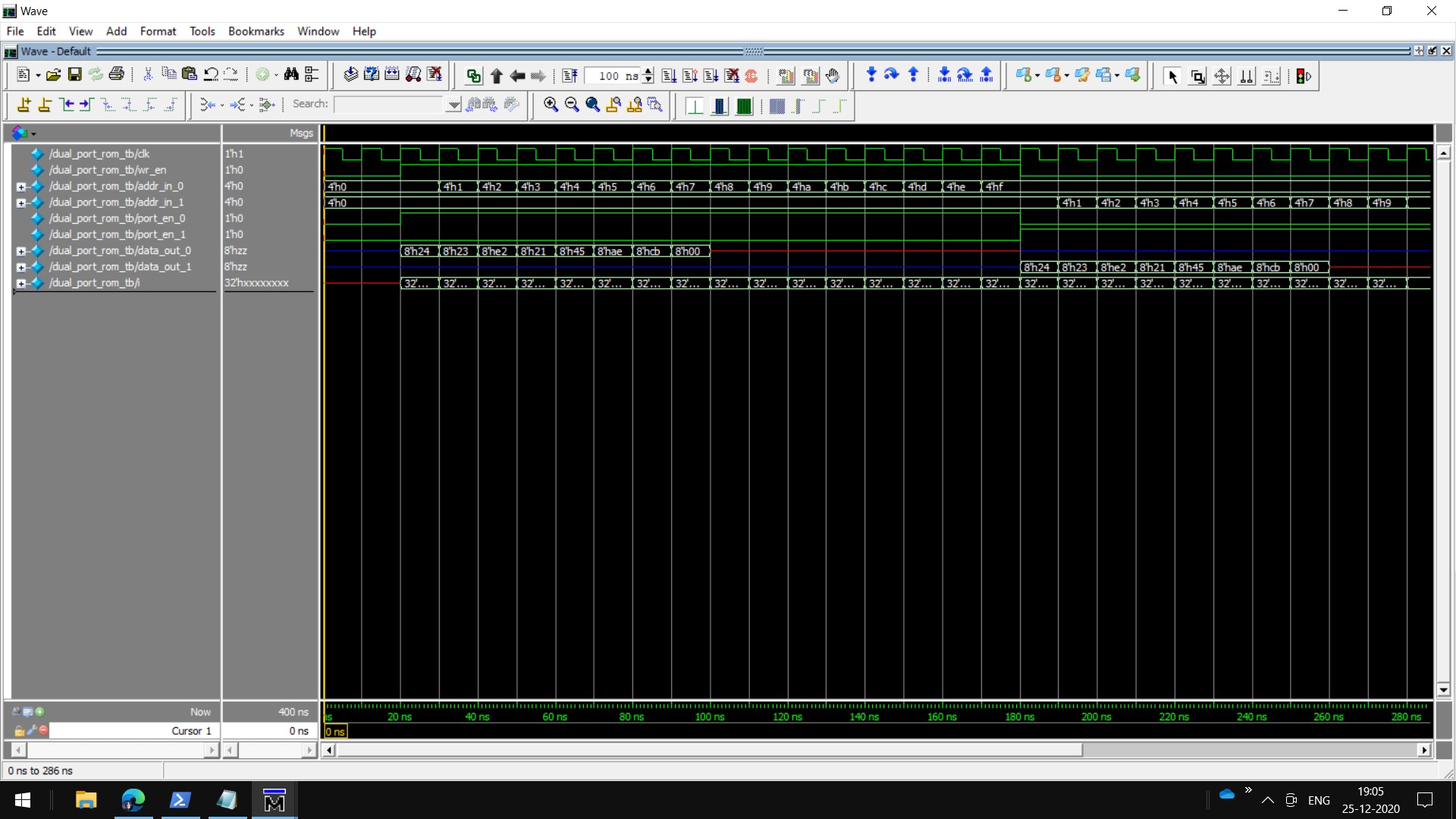

Dual Address ROM

Dual Address ROM

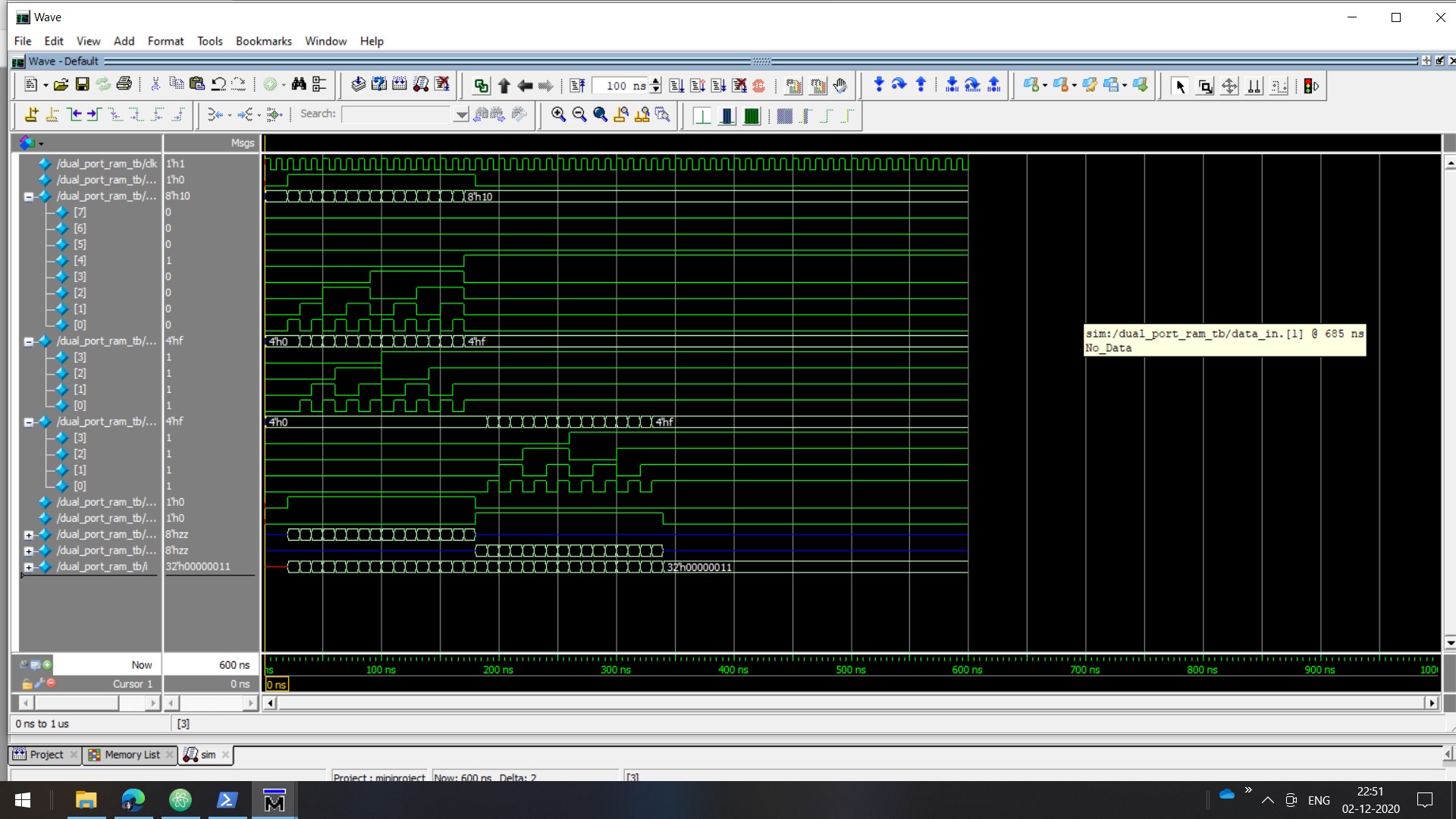

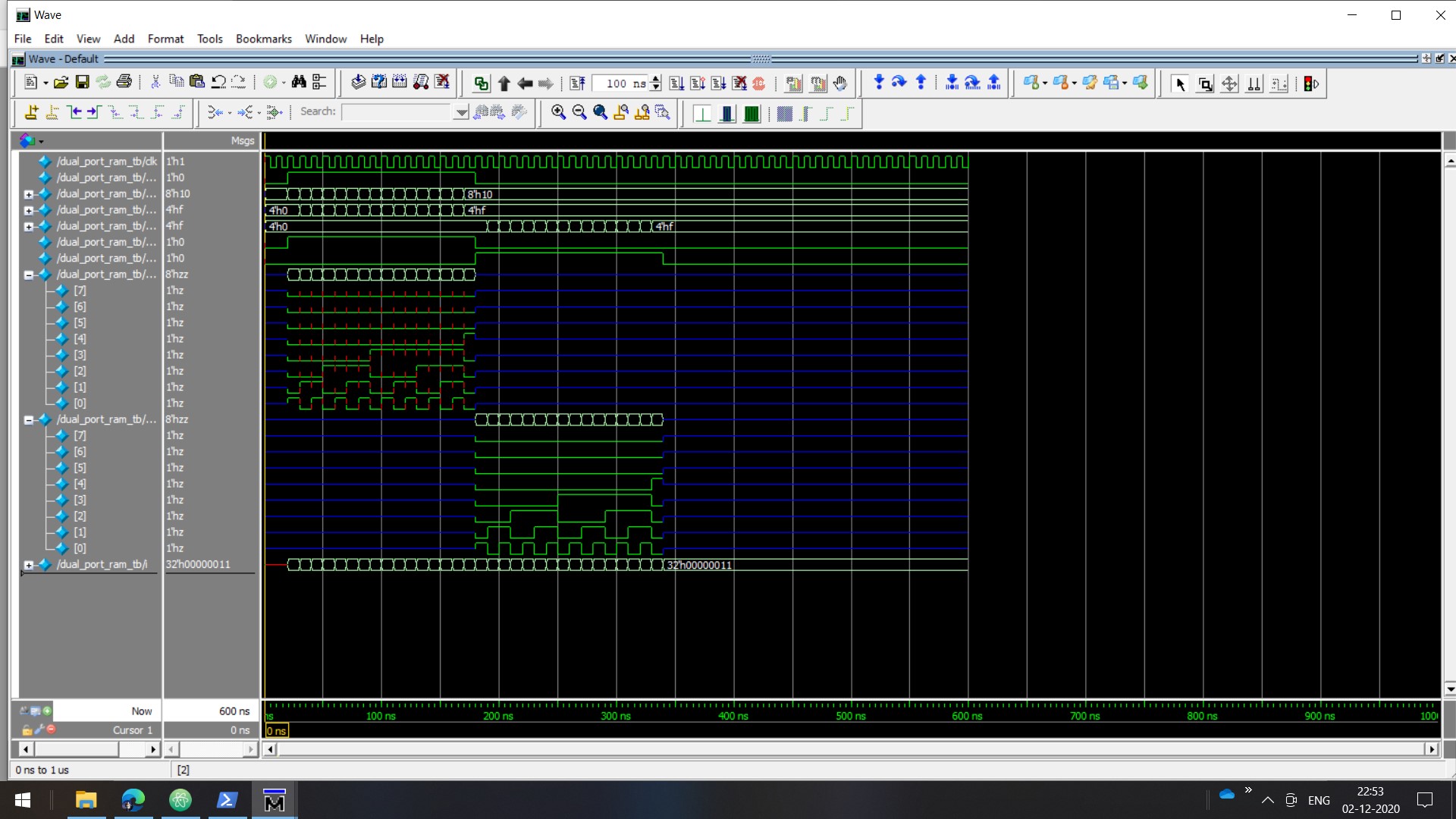

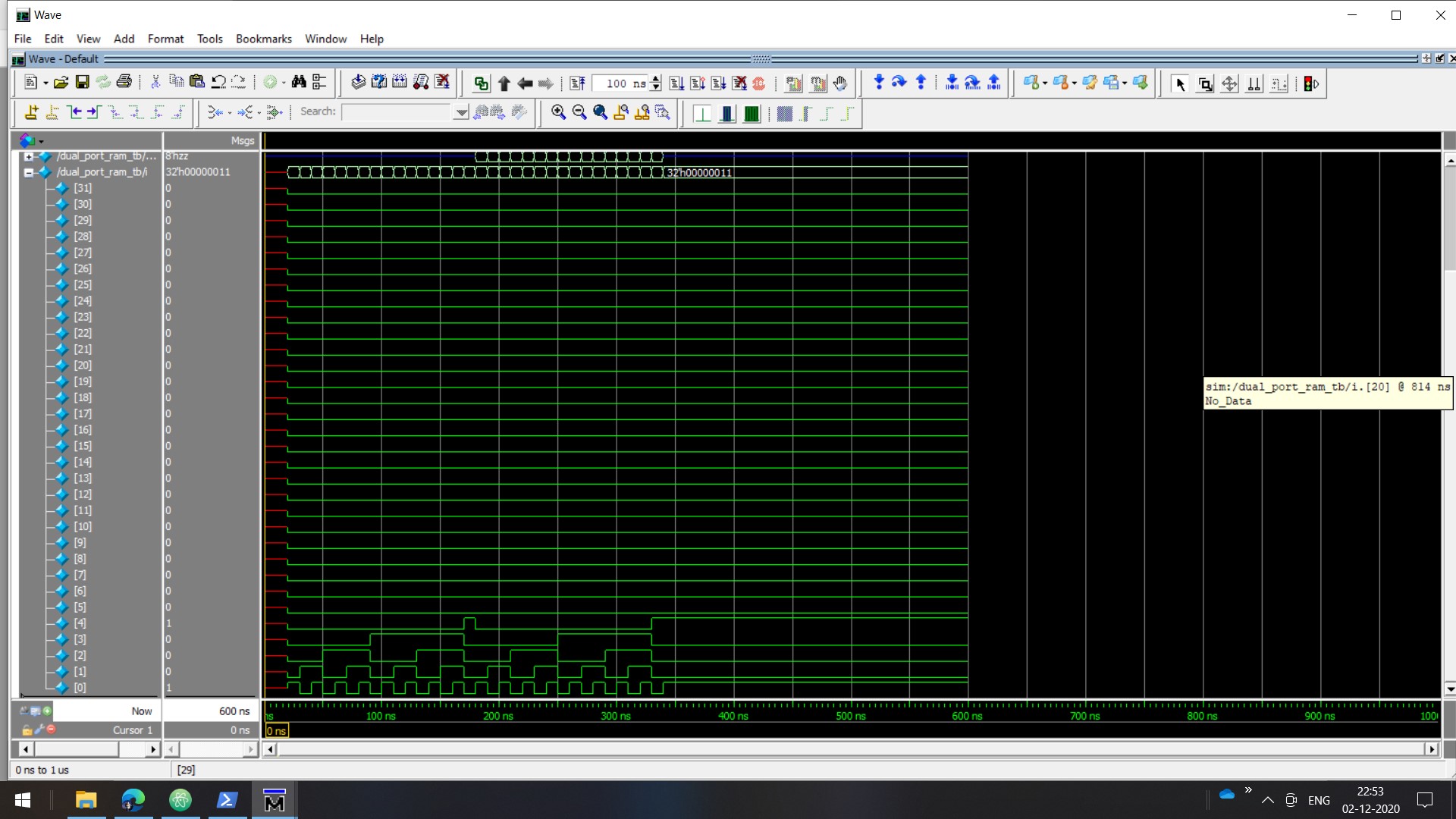

Dual Address RAM

Dual Address RAM

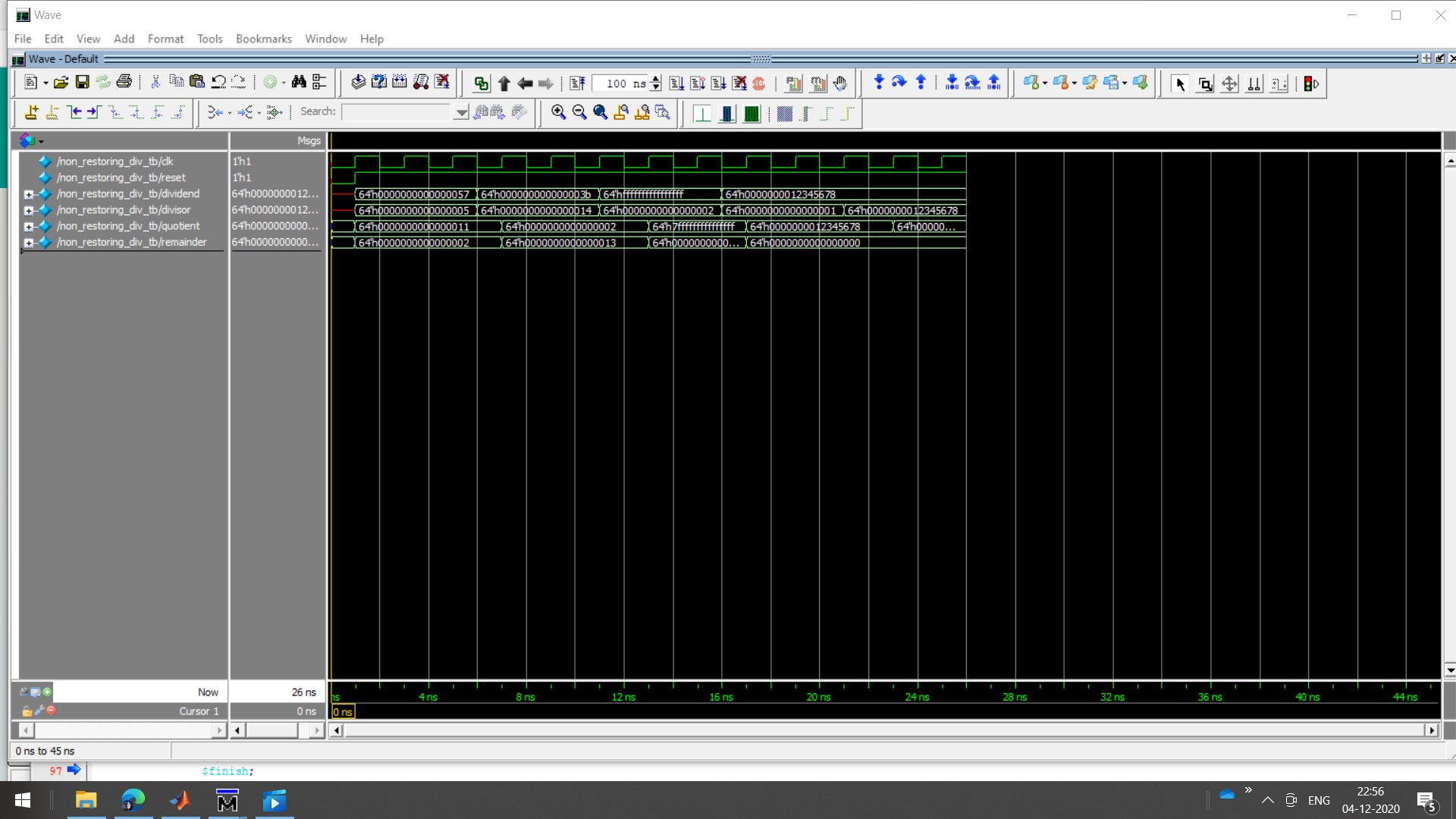

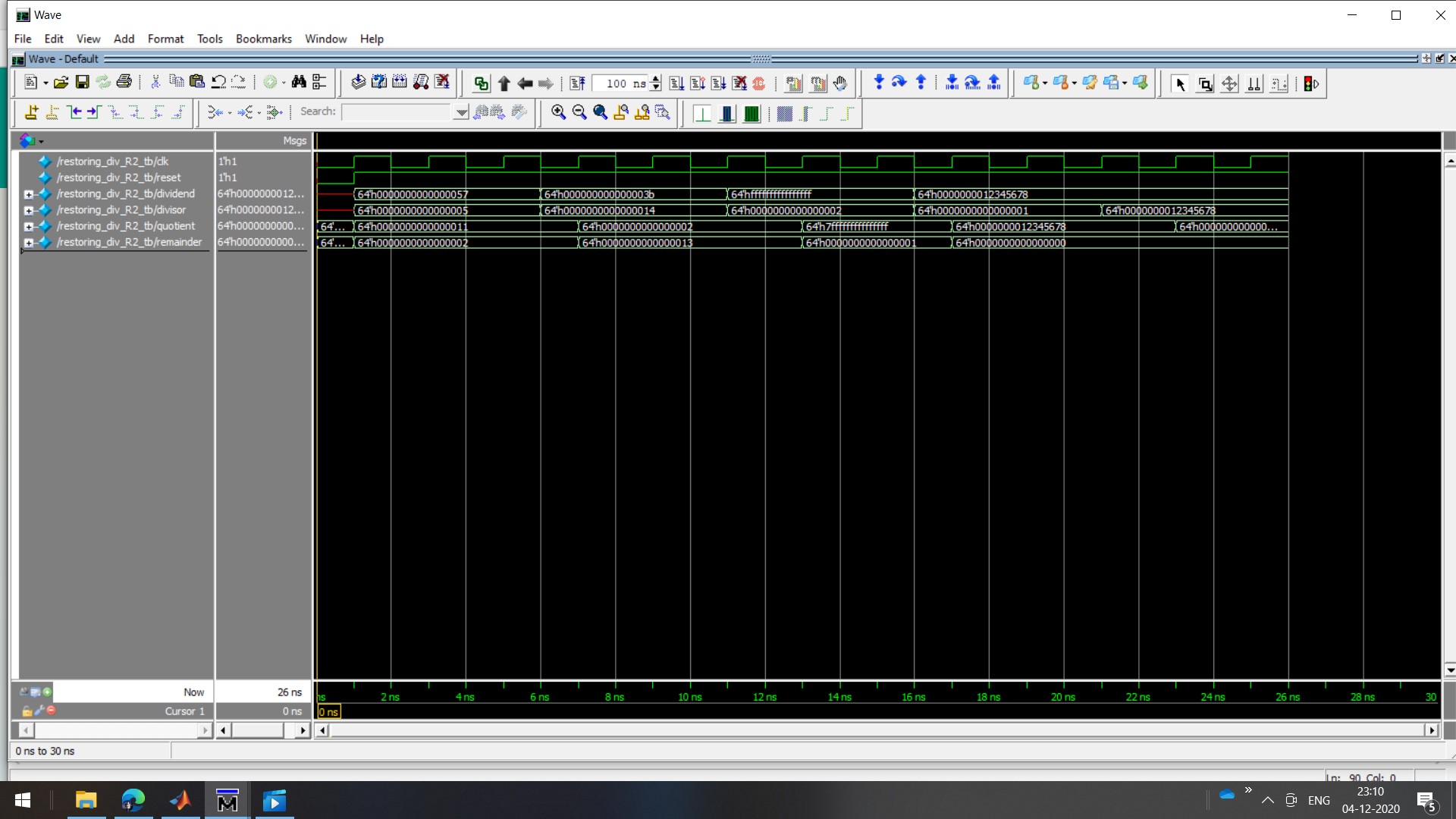

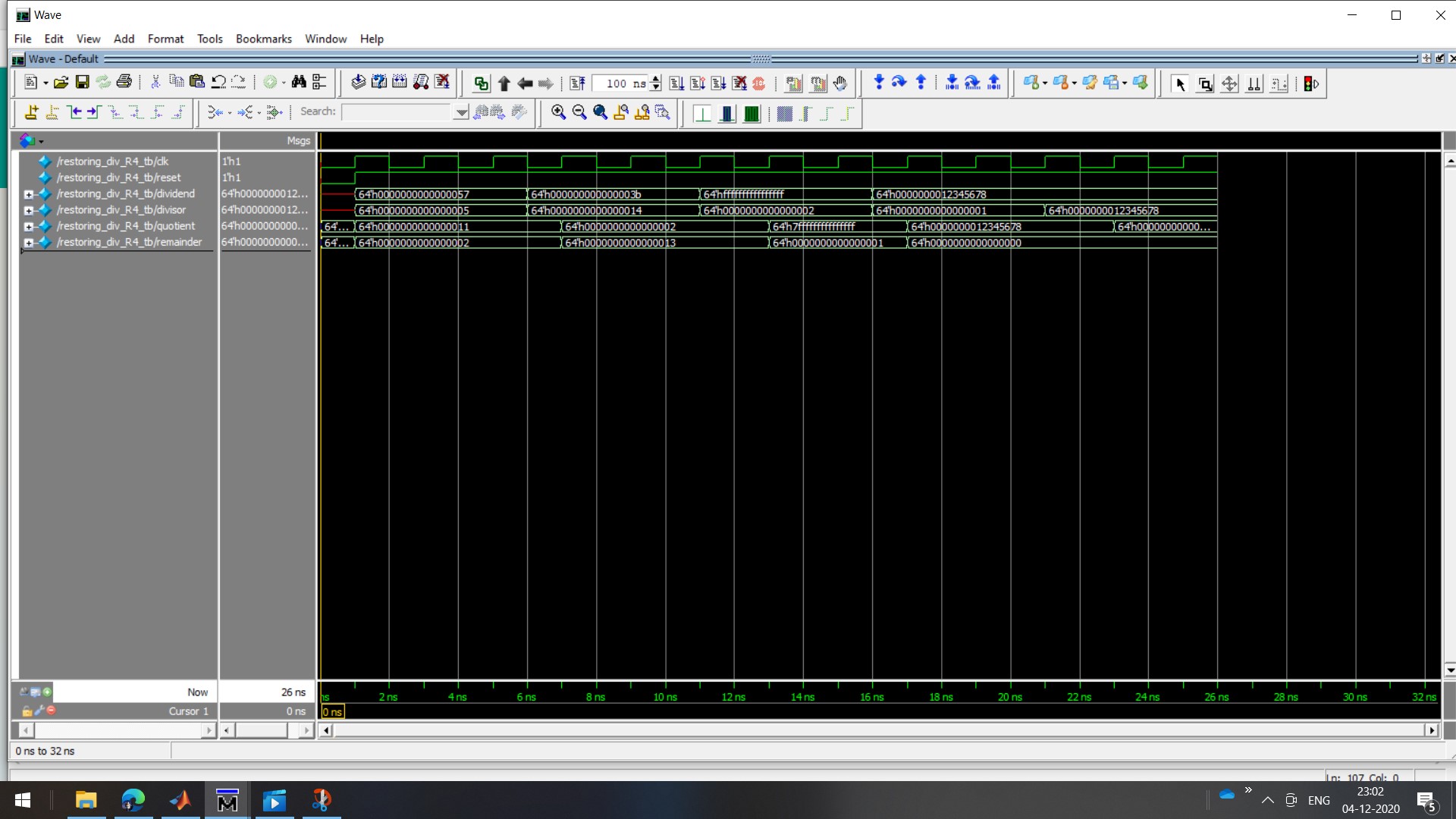

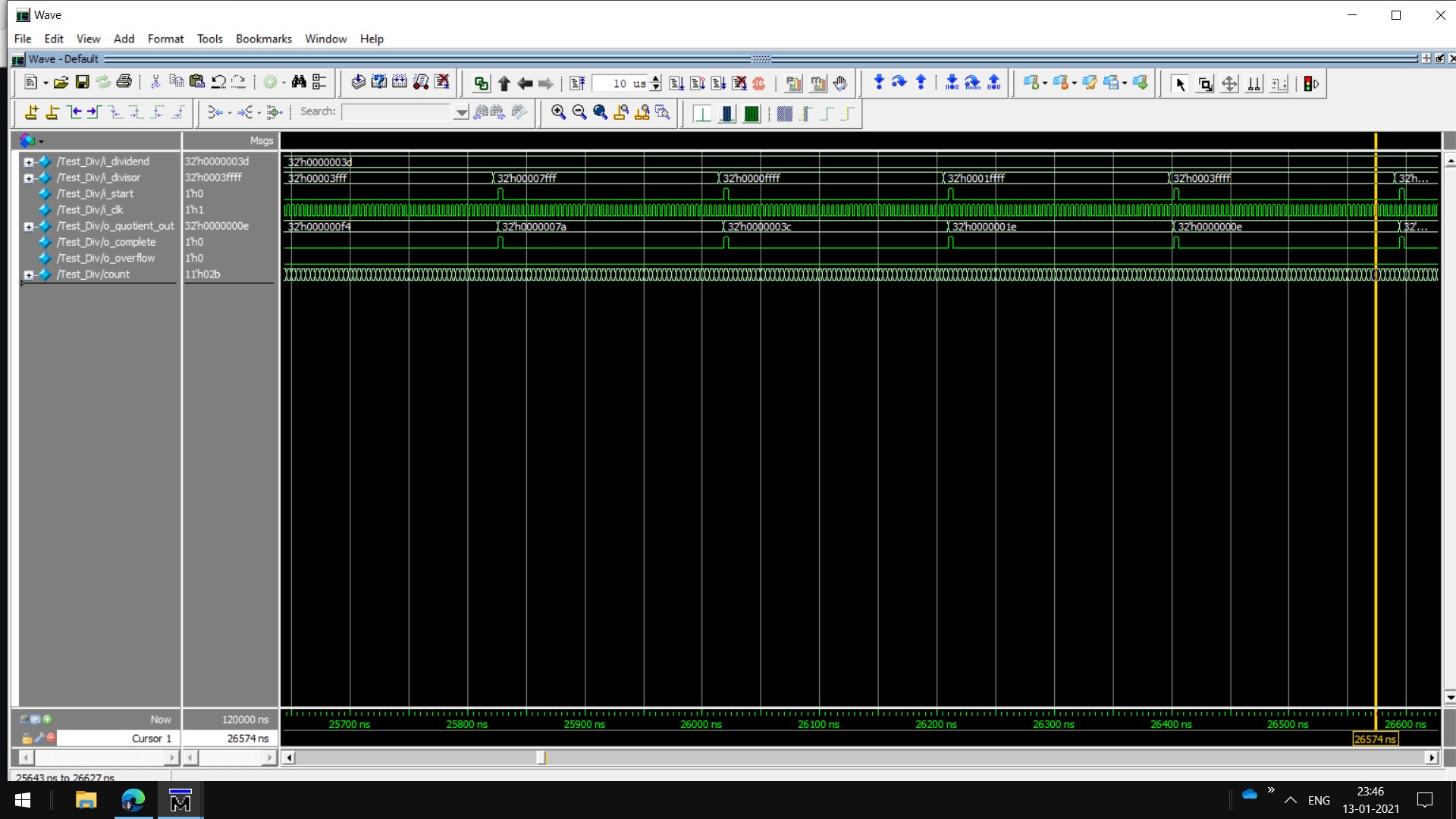

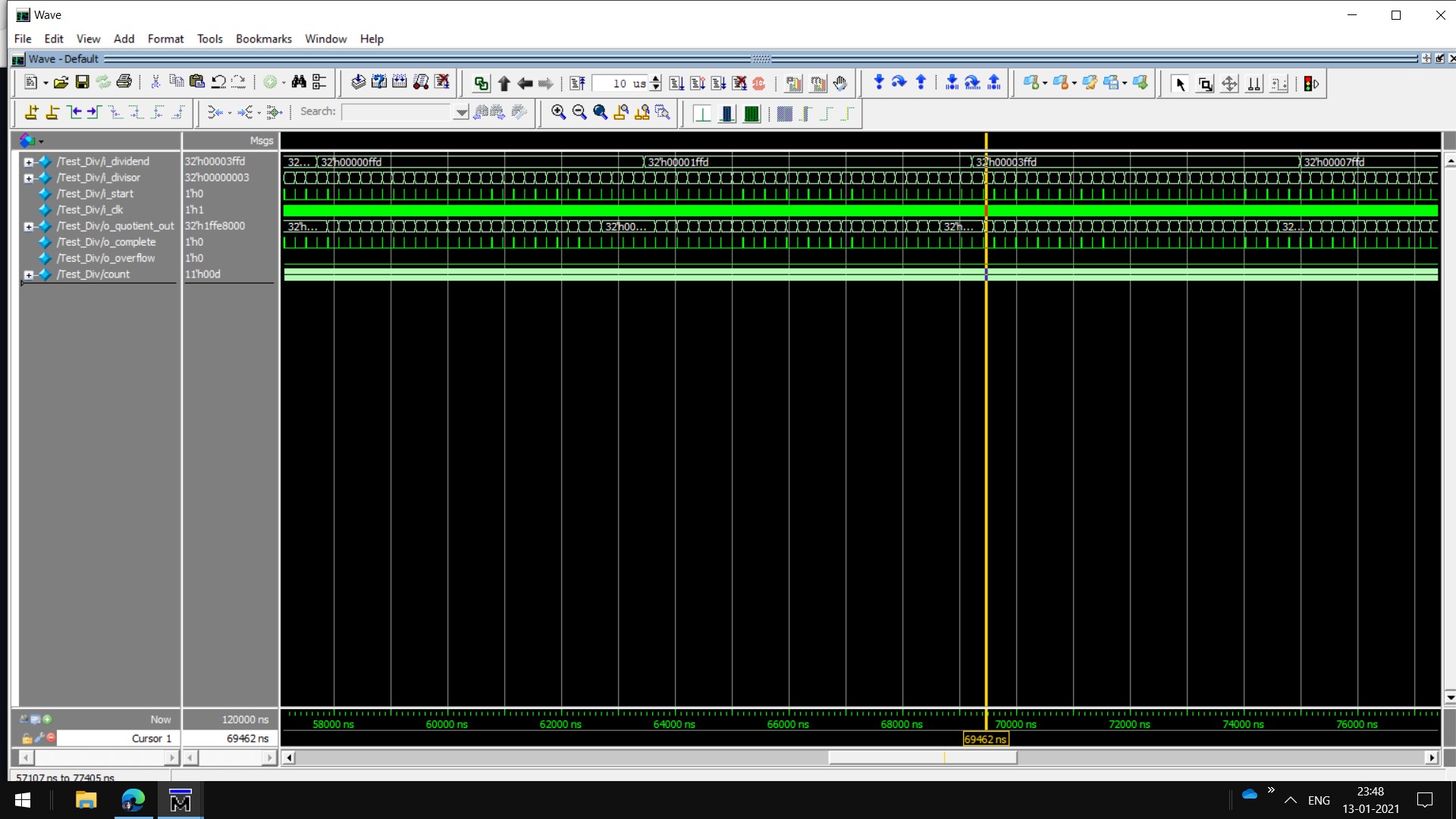

Restoring and Non Restoring Division

Restoring and Non Restoring Division

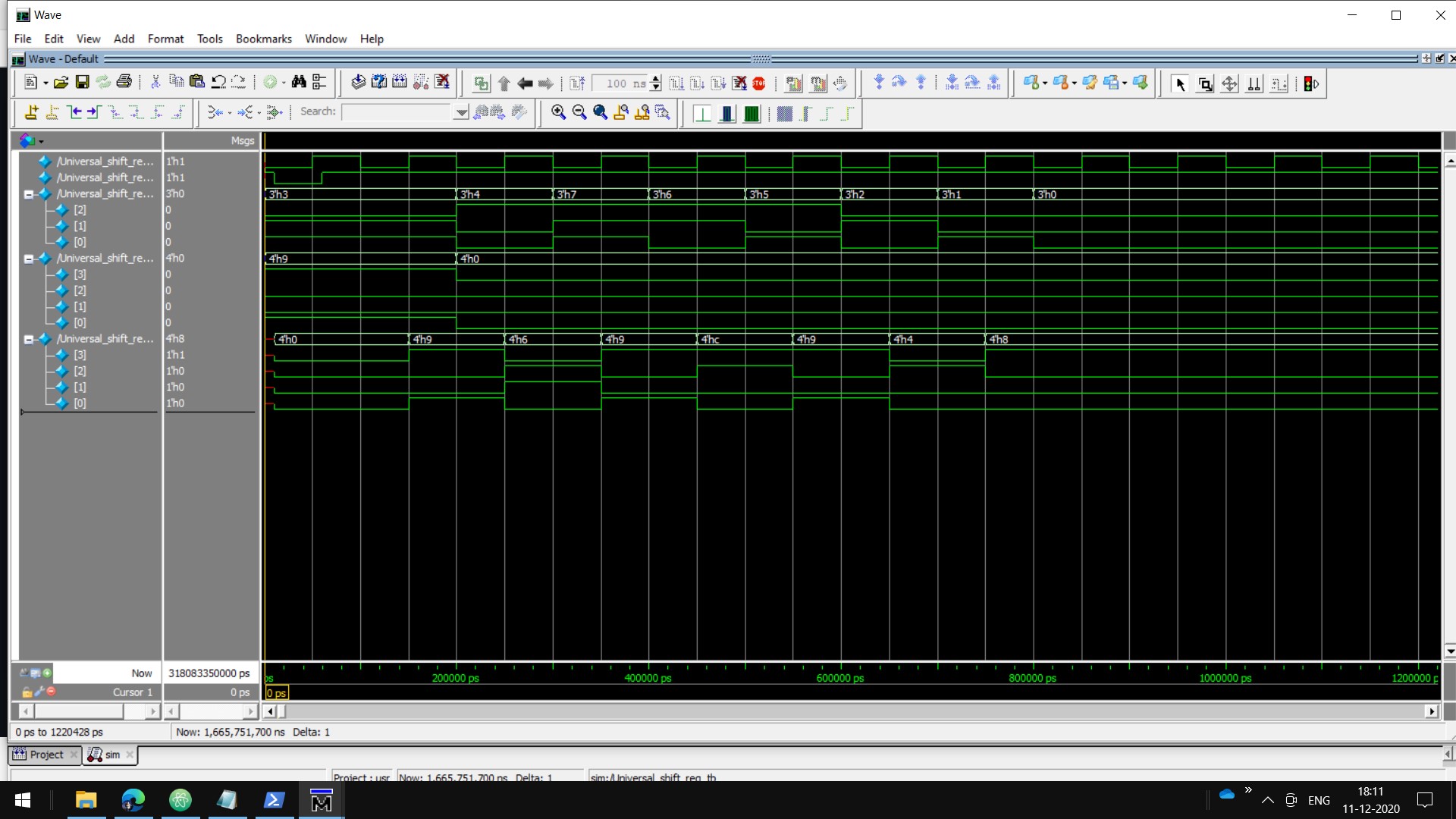

Universal Shift Register

Universal Shift Register

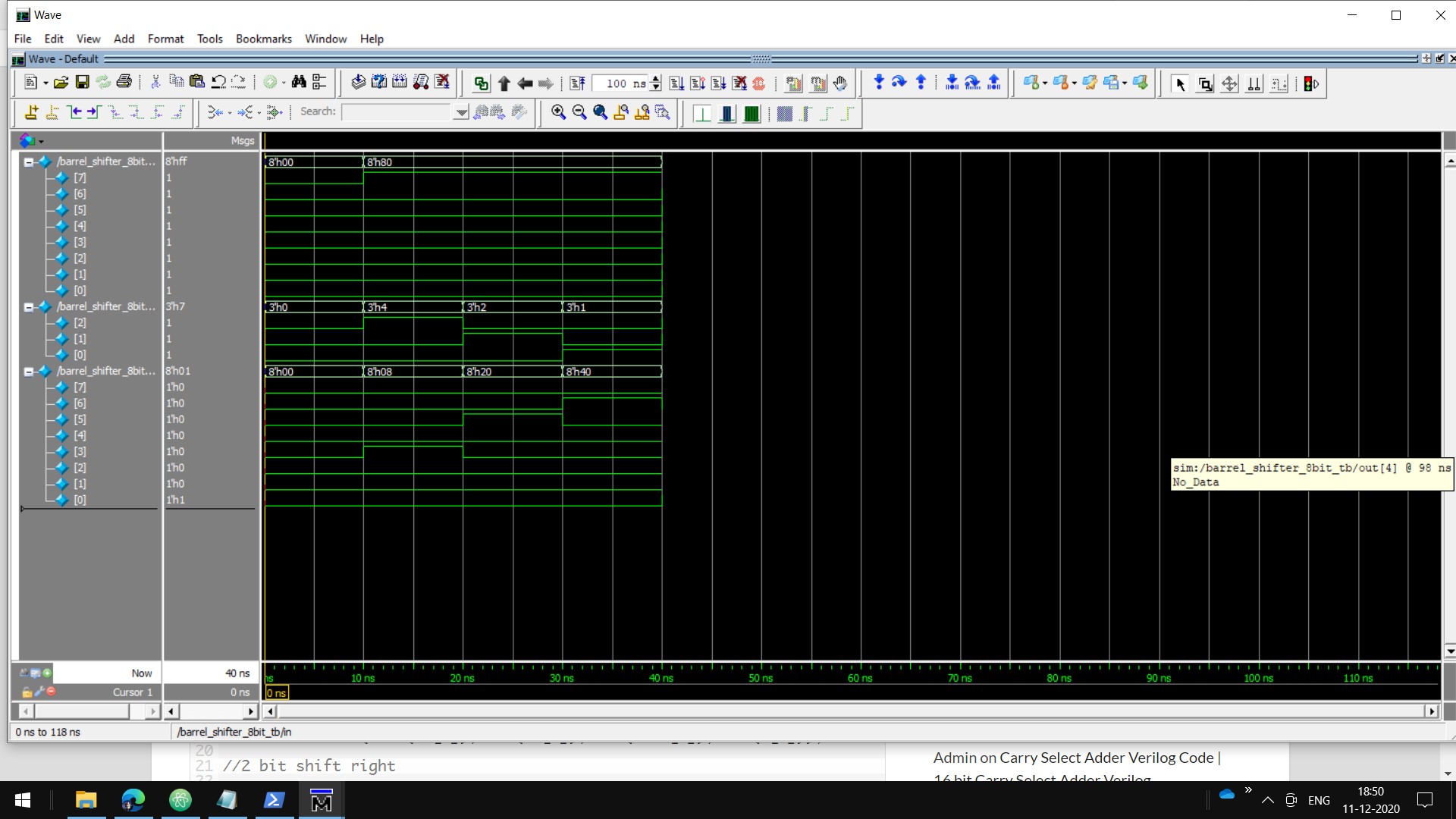

Barrel Shifter 8bit

Barrel Shifter 8bit

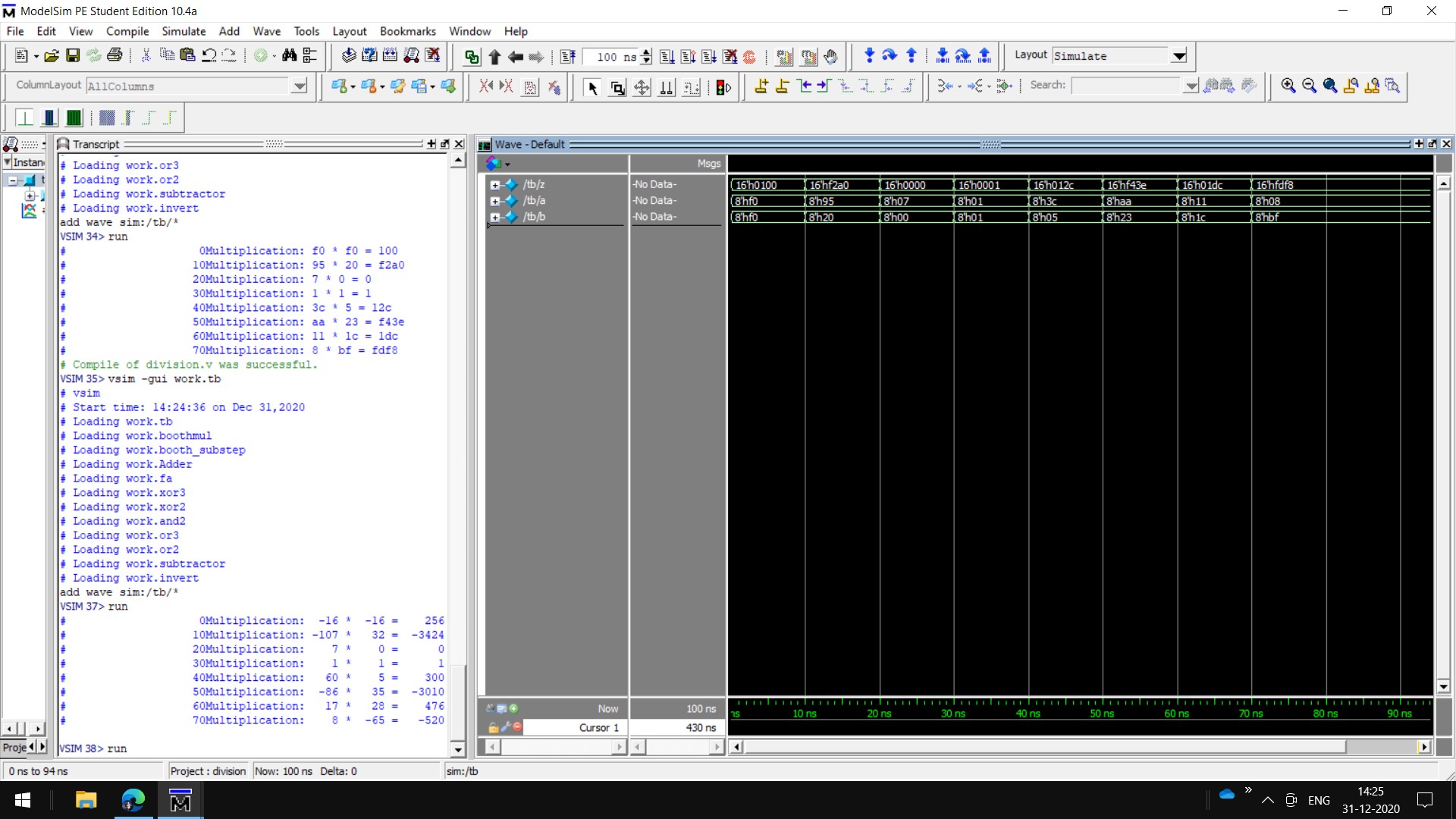

Booth Multiplier

Booth Multiplier

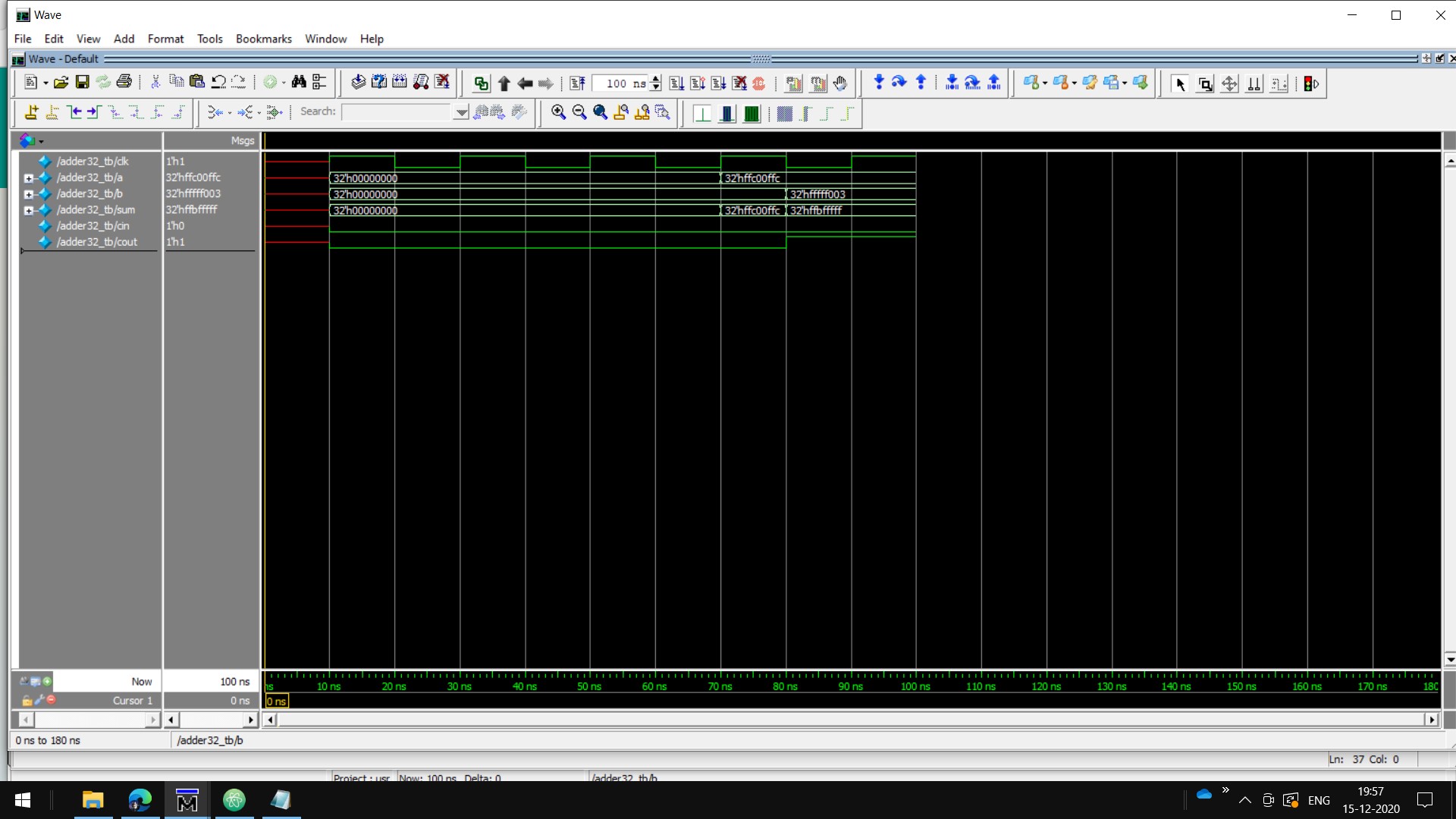

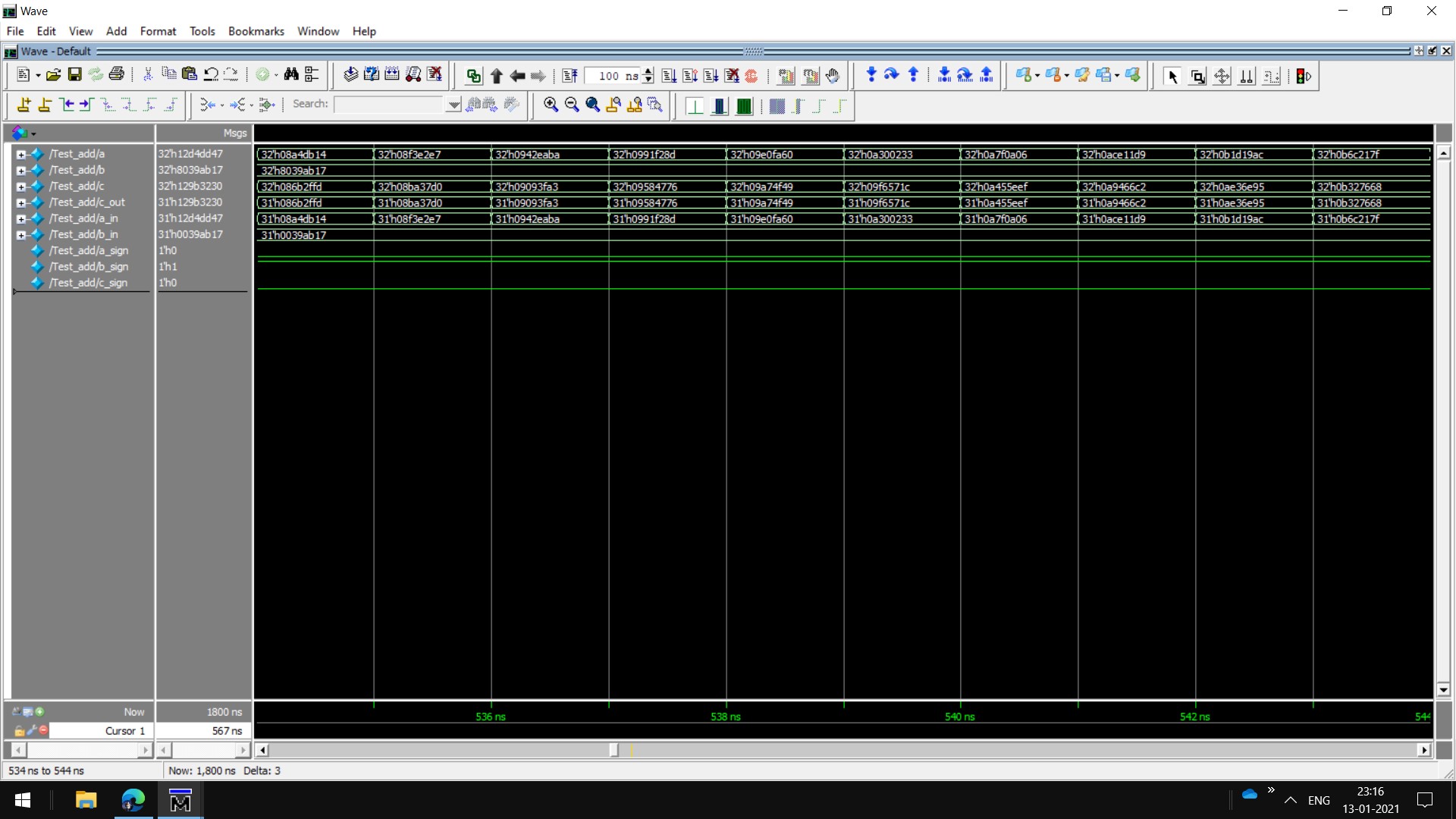

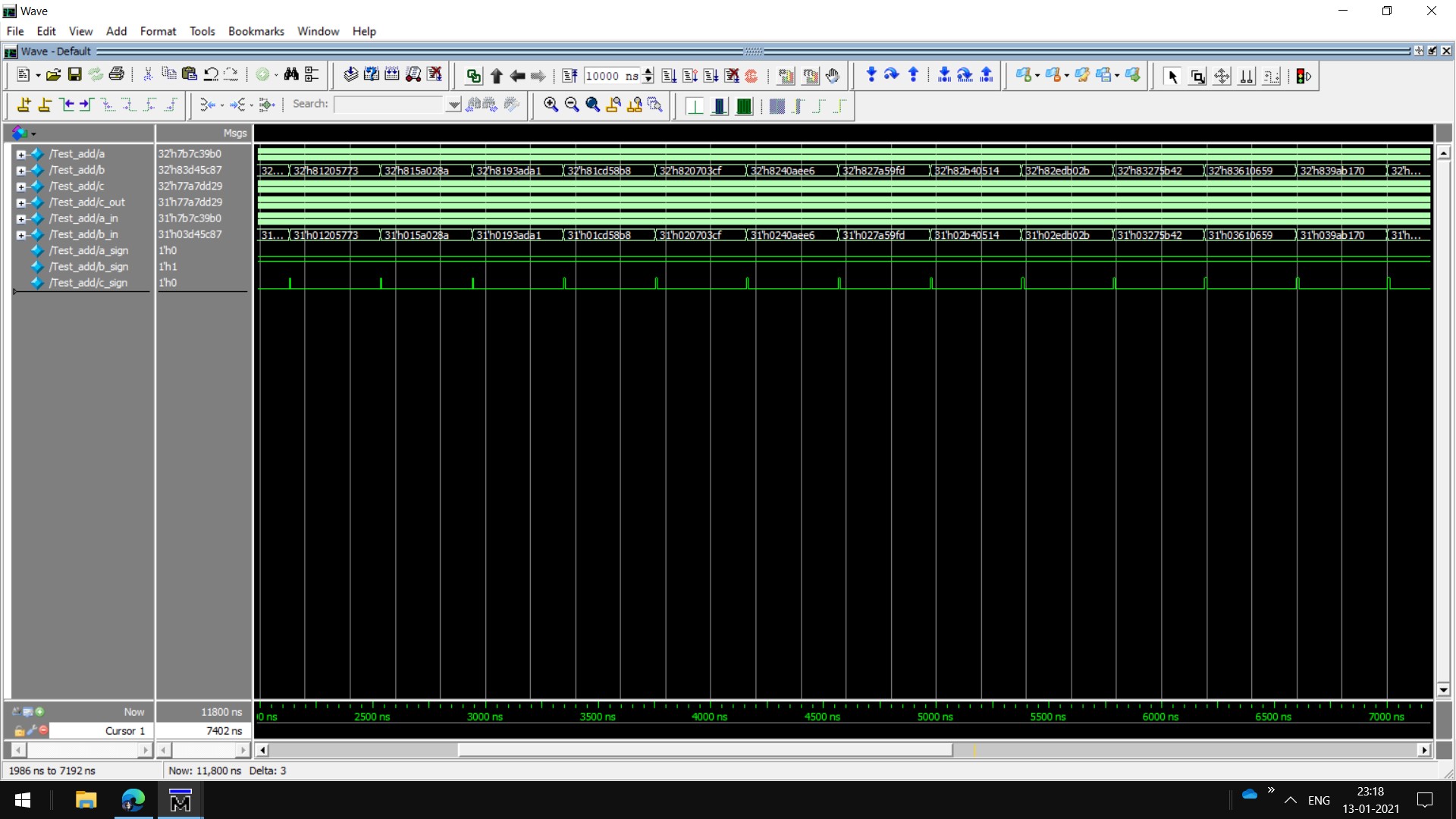

32 Bit Adder

32 Bit Adder

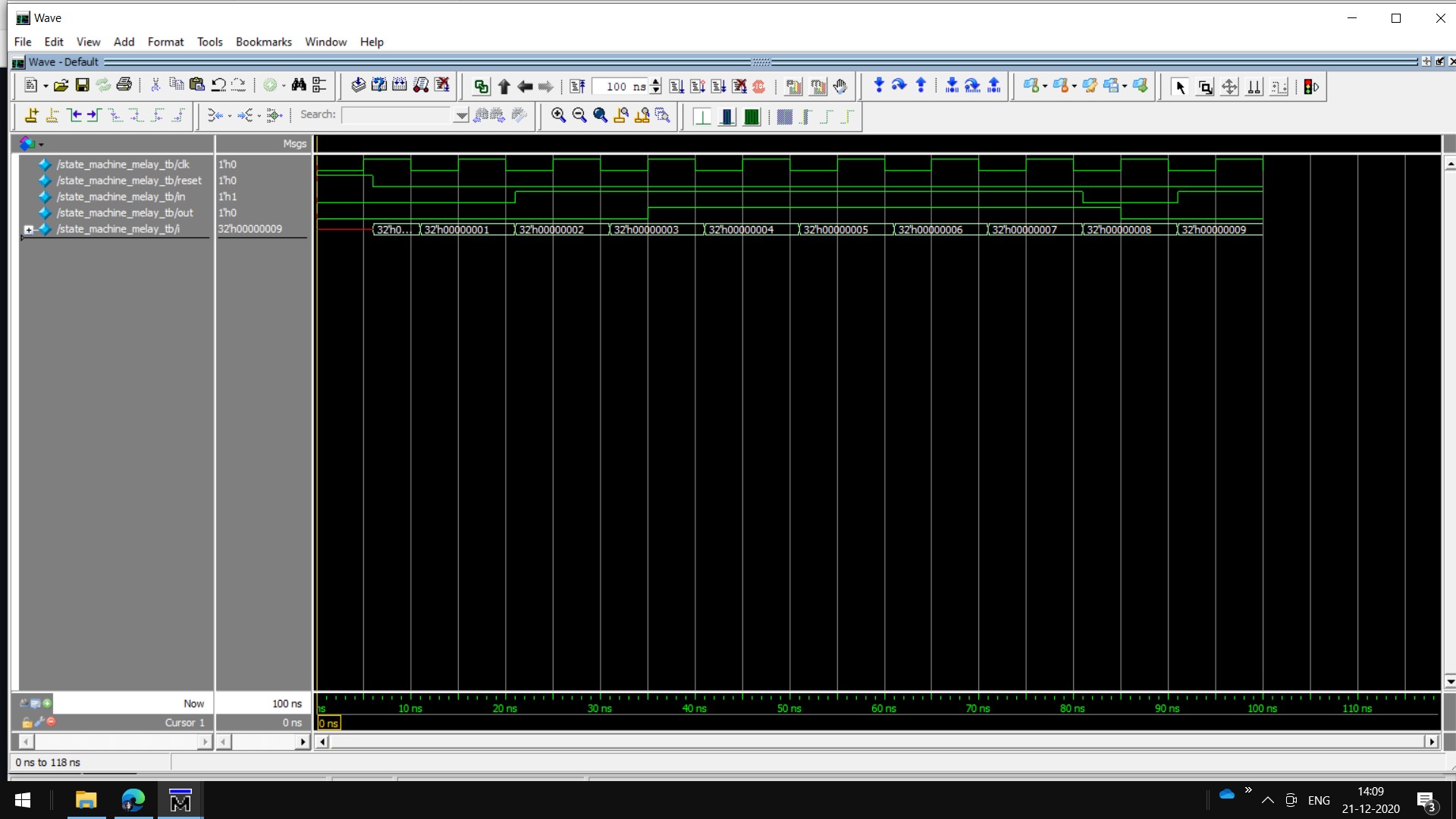

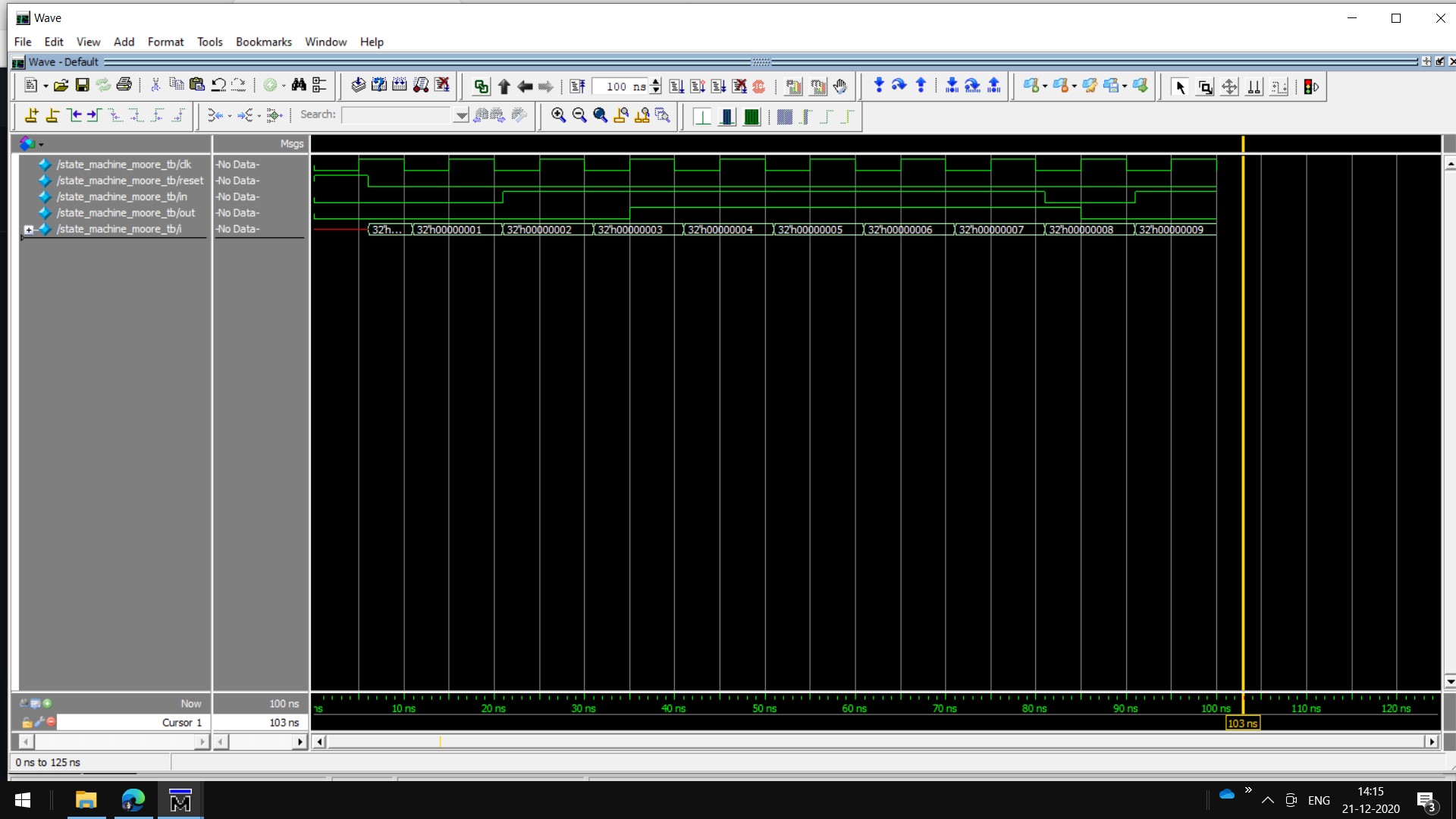

Mealy State Machine for sequence detection

Mealy State Machine for sequence detection

Moore State Machine for sequence detection

Moore State Machine for sequence detection

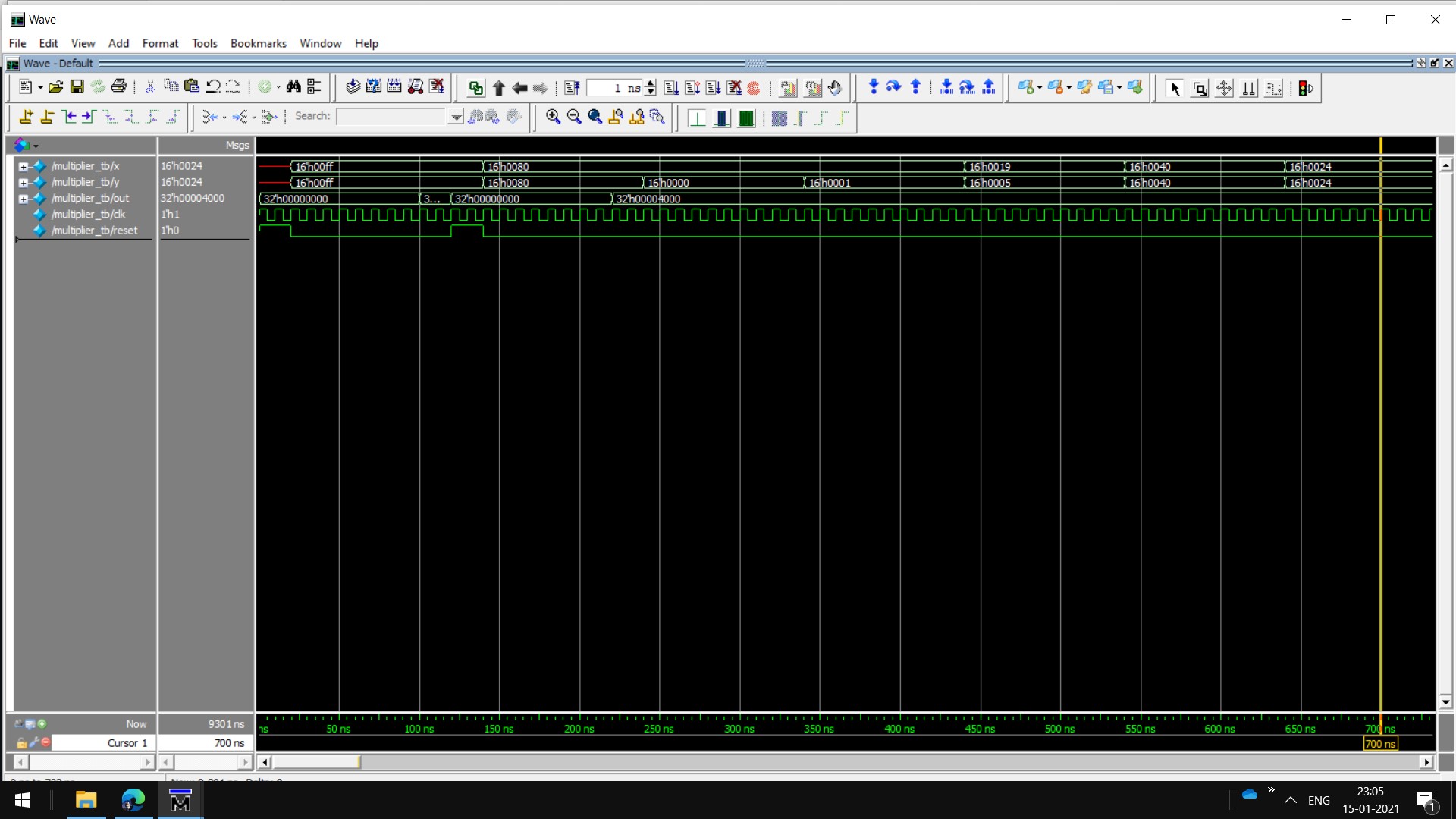

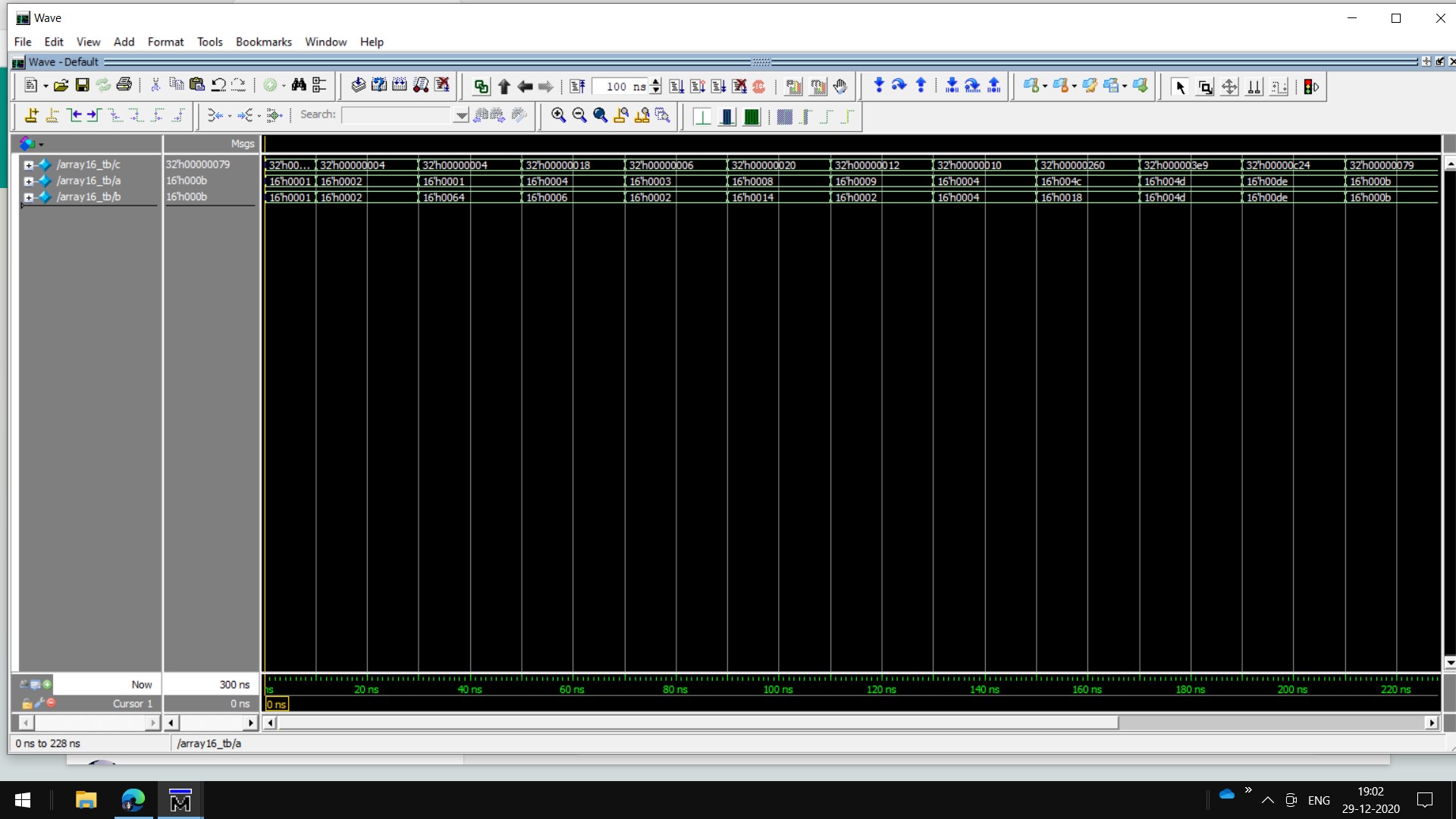

Array Multiplier

Array Multiplier

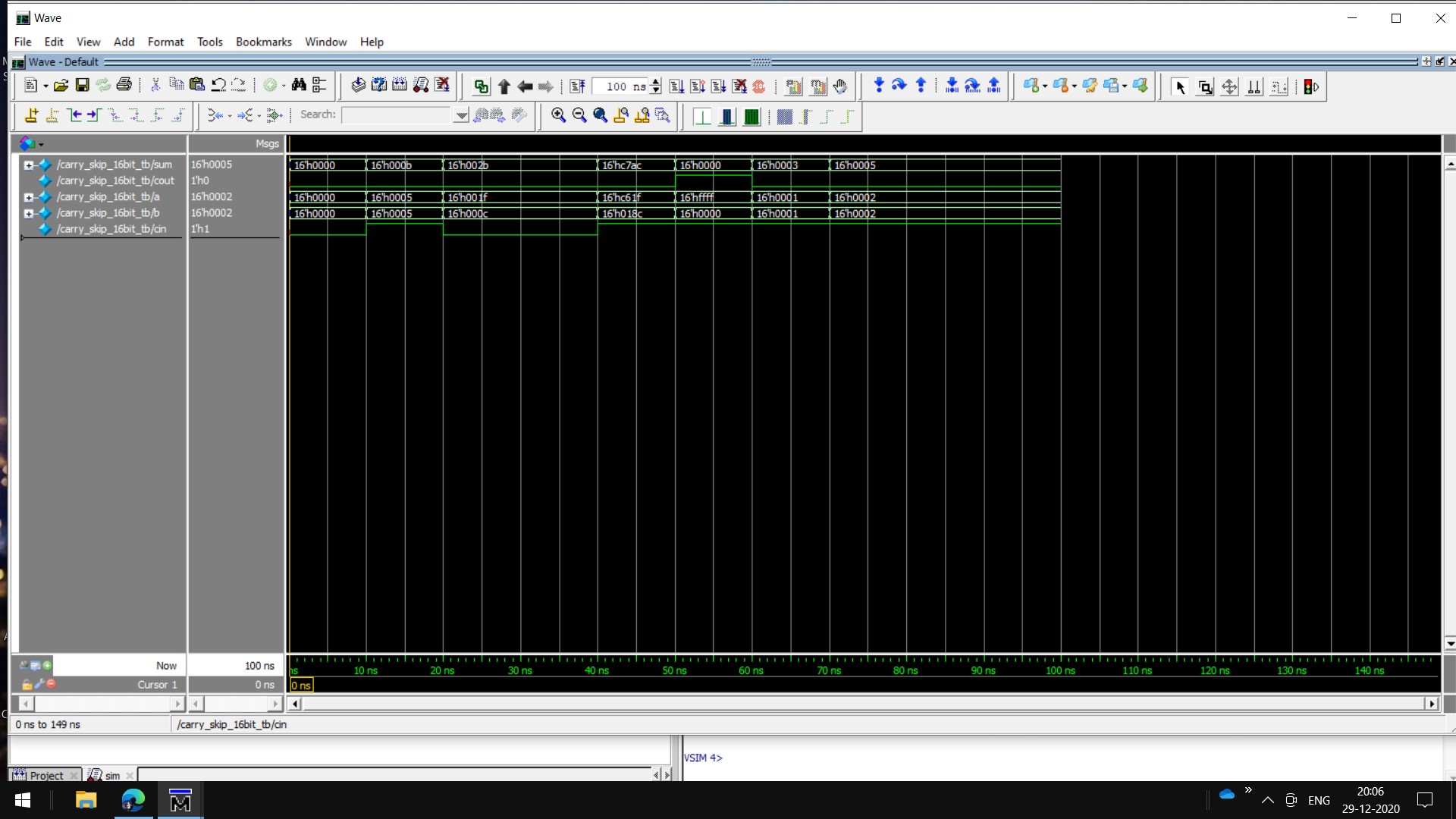

Carry Skip Adder

Carry Skip Adder

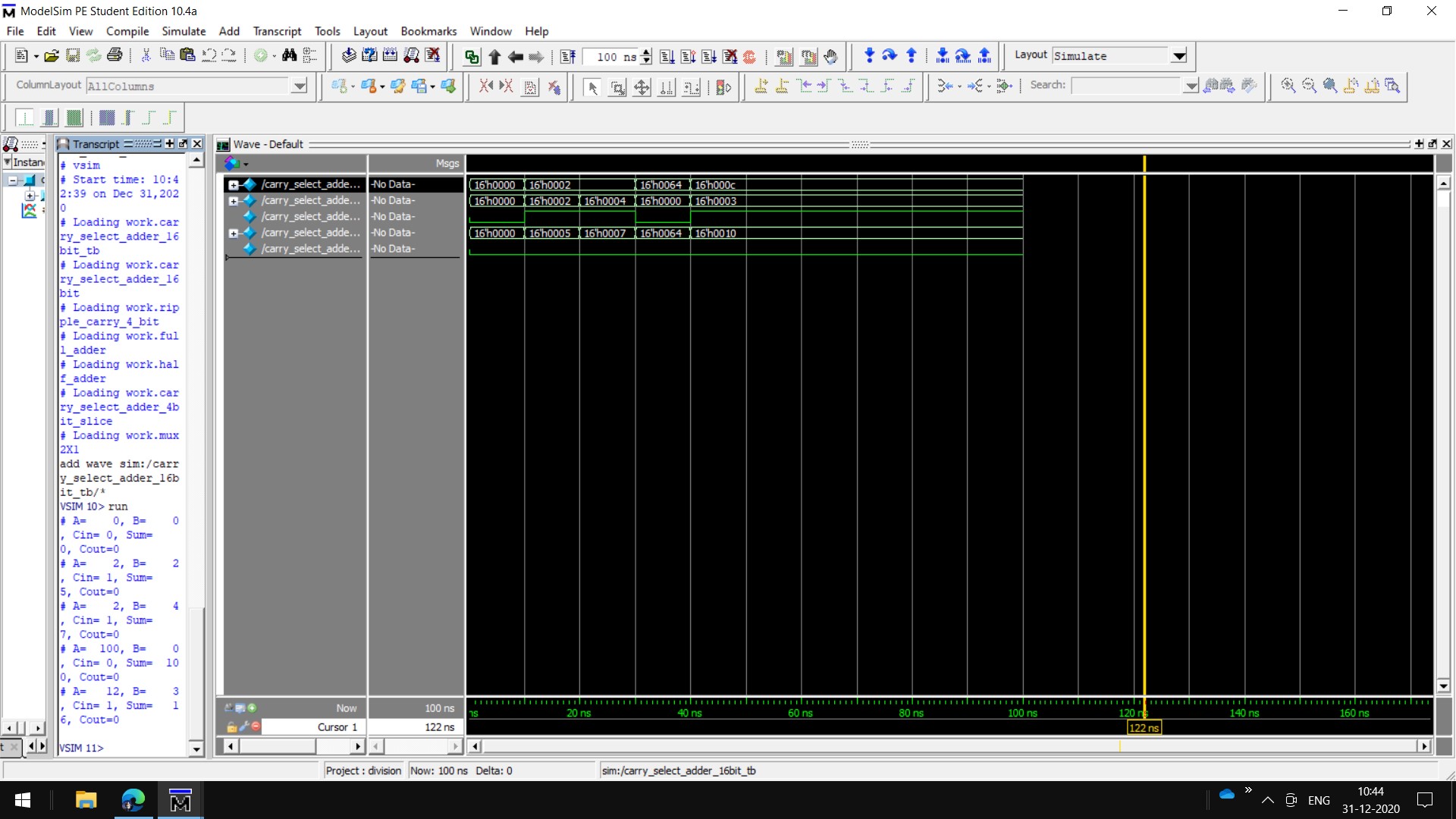

Carry Select Adder

Carry Select Adder

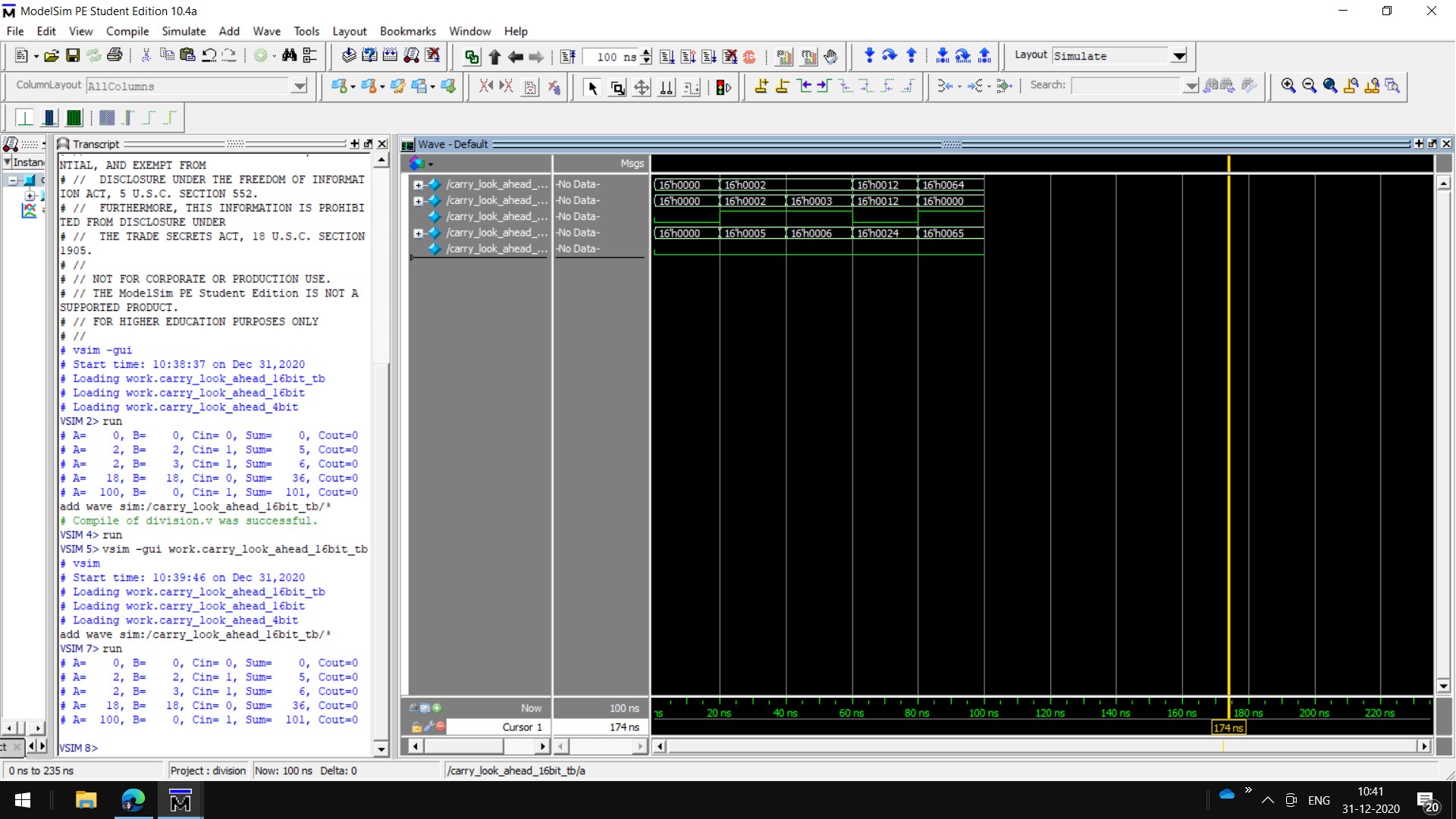

Carry Look Ahead Adder

Carry Look Ahead Adder

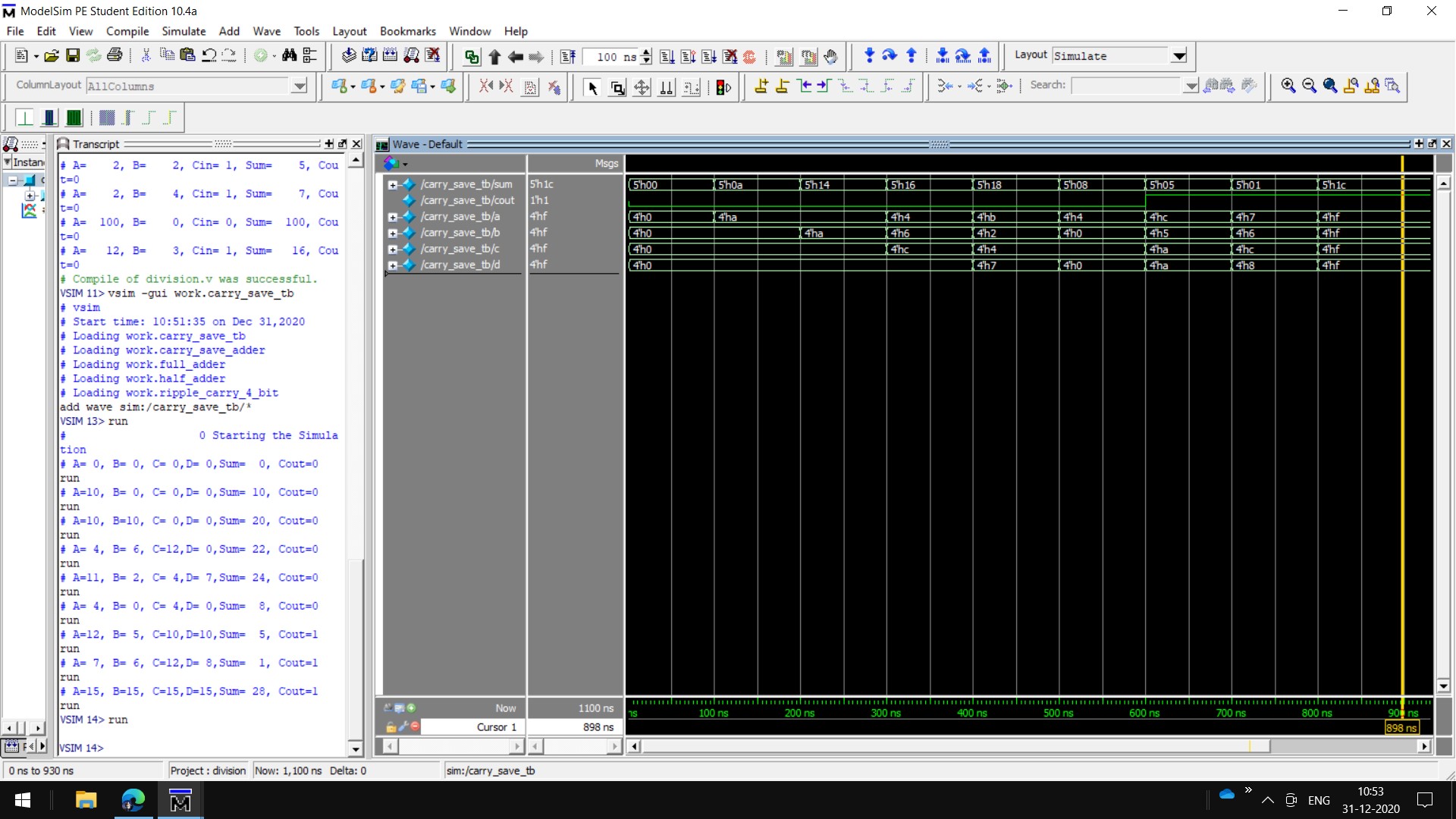

Carry Save Adder

Carry Save Adder

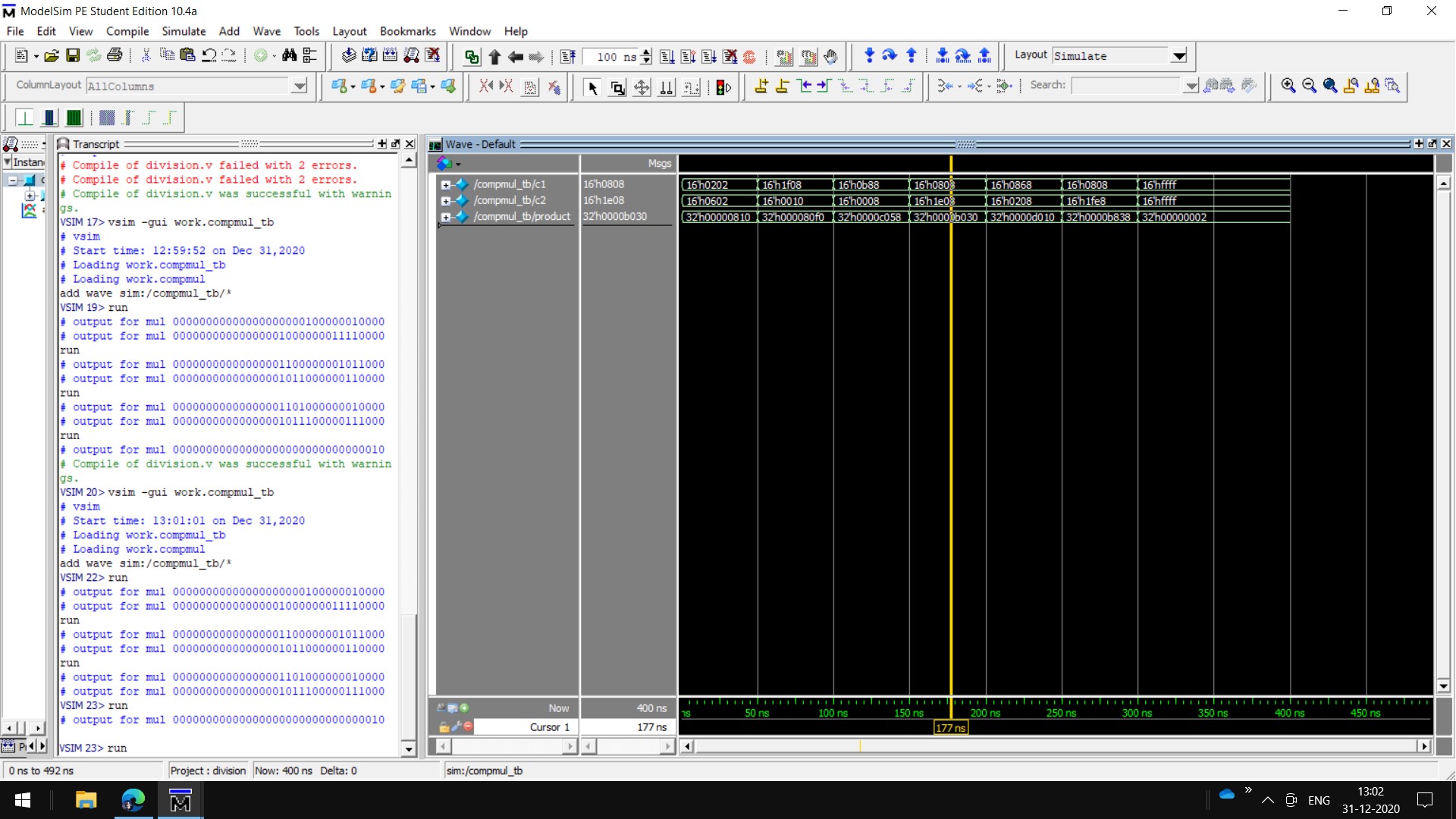

Complex Multiplier

Complex Multiplier

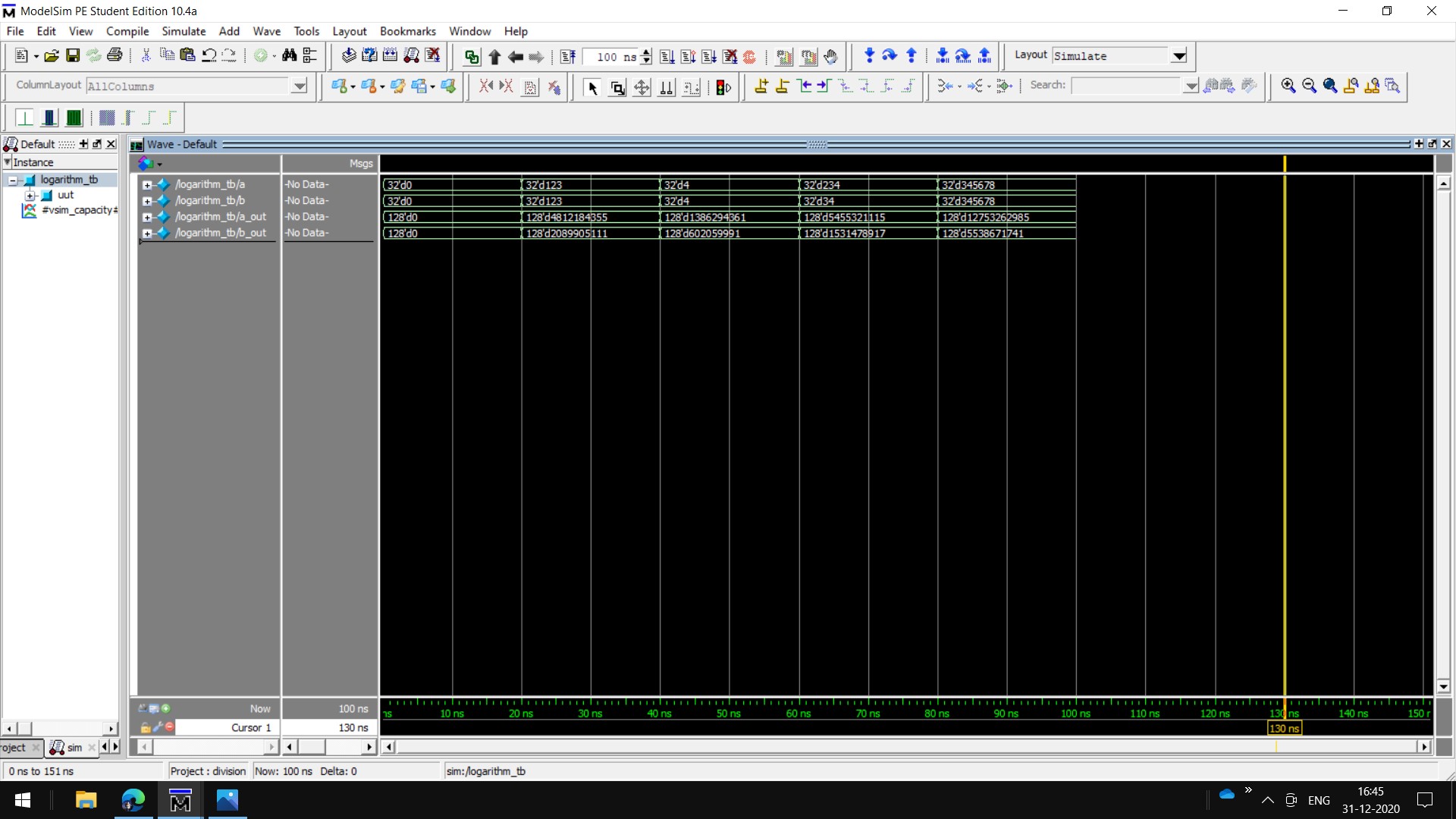

Logarithm Implementation

Logarithm Implementation

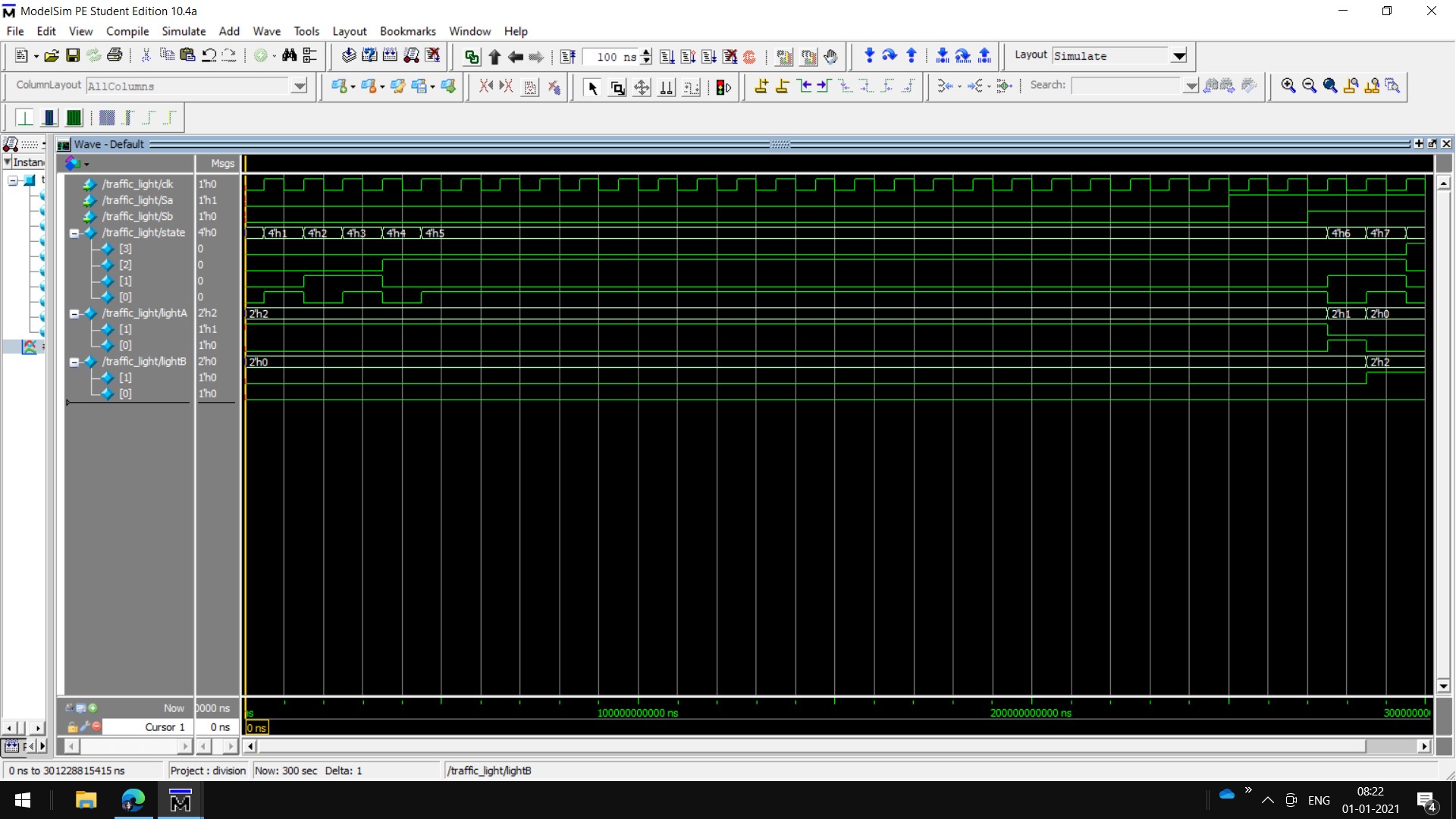

Traffic_Light_Controller

Traffic_Light_Controller

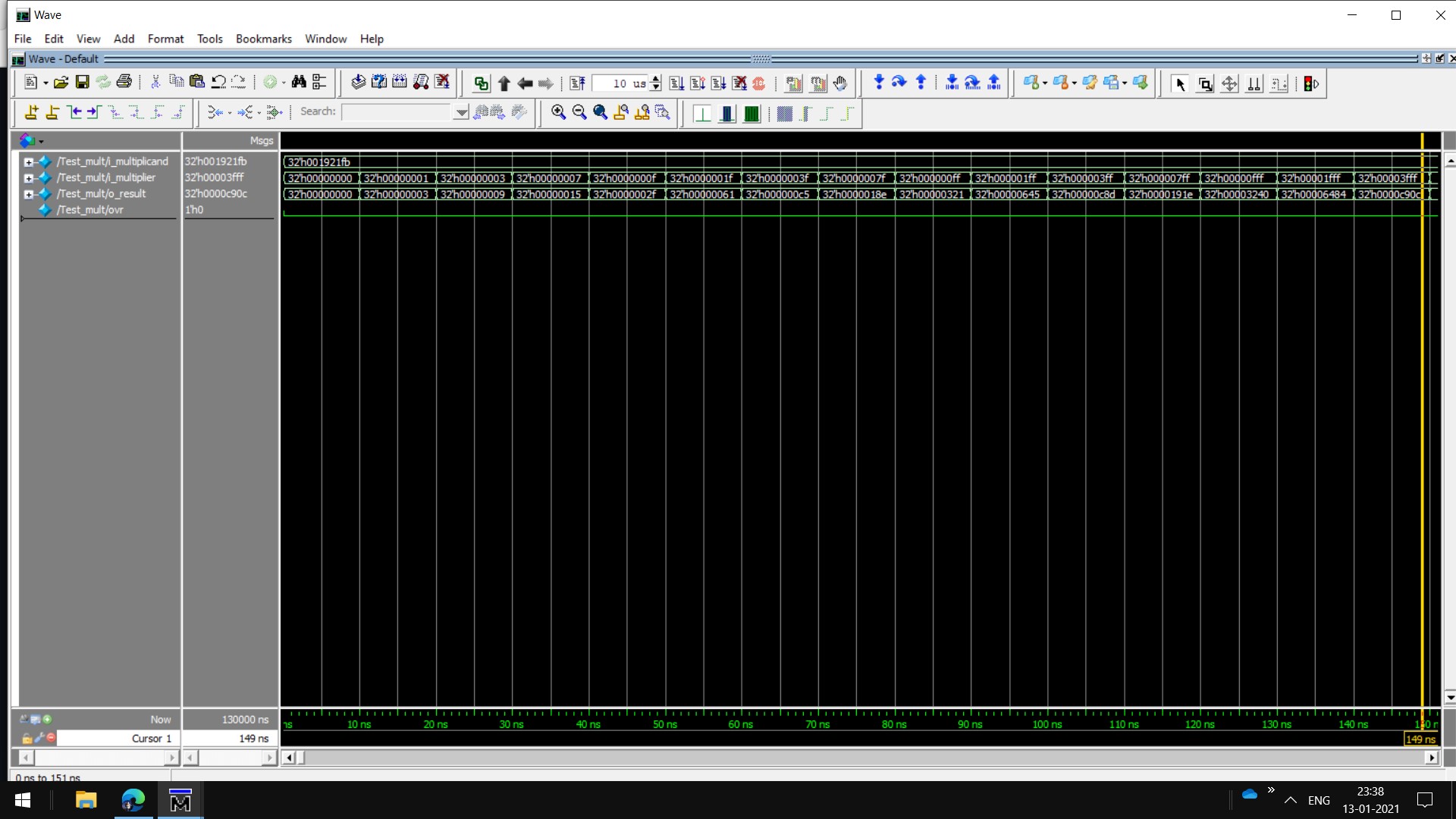

Shift and Add Binary Multiplier

Shift and Add Binary Multiplier

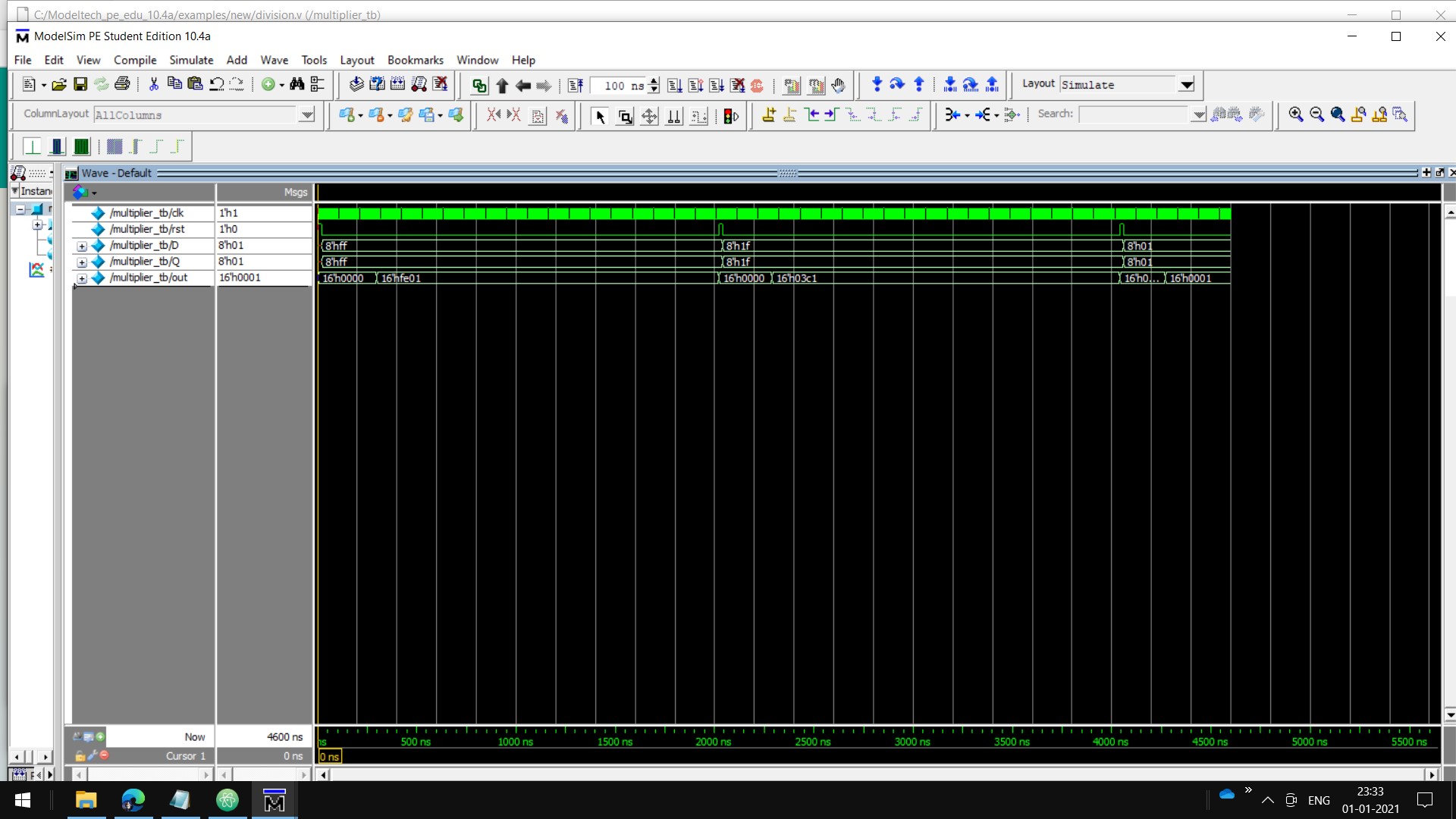

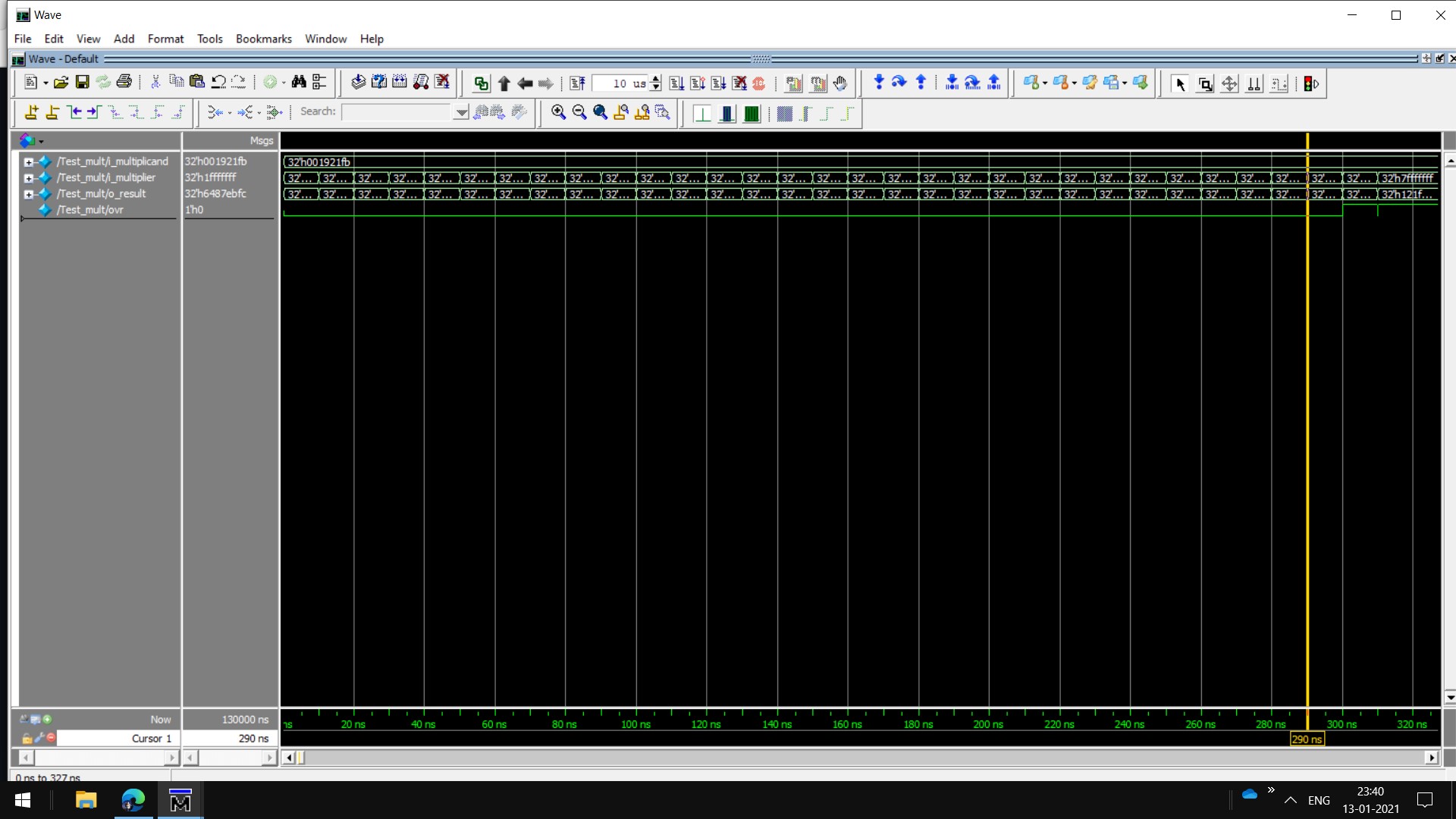

Sequential Multiplier

Sequential Multiplier

Fixed Point Adder

Fixed Point Adder

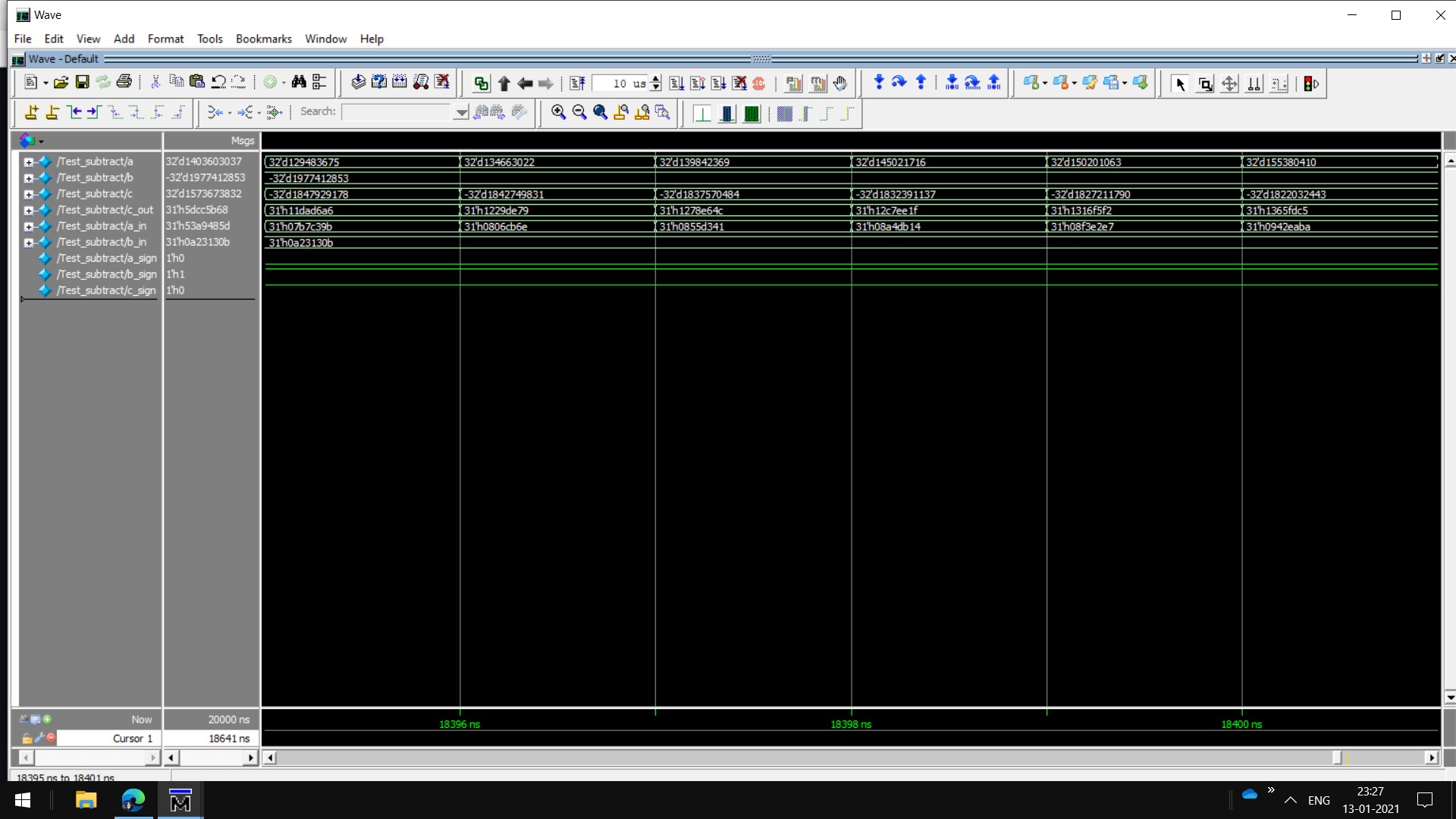

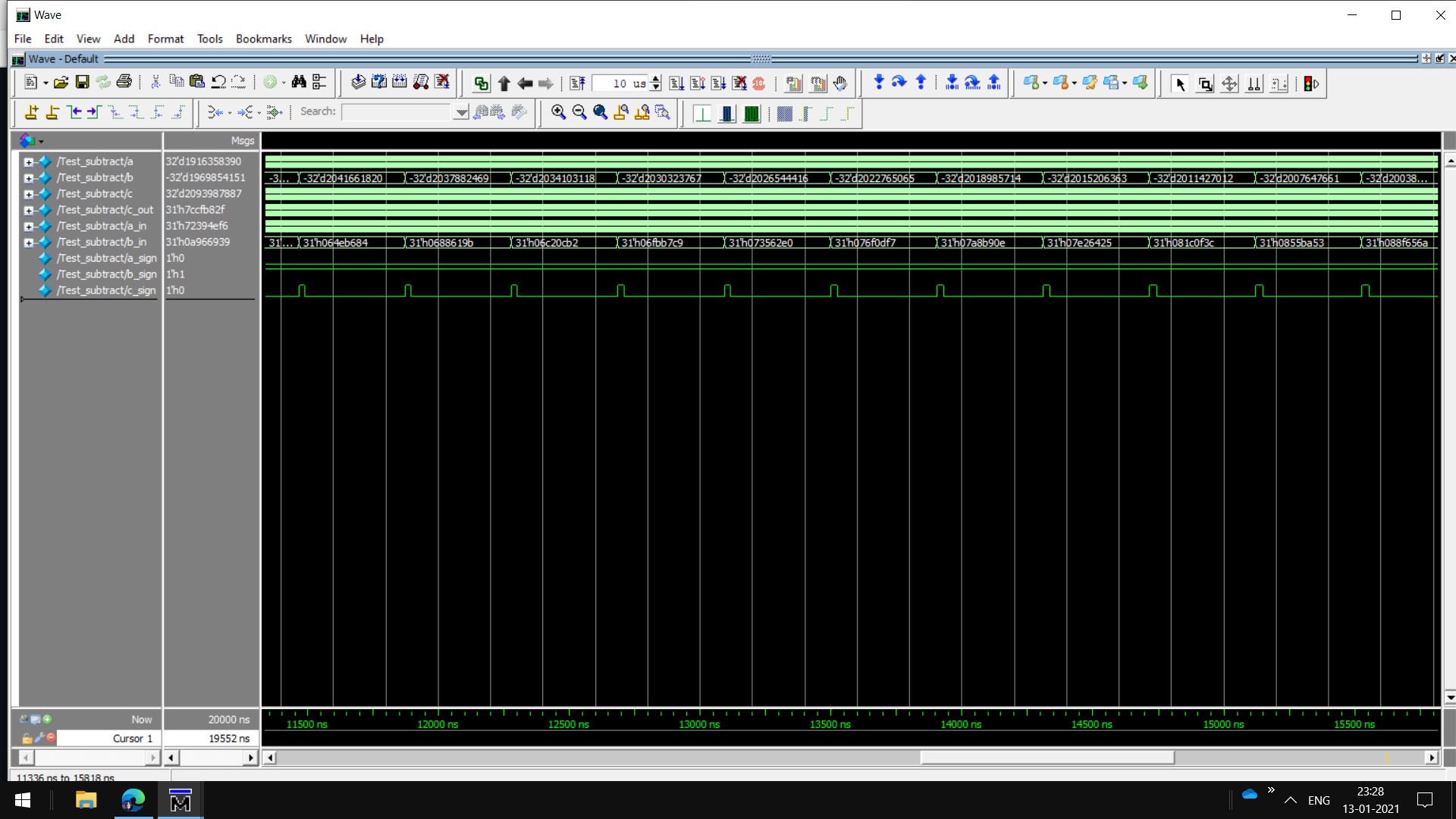

Fixed Point Subtractor

Fixed Point Subtractor

Fixed Point Multiplier

Fixed Point Multiplier

Fixed Point Divider

Fixed Point Divider

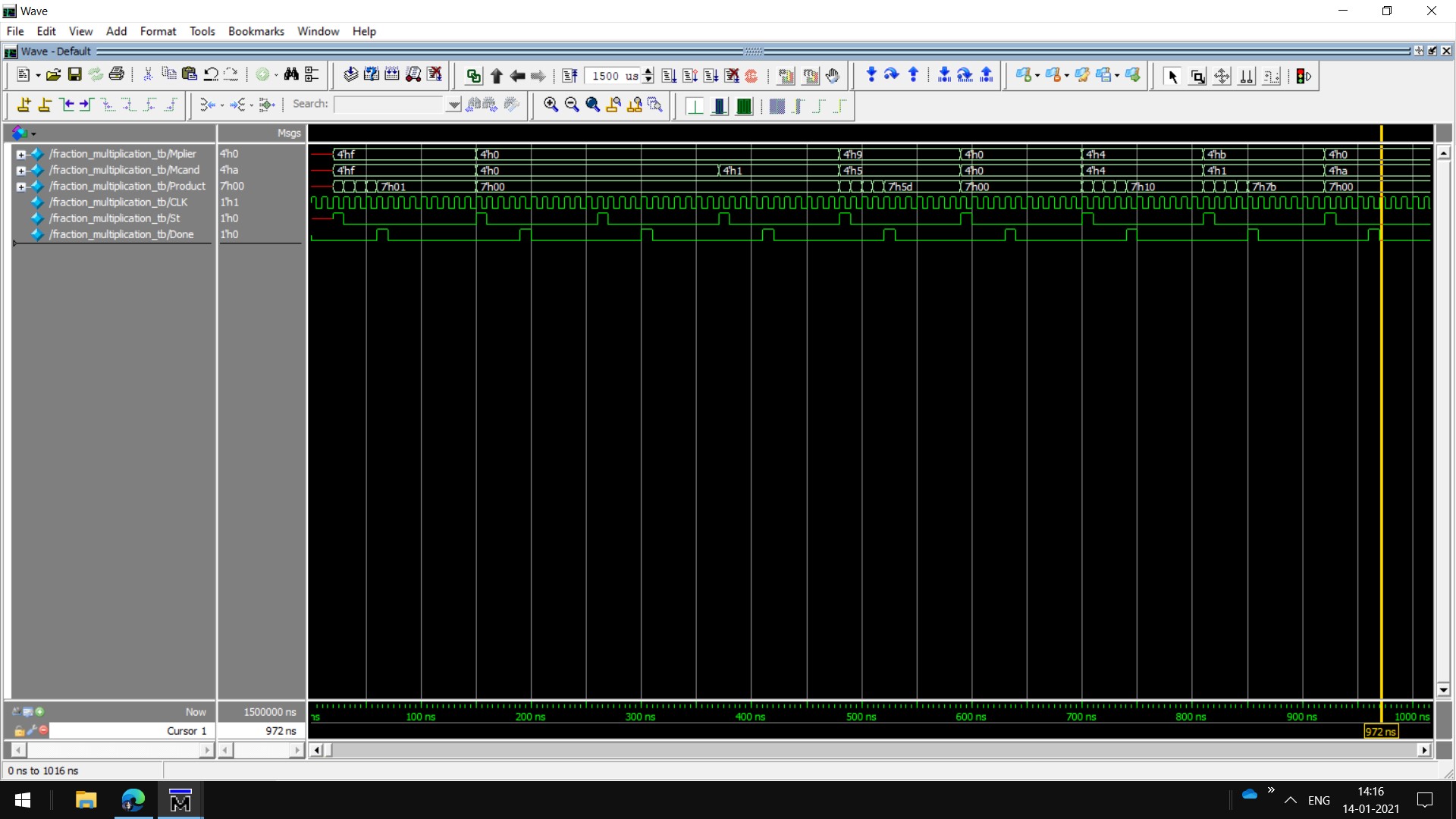

Fraction_Multiplier

Fraction_Multiplier

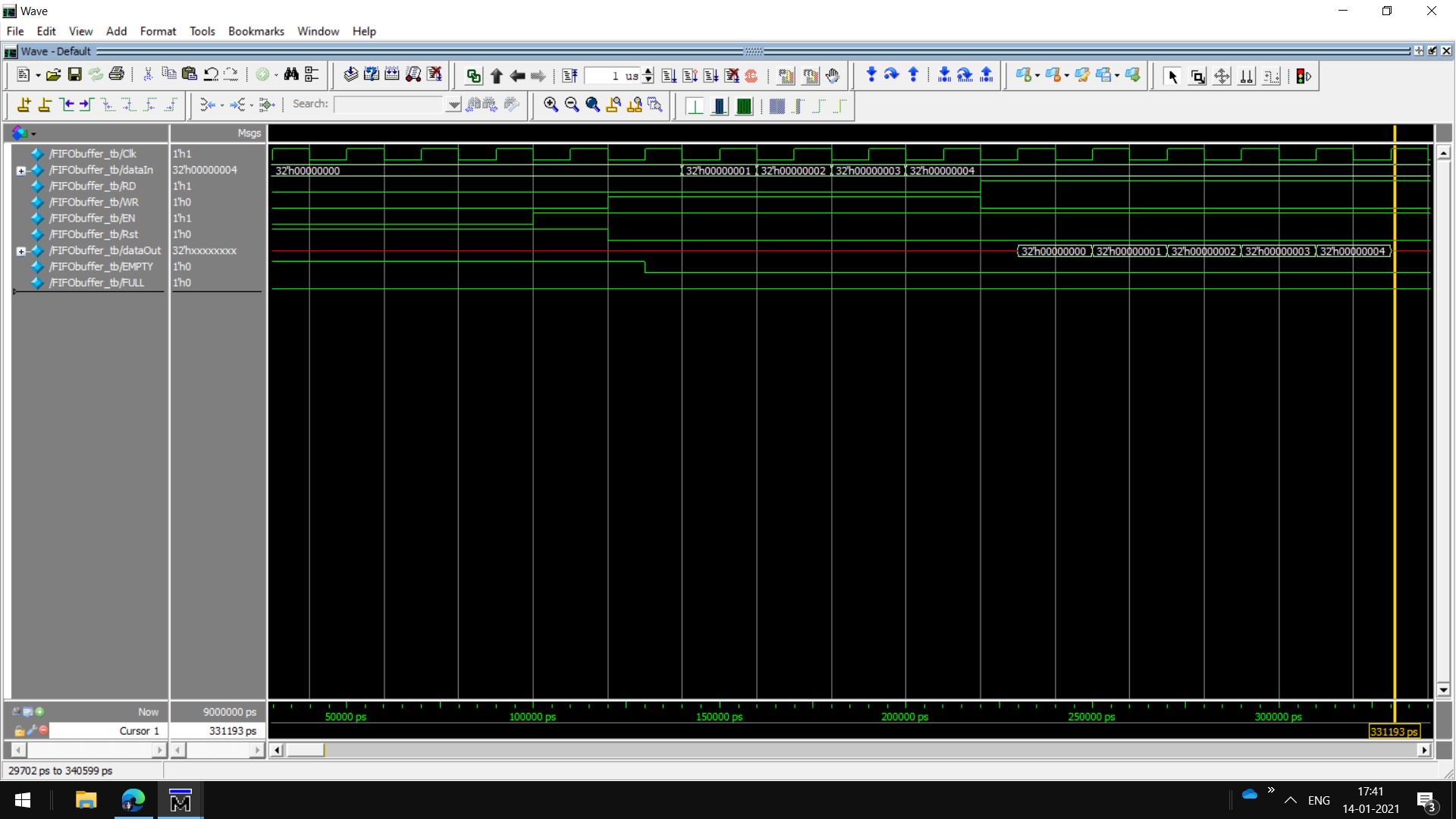

FIFO

FIFO

LFSR and CFSR

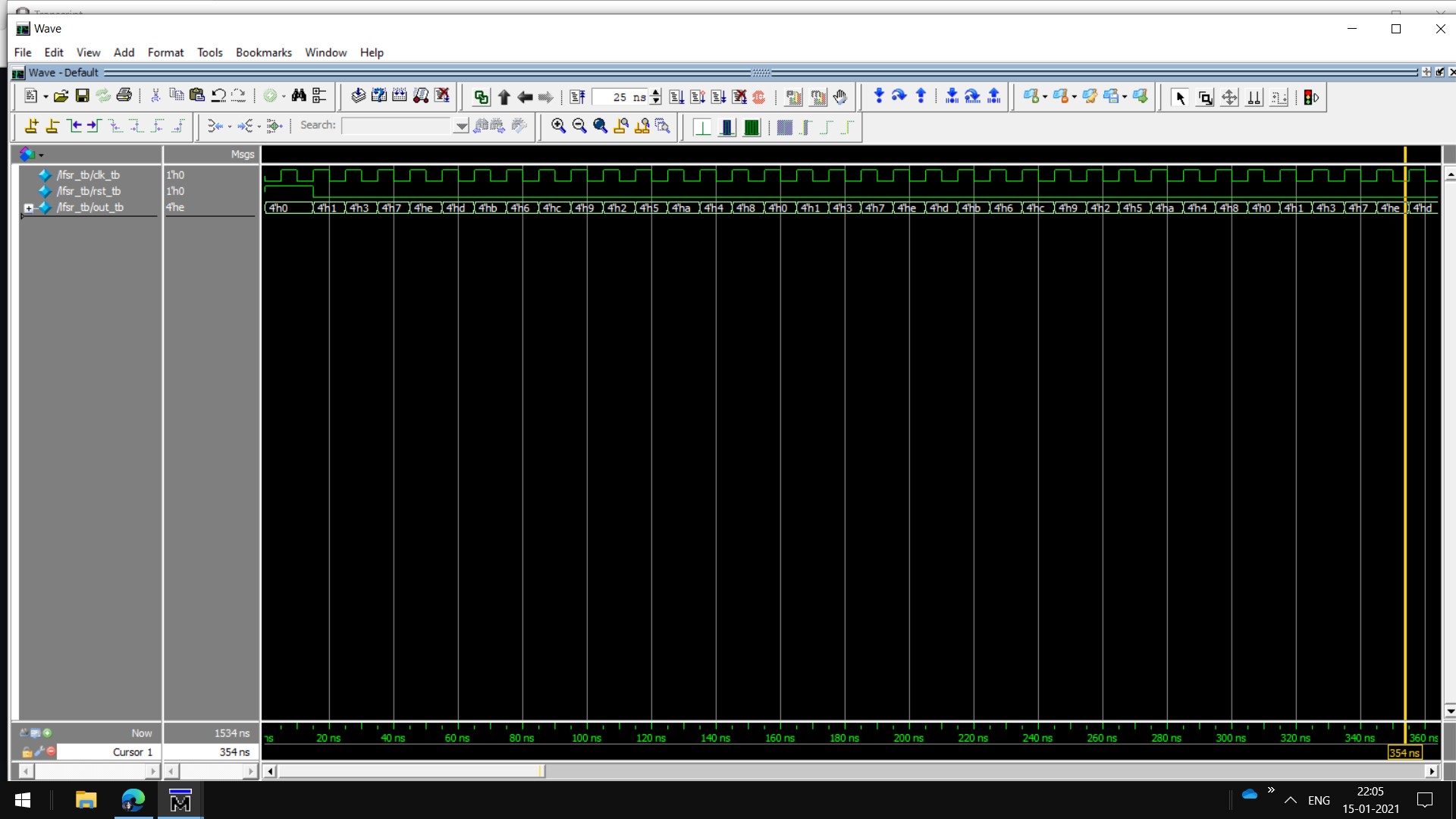

LFSR

LFSR and CFSR

LFSR

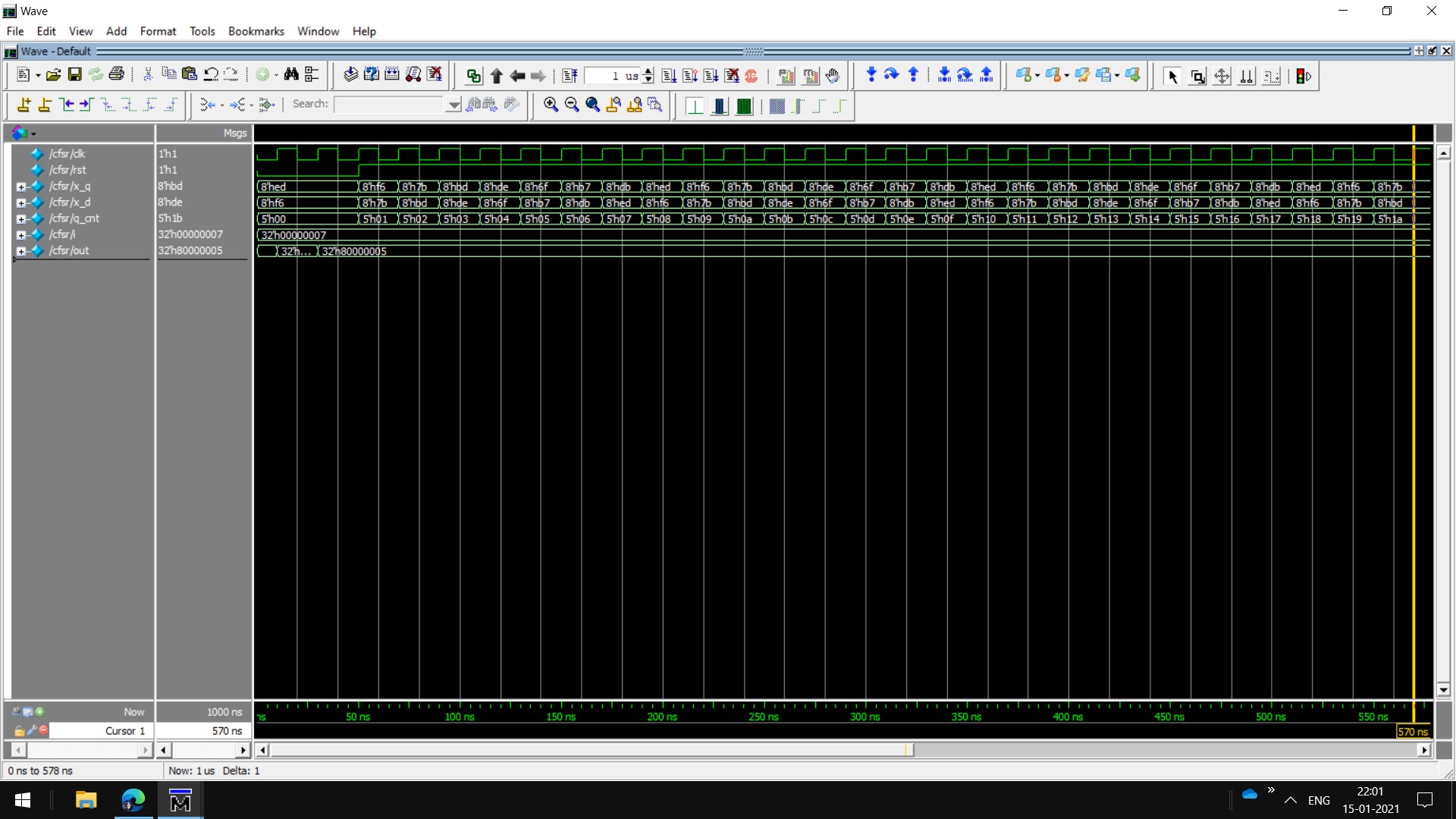

CFSR

CFSR

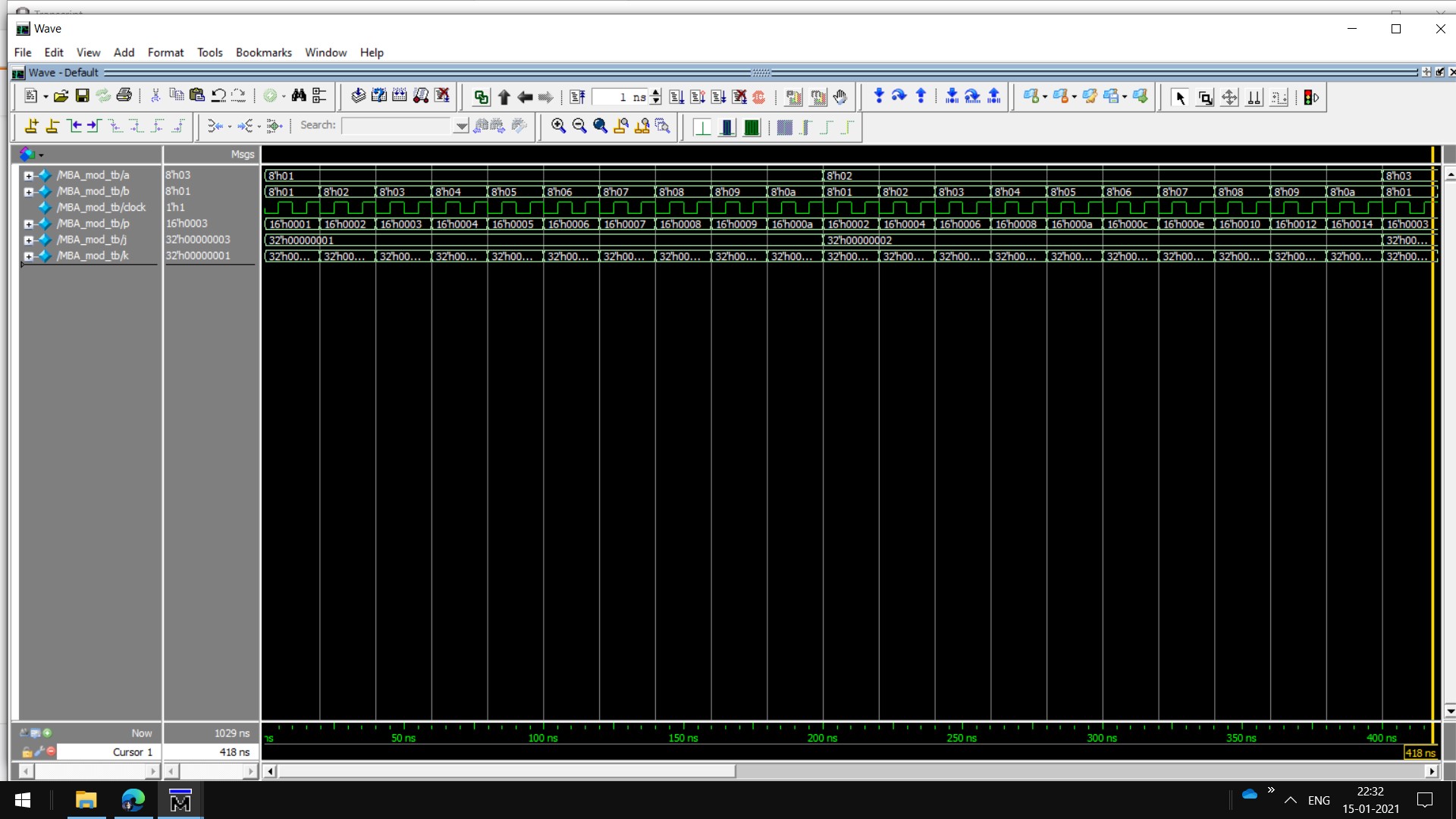

Modified Booth Multiplication

Modified Booth Multiplication

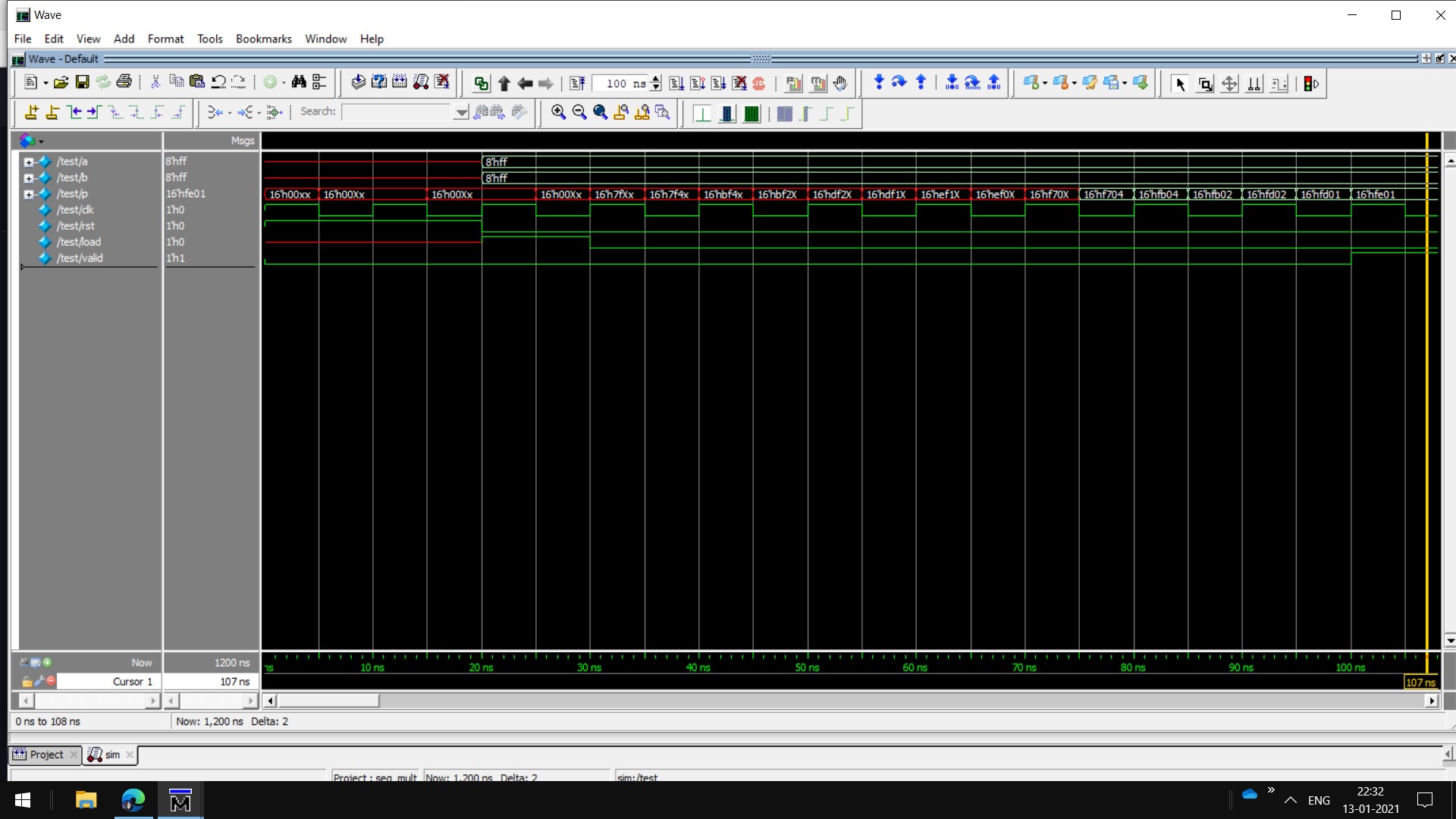

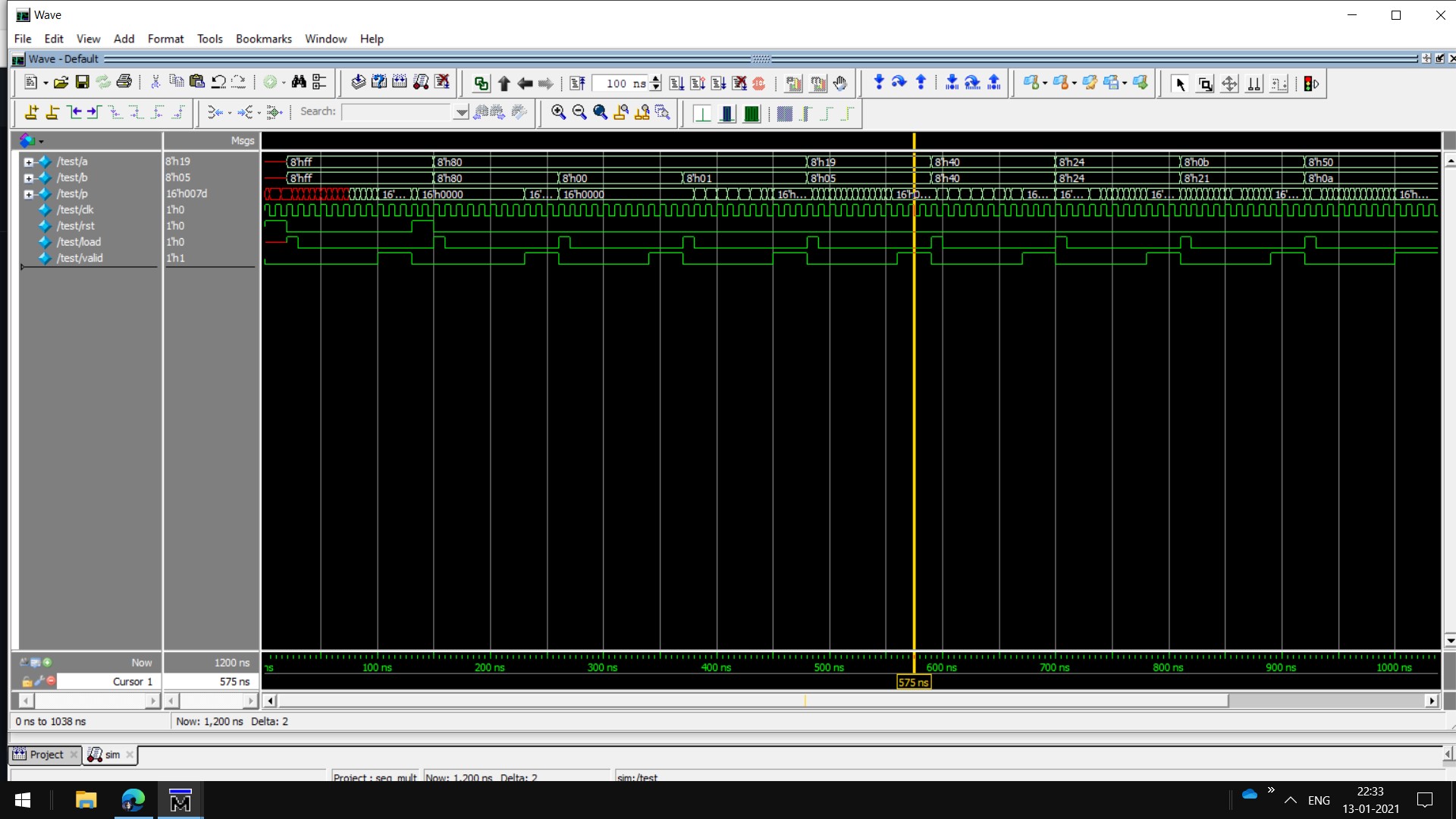

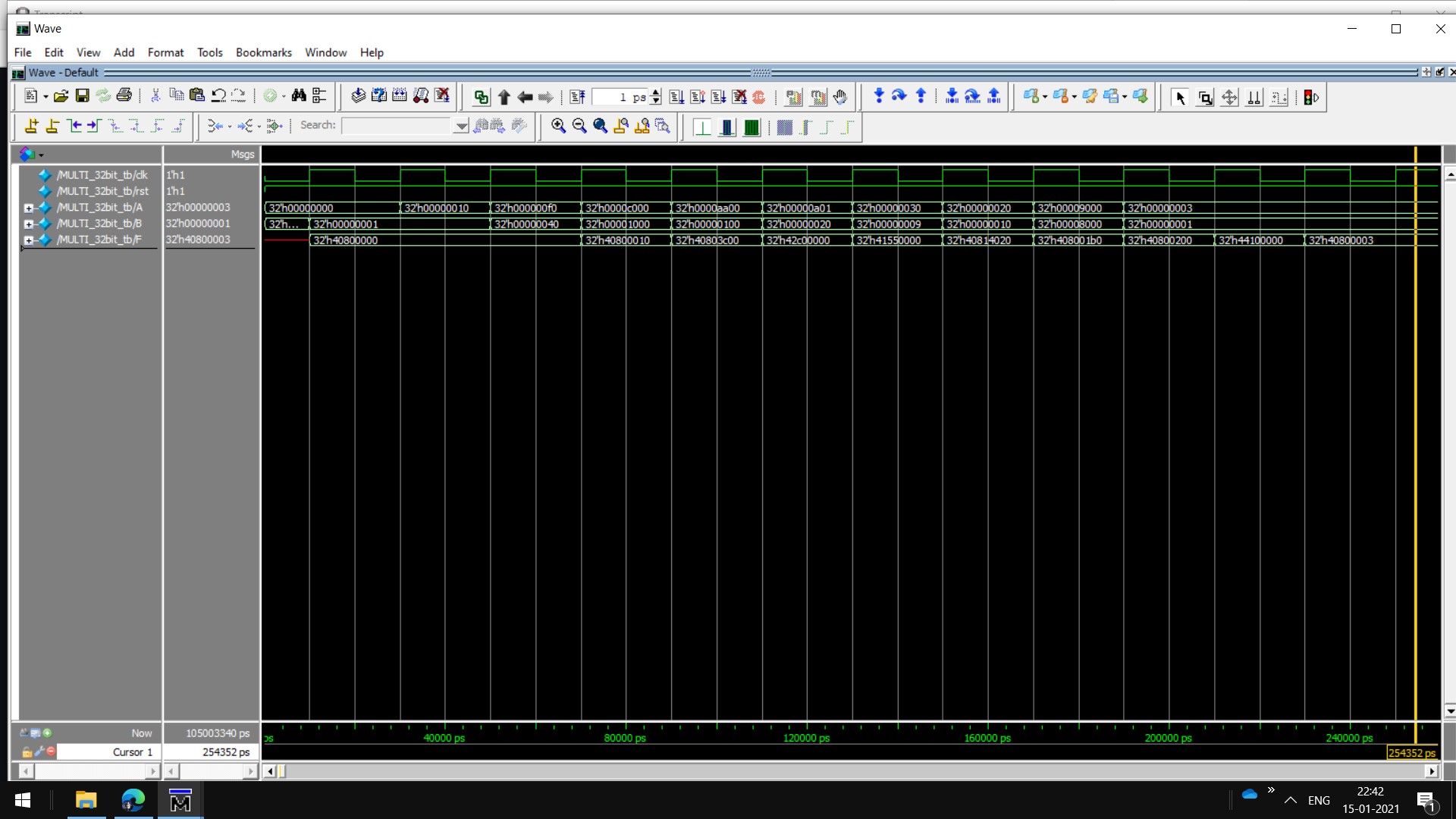

Pipelined Multiplier

Pipelined Multiplier

High Radix Multiplication

High Radix Multiplication