A new chip placement method based on visual representation learning.

Lai, Yao, Yao Mu, and Ping Luo. "Maskplace: Fast chip placement via reinforced visual representation learning." Advances in Neural Information Processing Systems 35 (2022): 24019-24030. (NeurIPS 2022, spotlight)

You can start easily by using the following script.

cd maskplace

python PPO2.py

- gamma Decay factor.

- seed Random seed.

- disable_tqdm Whether to disable the progress bar.

- lr Learning rate.

- log-interval Interval between training status logs.

- pnm Number of place modules for each placement trajectory.

- benchmark Circuit benchmark.

- soft_coefficient Whether to constriant the actions based on the wiremask.

- batch_size Batch size.

- is_test Testing mode based on the trained agent.

- save_fig Whether to save placement figures.

The repo has provided the benchmark adaptec1 and ariane. For other benchmarks, you can download them by the following the link:

http://www.cerc.utexas.edu/~zixuan/ispd2005dp.tar.xz

-

Python >= 3.9

-

Pytorch >= 1.10

- Other versions may also work, but not tested

-

gym >= 0.21.0

-

matplotlib >= 3.7.1

-

protobuf (for benchmark ariane)

If you find our paper/code useful in your research, please cite

@article{lai2022maskplace,

title={Maskplace: Fast chip placement via reinforced visual representation learning},

author={Lai, Yao and Mu, Yao and Luo, Ping},

journal={Advances in Neural Information Processing Systems},

volume={35},

pages={24019--24030},

year={2022}

}

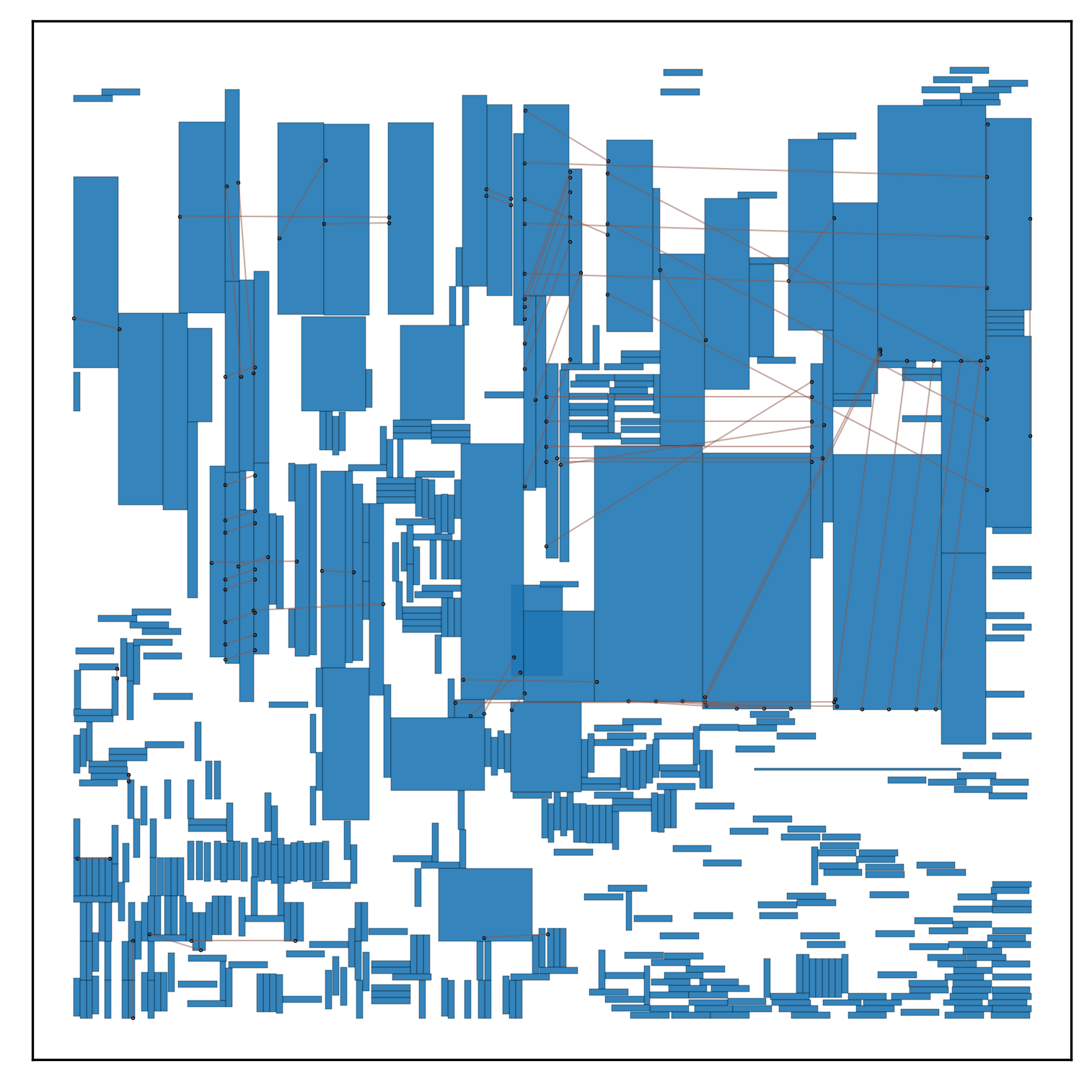

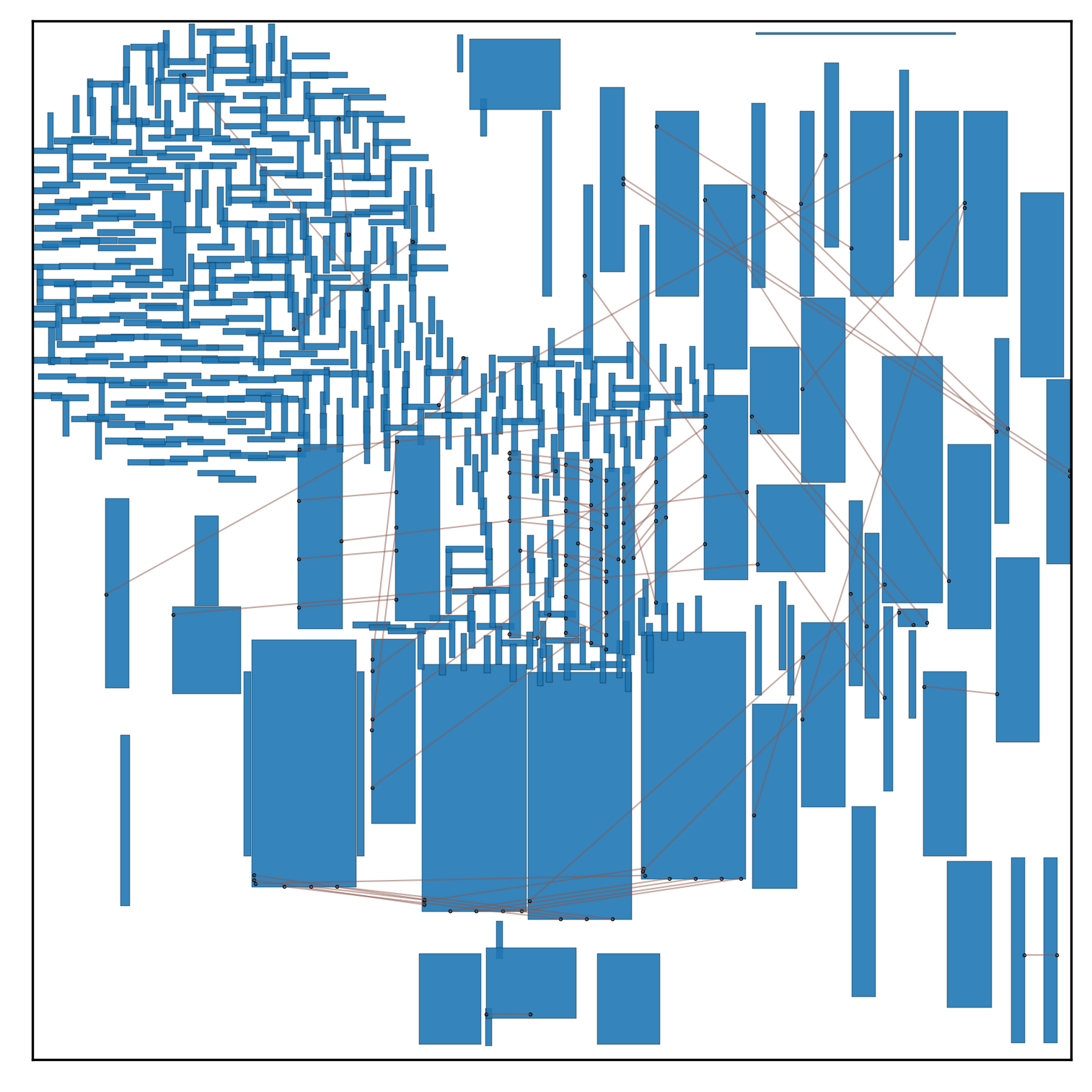

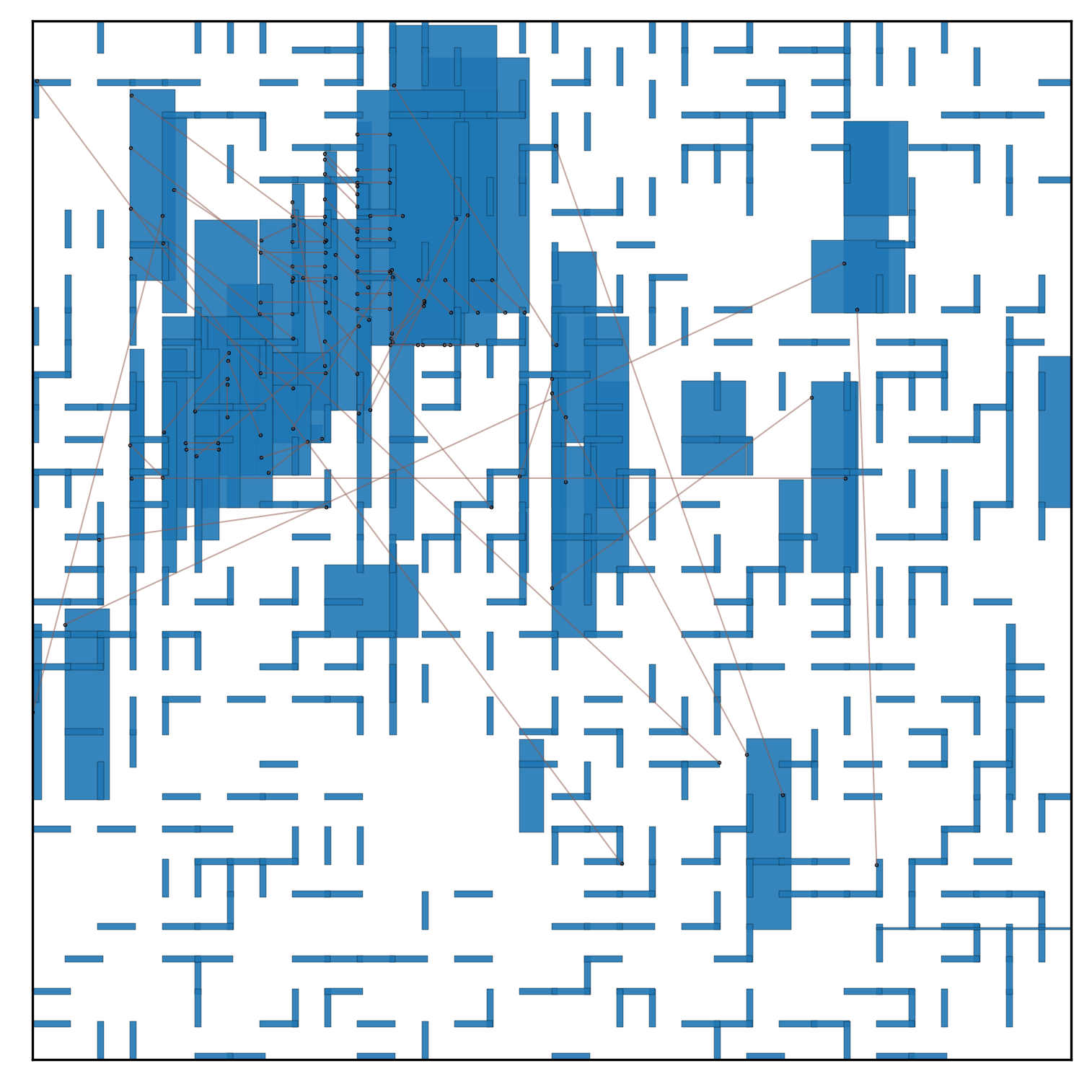

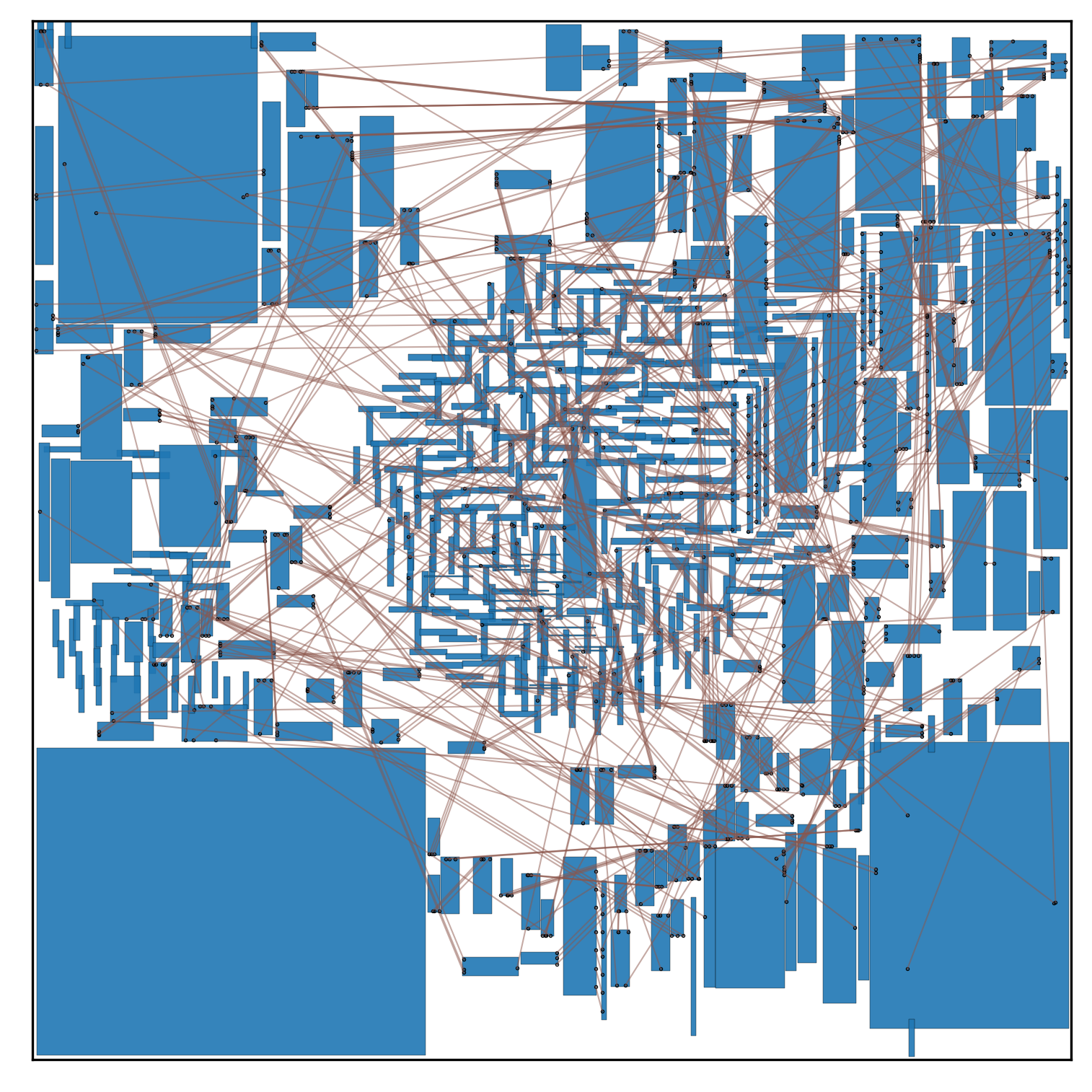

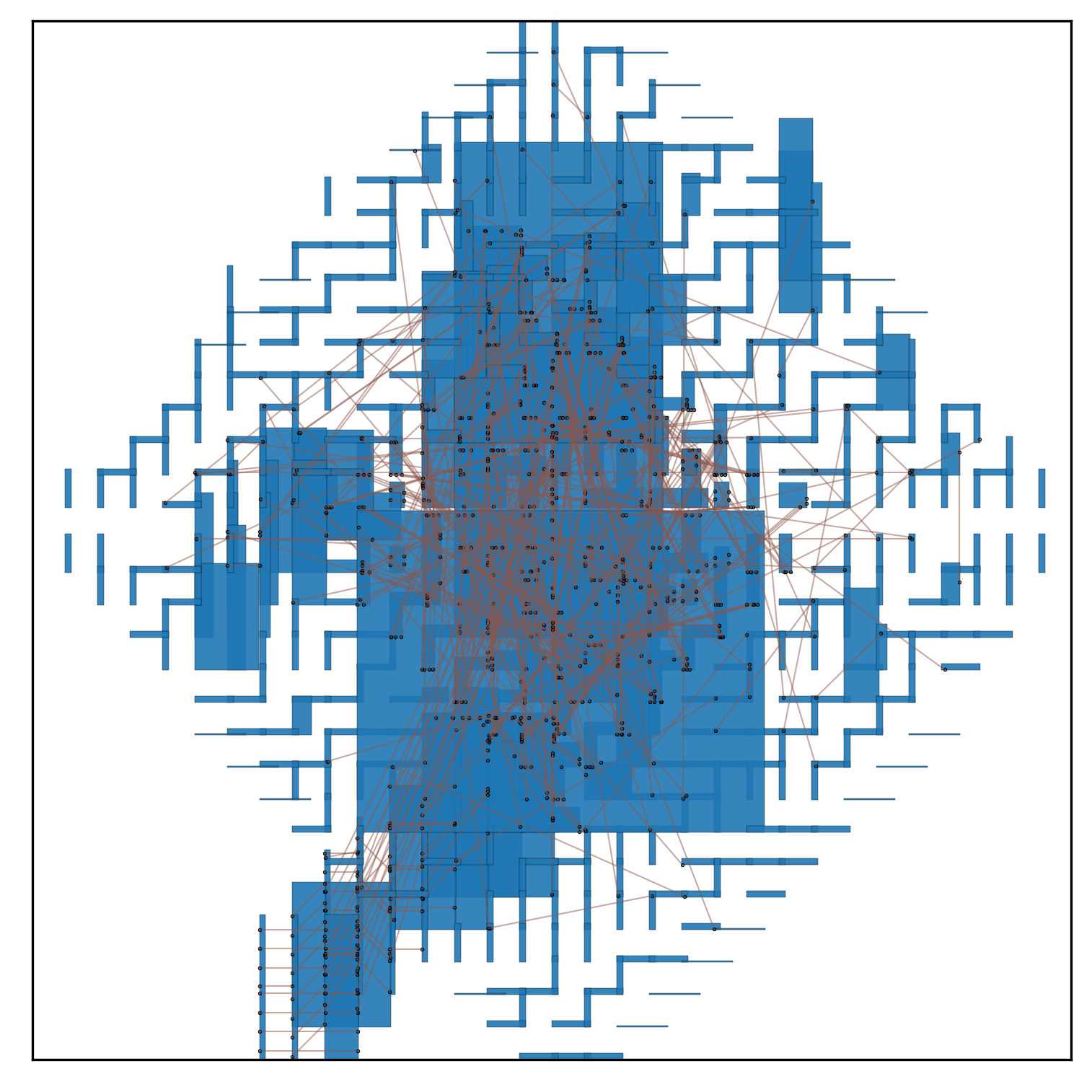

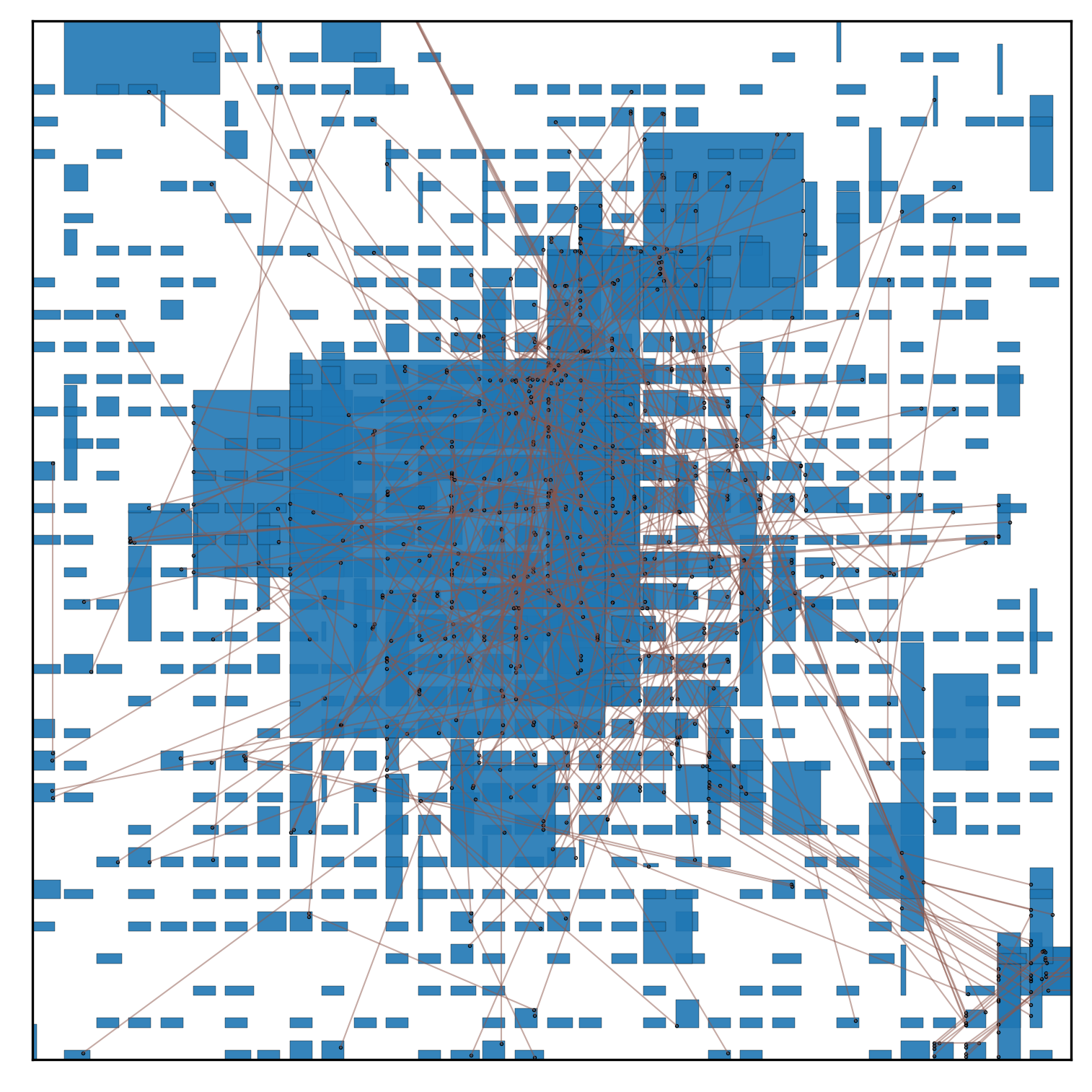

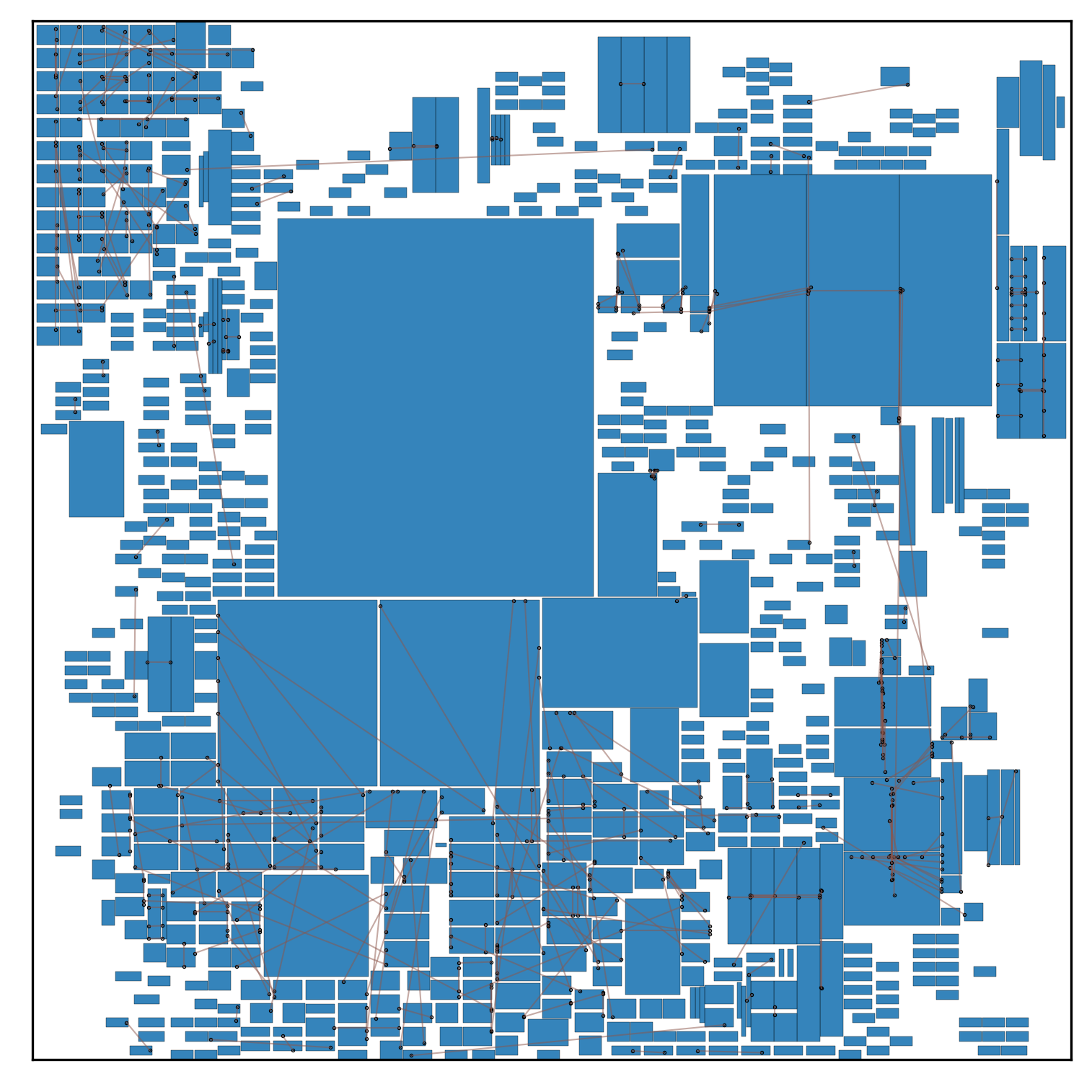

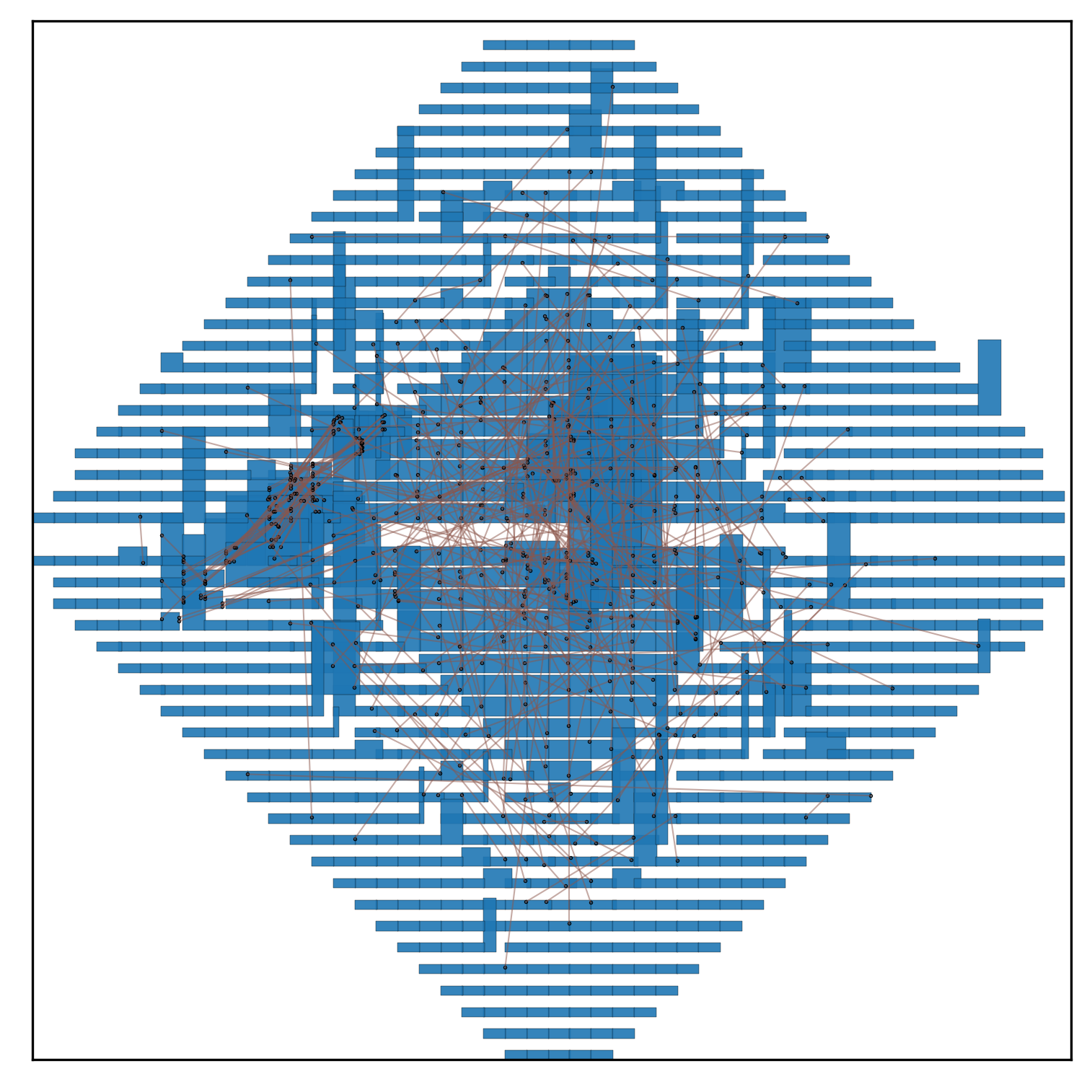

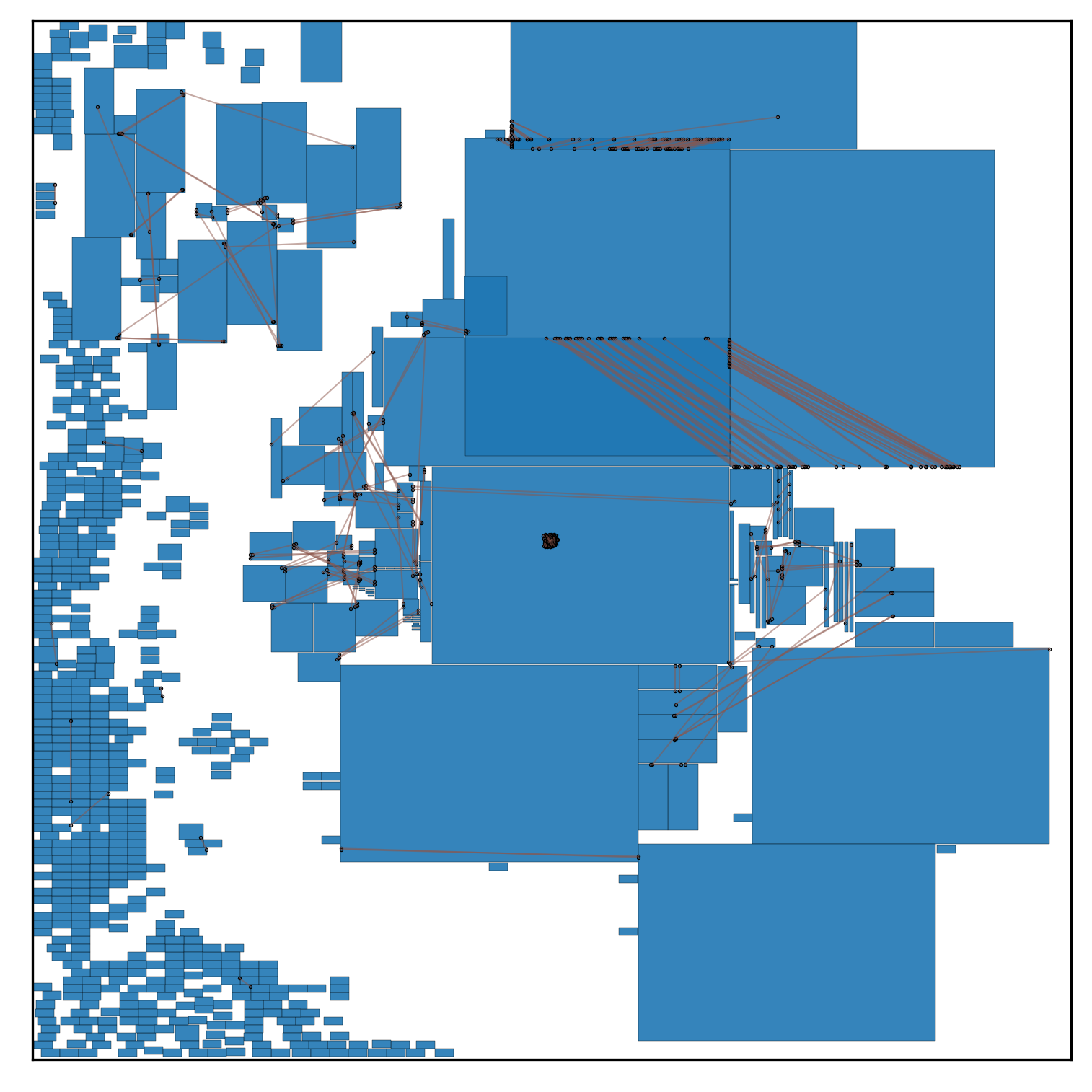

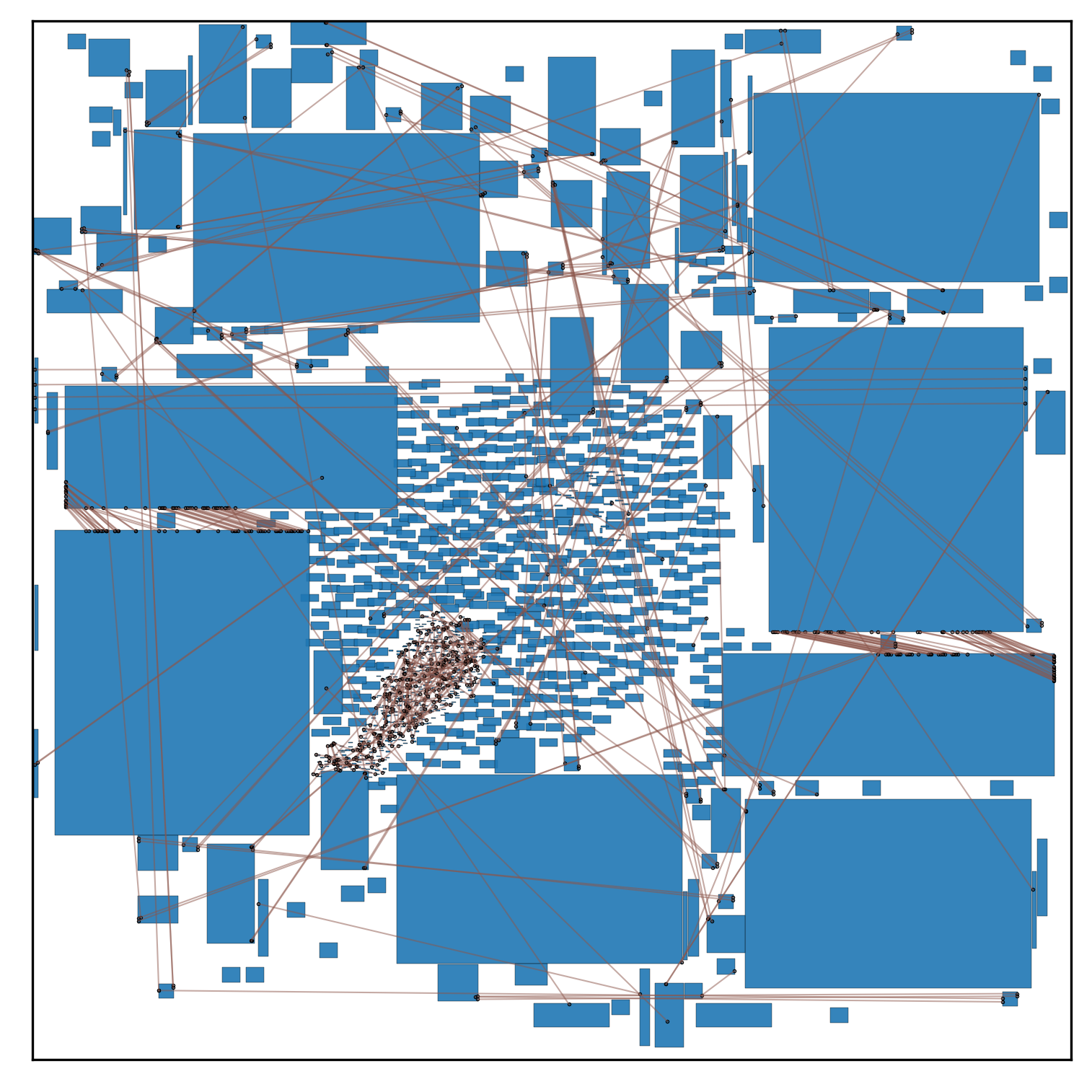

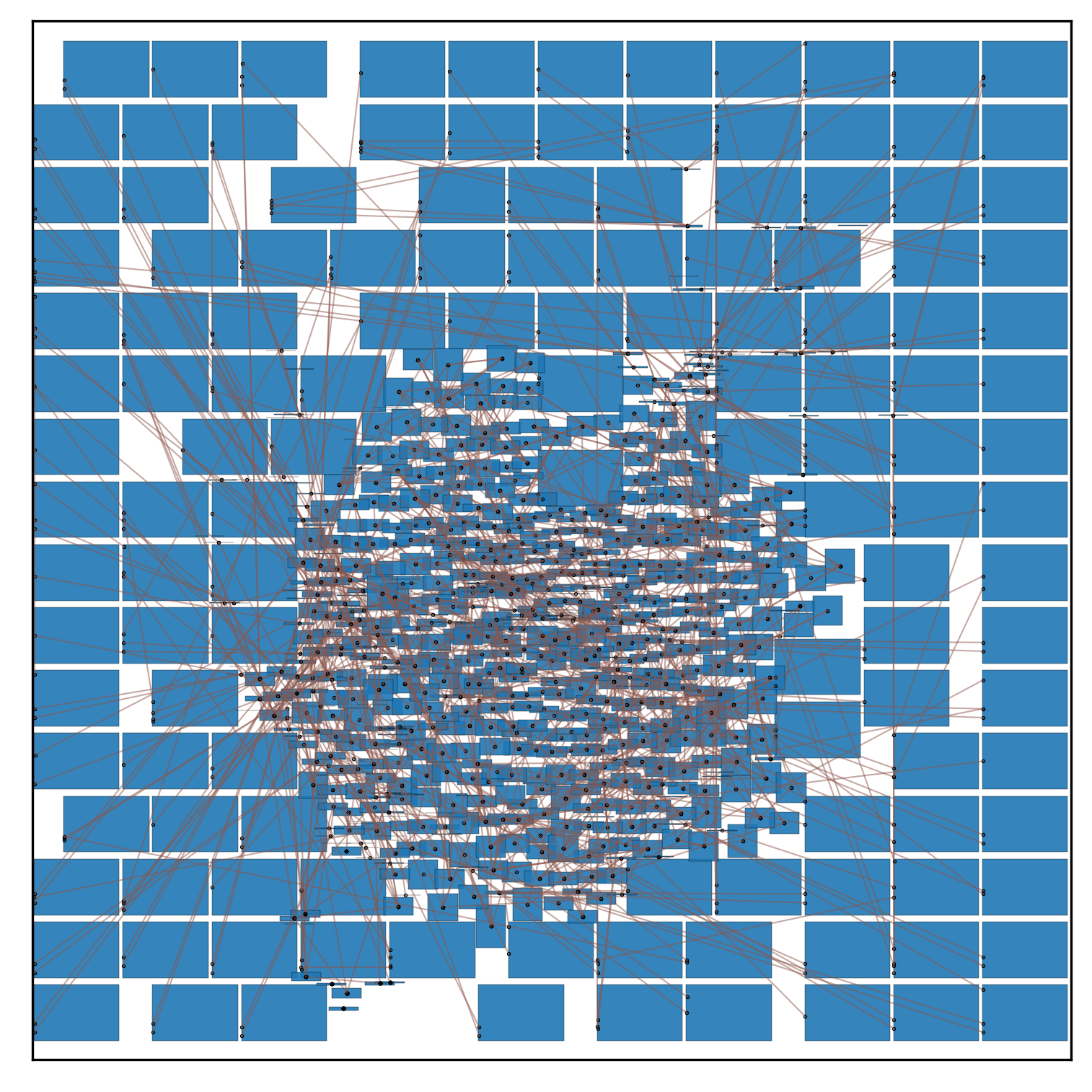

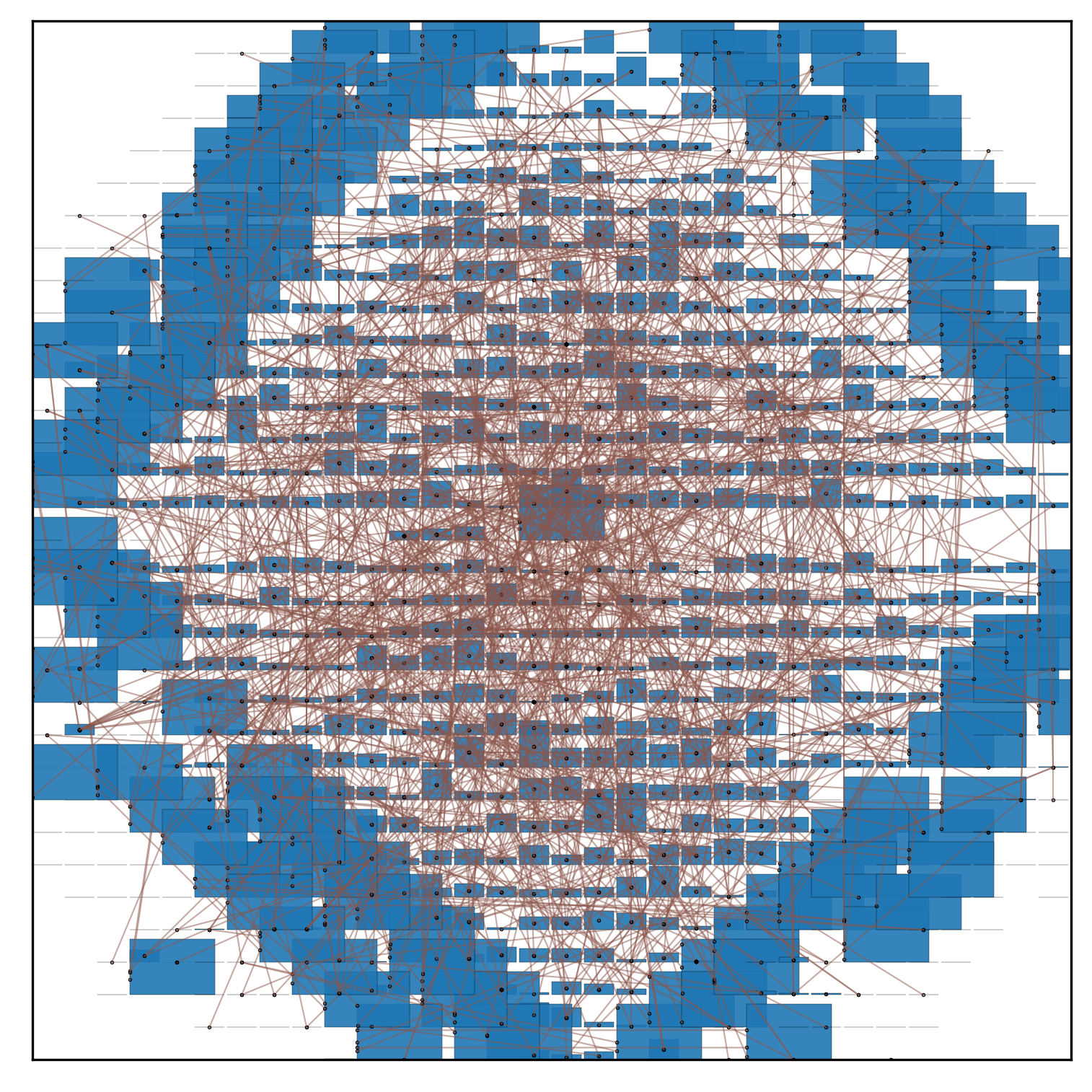

Benchmark: Bigblue3

| Placement | Pos Mask t | Wire Mask t |

|---|---|---|

|

|

|

| View Mask | Pos Mask t+1 | Wire Mask t+1 |

|

|

|

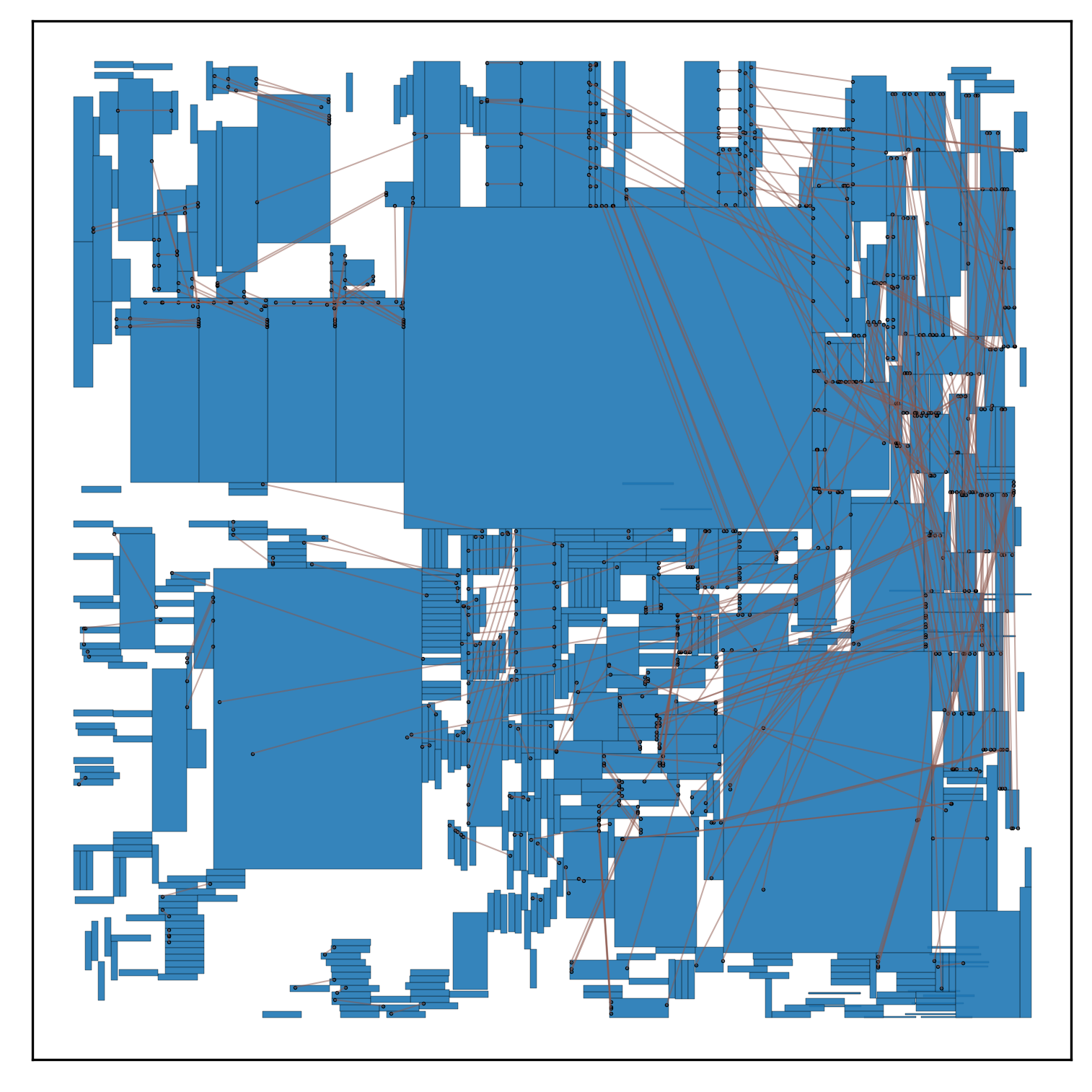

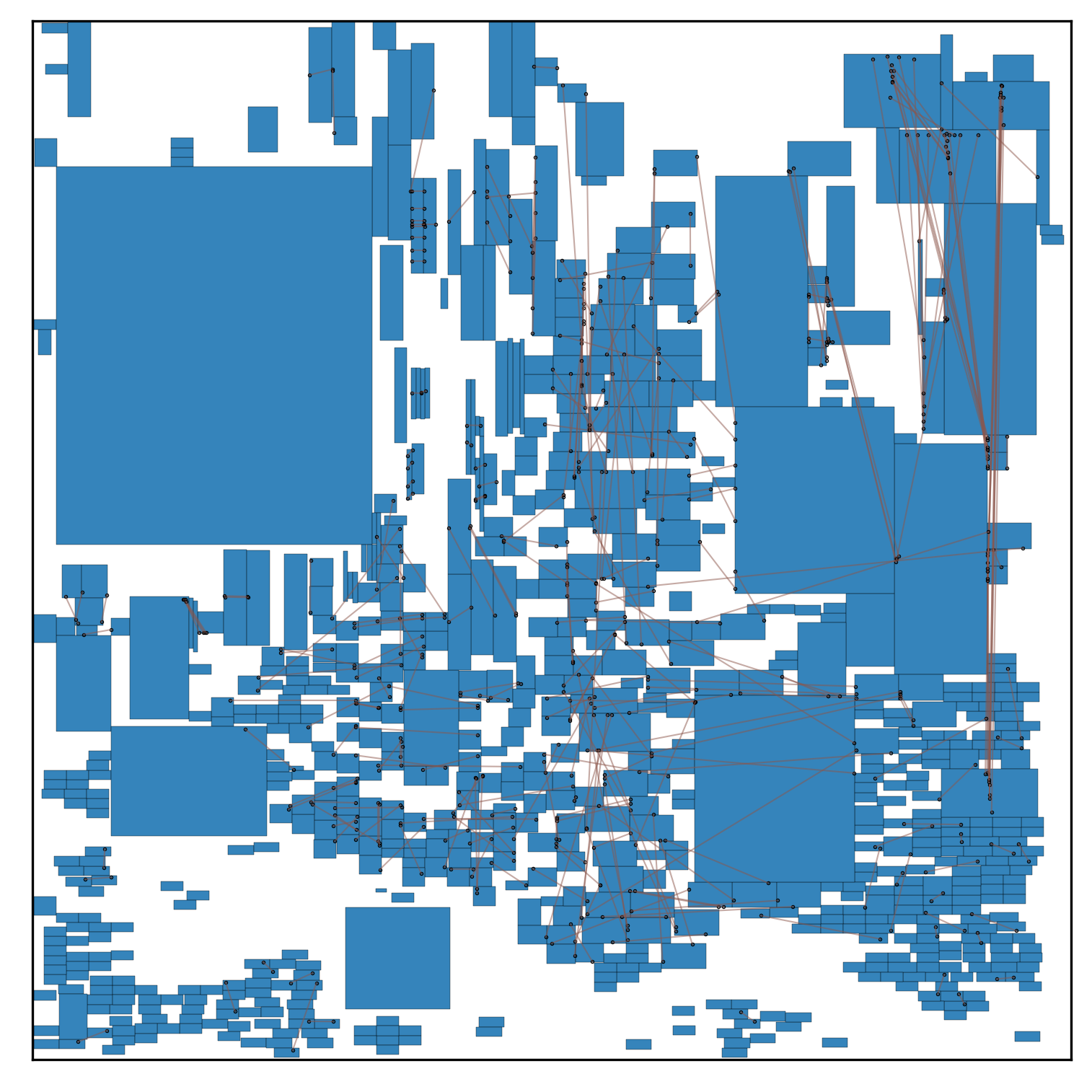

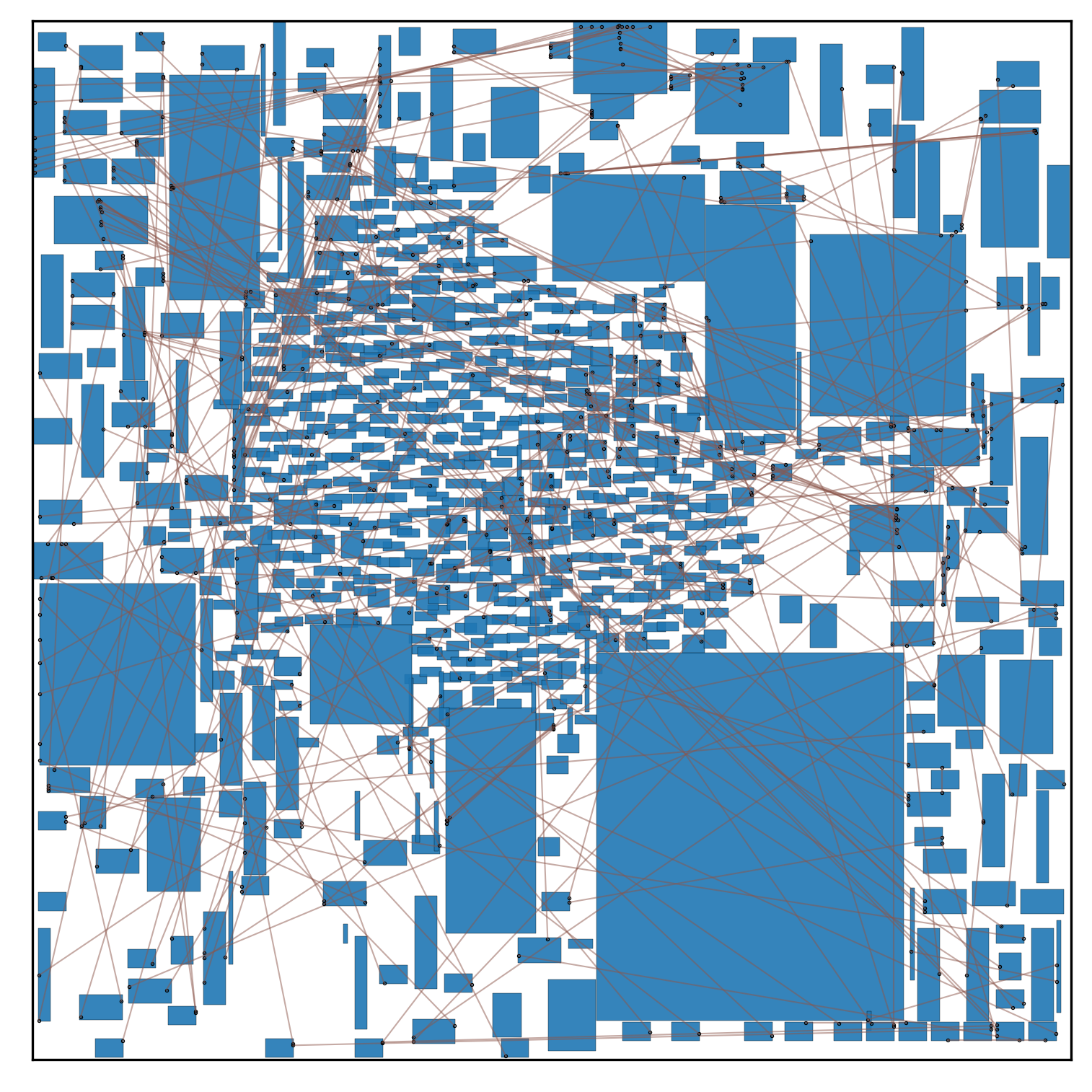

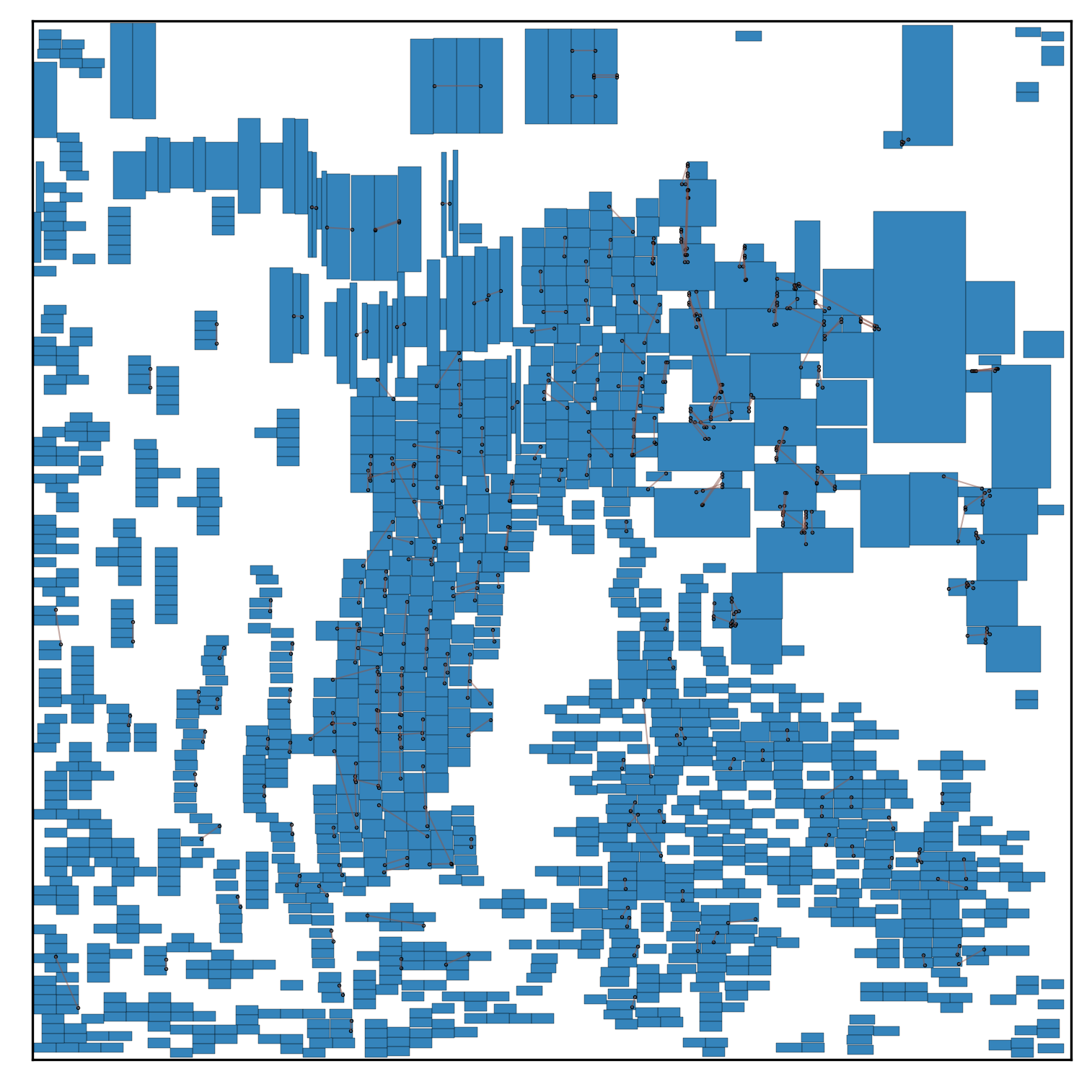

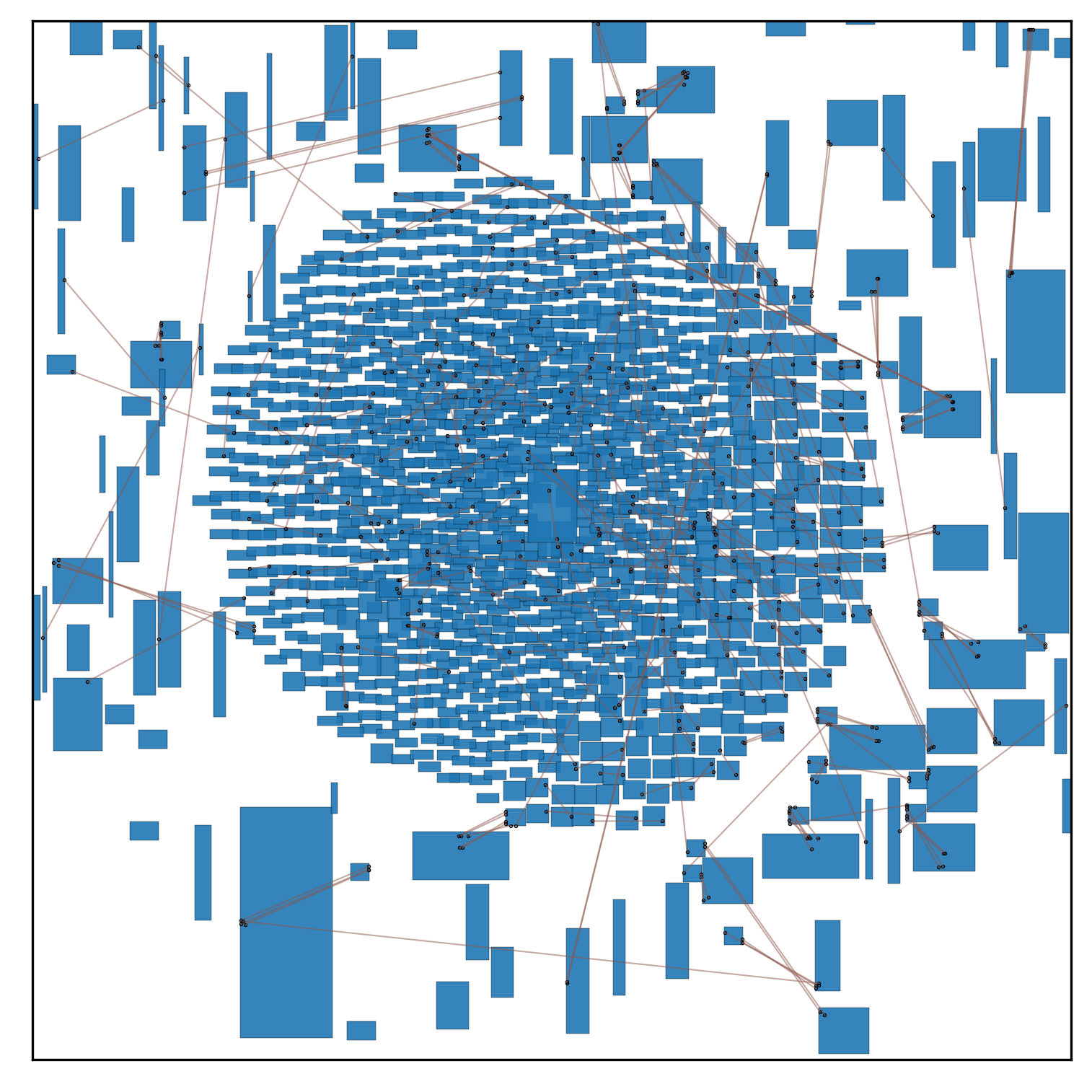

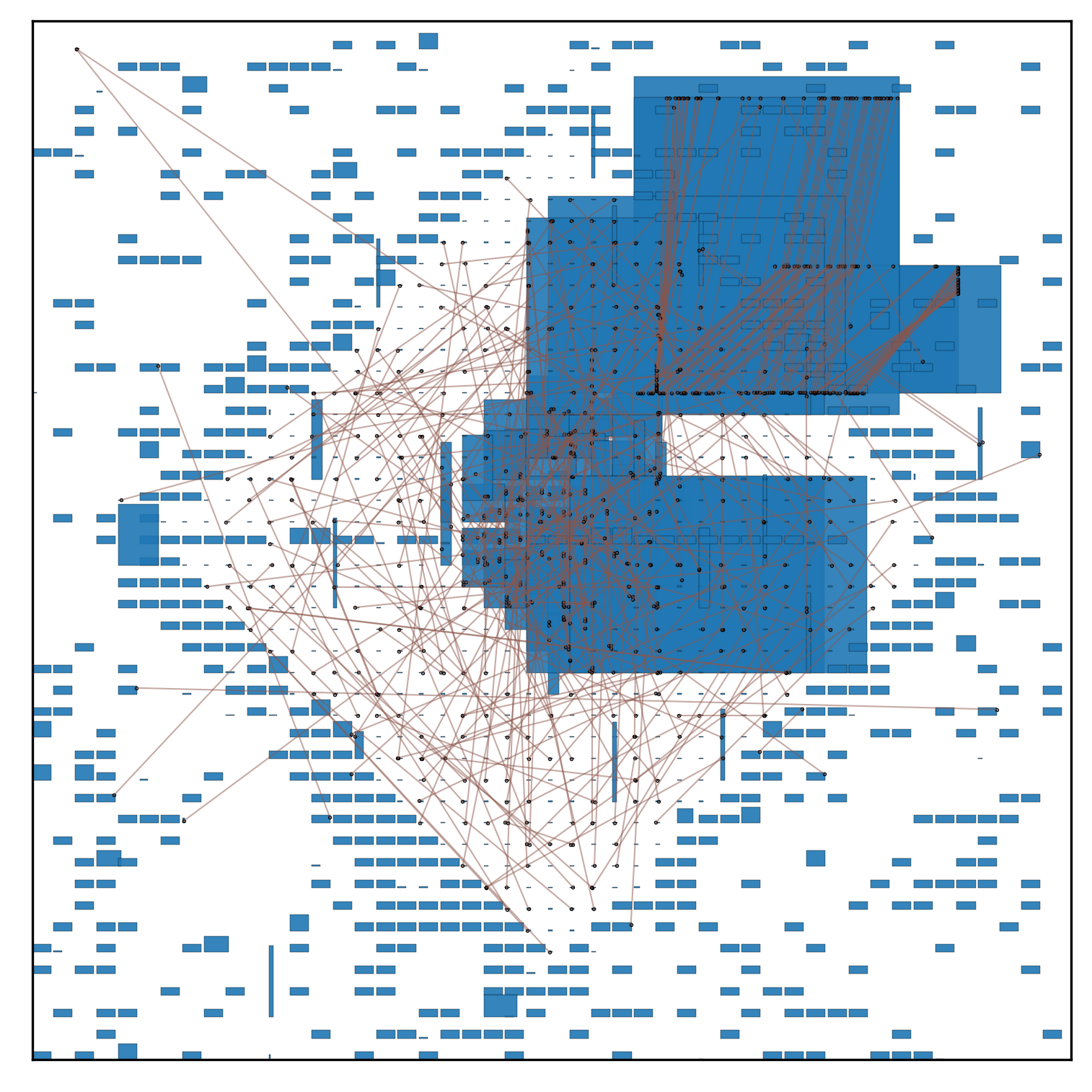

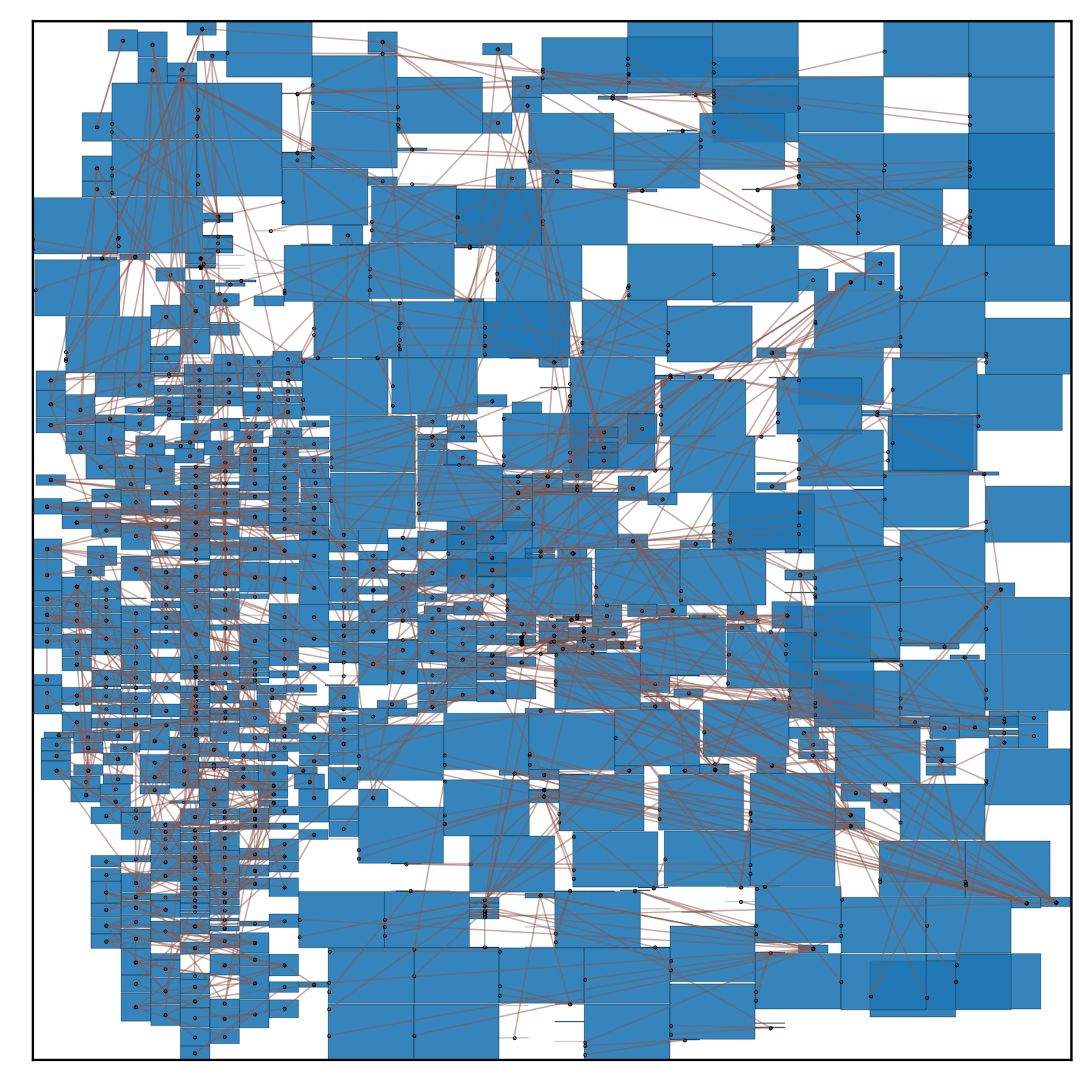

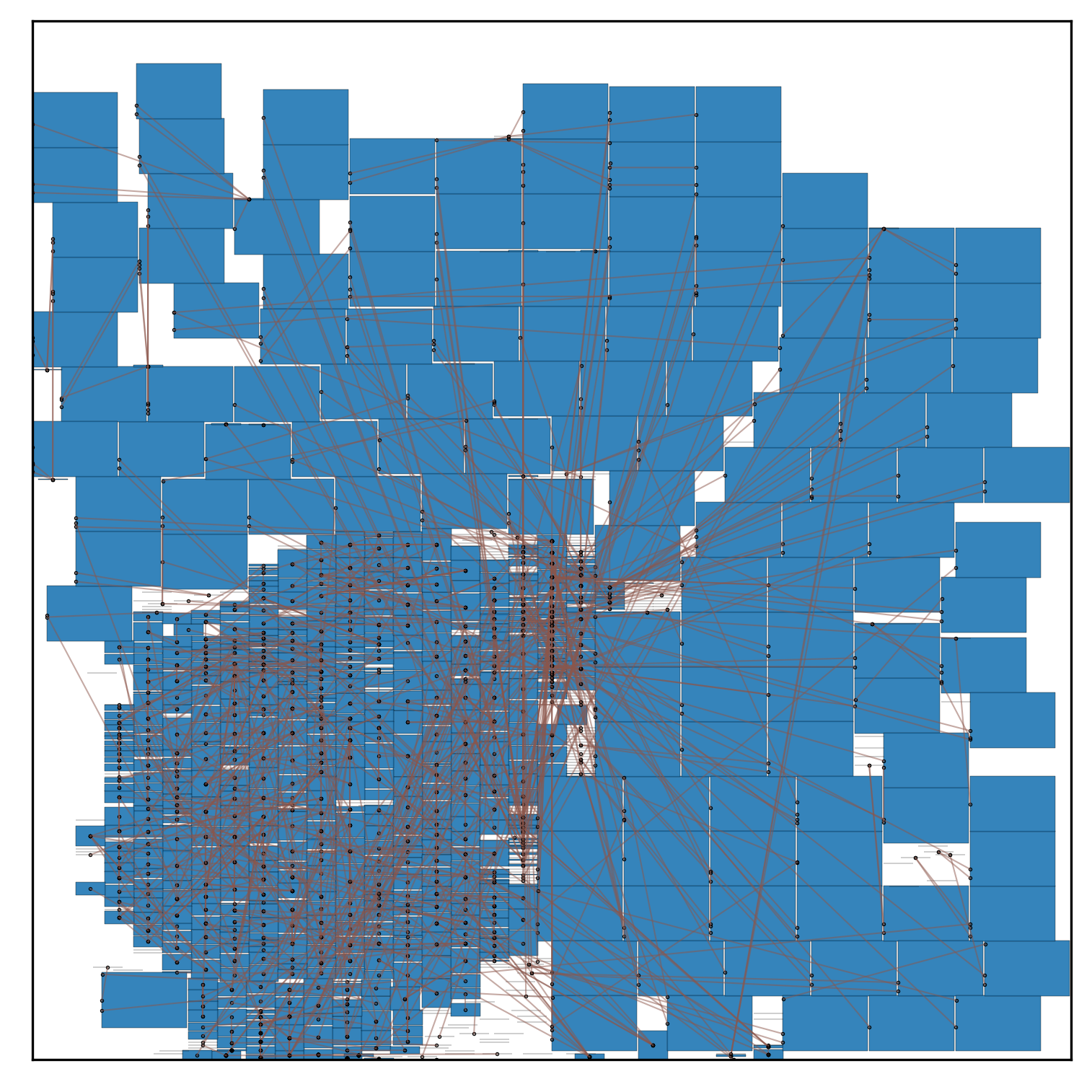

Fix macros and use DREAMPlace (classic optimization-based method) to place standard cells.

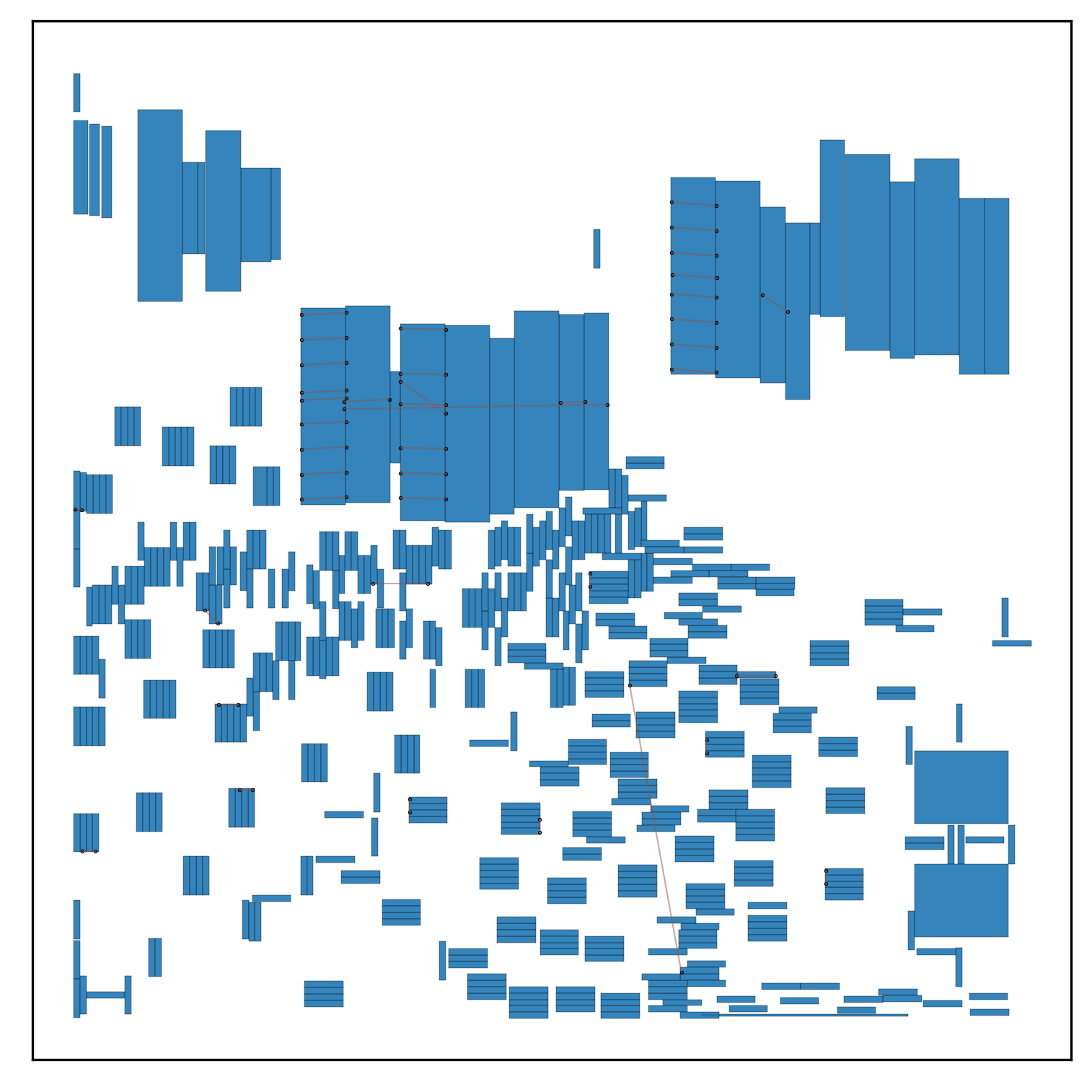

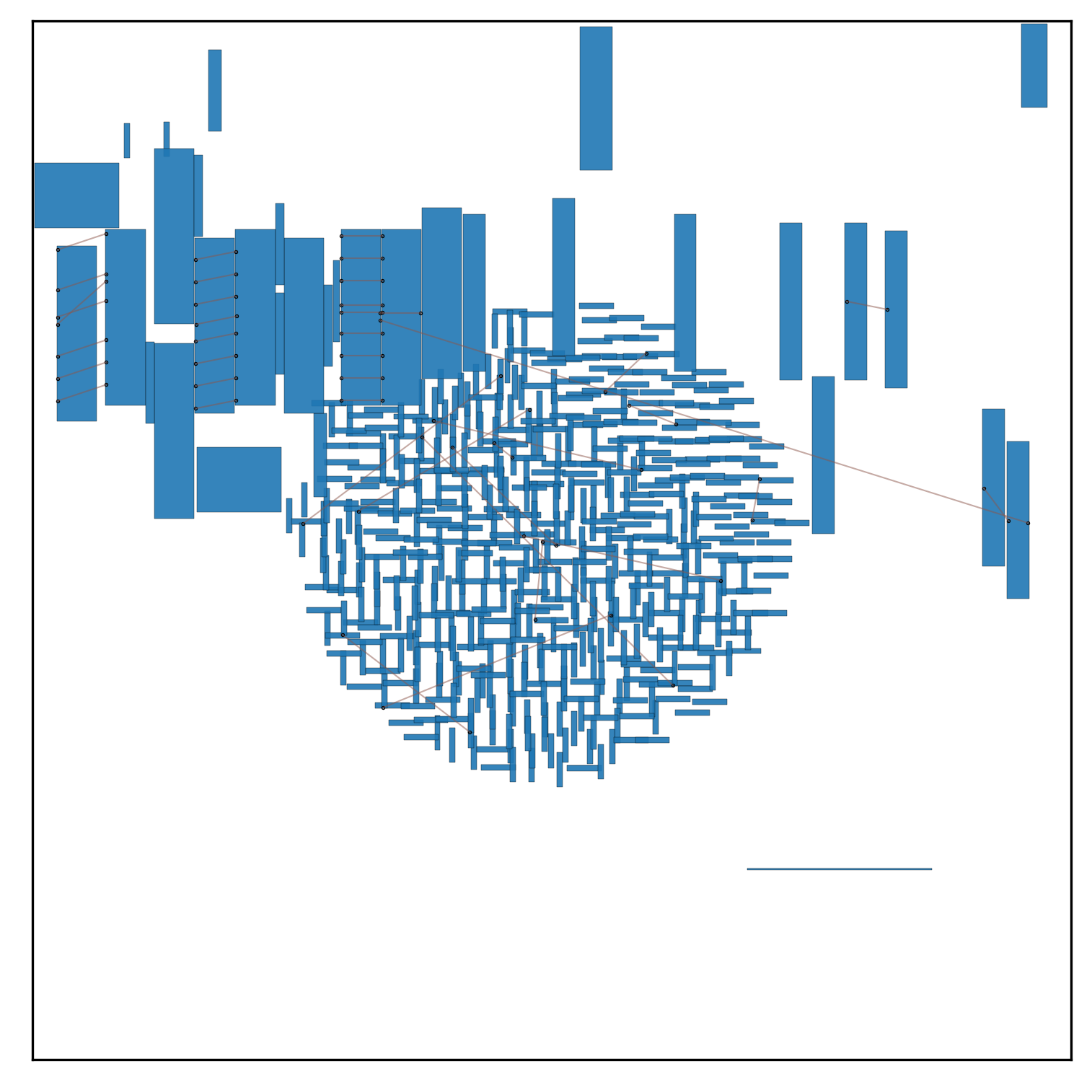

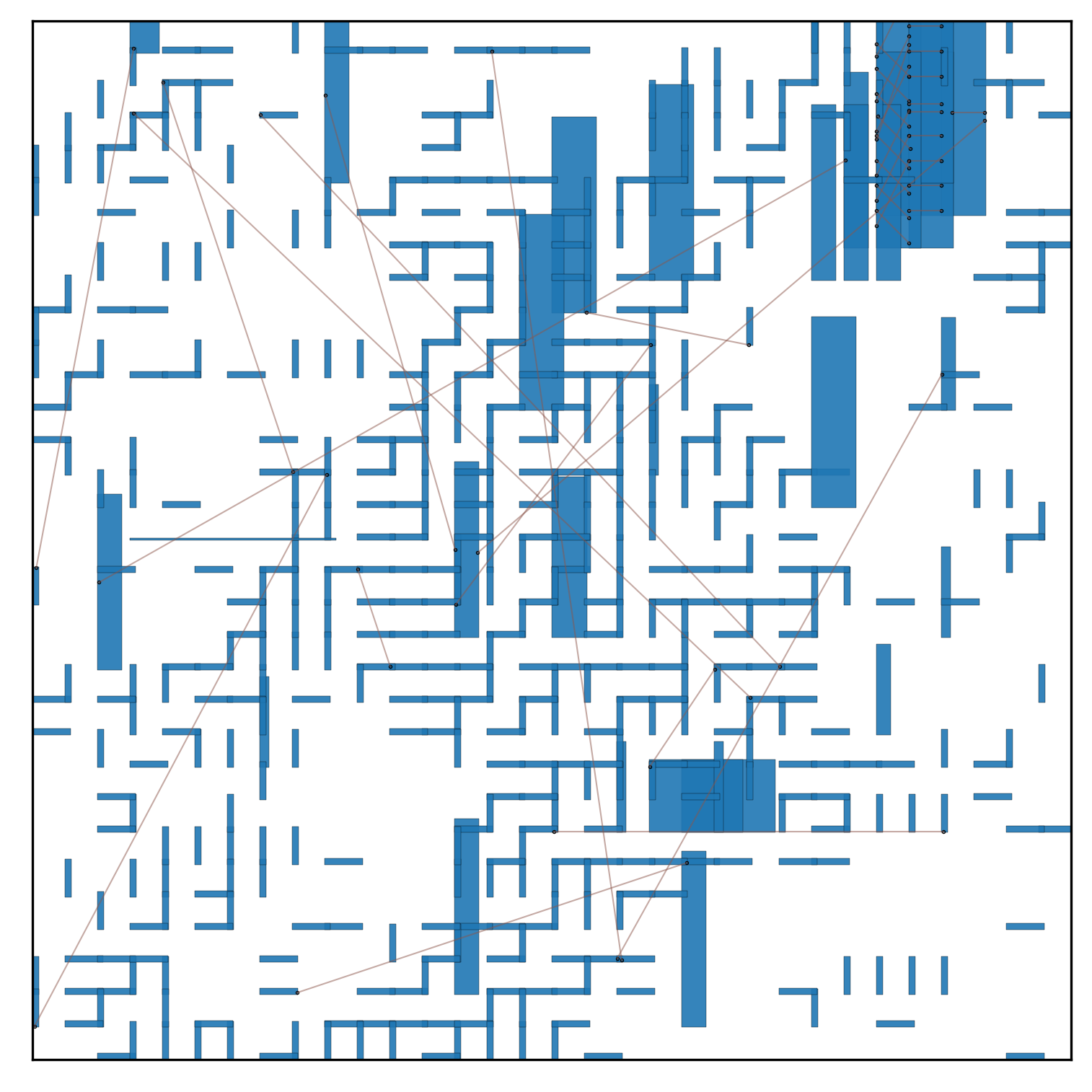

| adaptec2 | adaptec4 | bigblue3 |

|---|---|---|

|

|

|