Learn programing FPGA with VHDL, builds basic modules and components. FPGA based UART Tx Rx

- Reading a switch input and driving an LED output

- Simple State Machine which reacts to user input and drives a number of LEDs

- Synchronising and de-bouncing a Switch Input.

- Generating a PWM output.

- Designing a Shift Register.

- 4 Digit 7-Segment display for counting the number of push button activations

- UART module & State machine for echoing back characters received from a PC over RS232

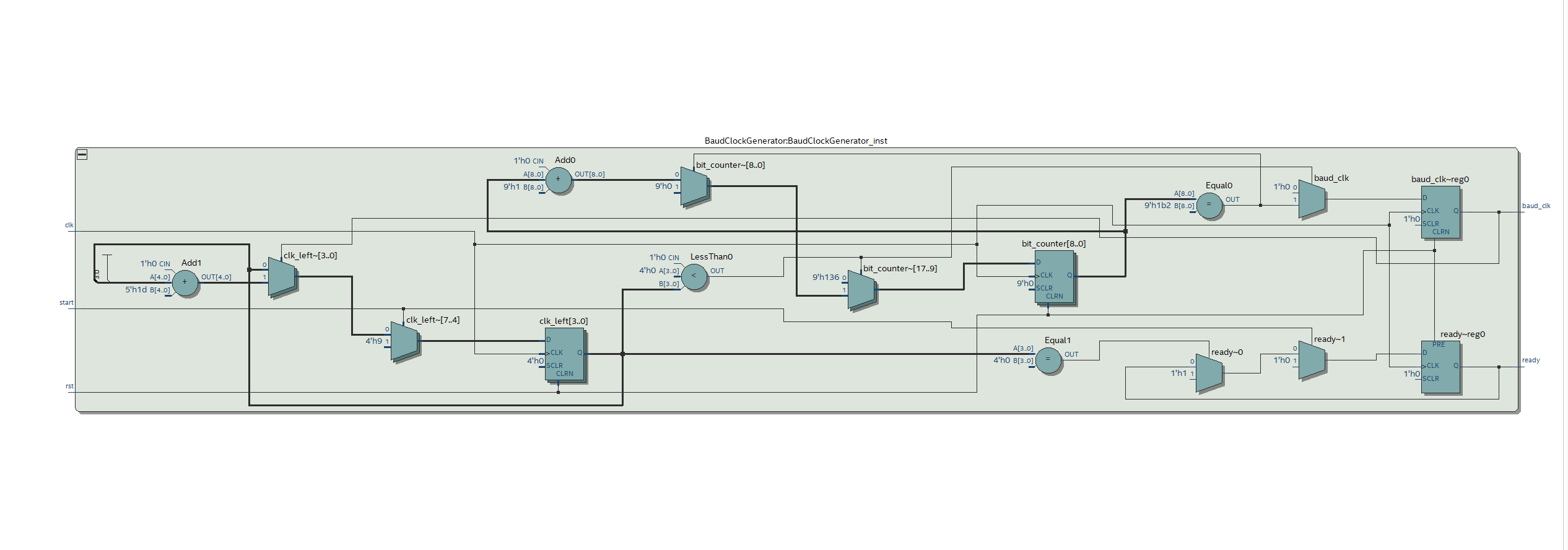

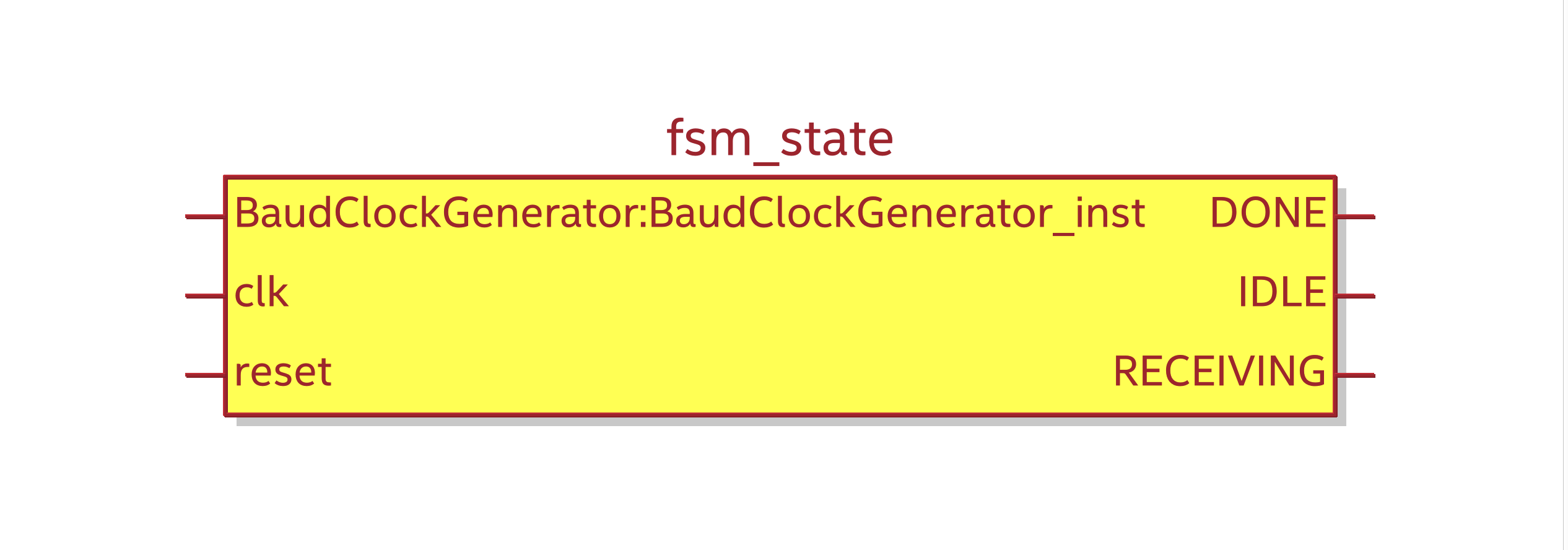

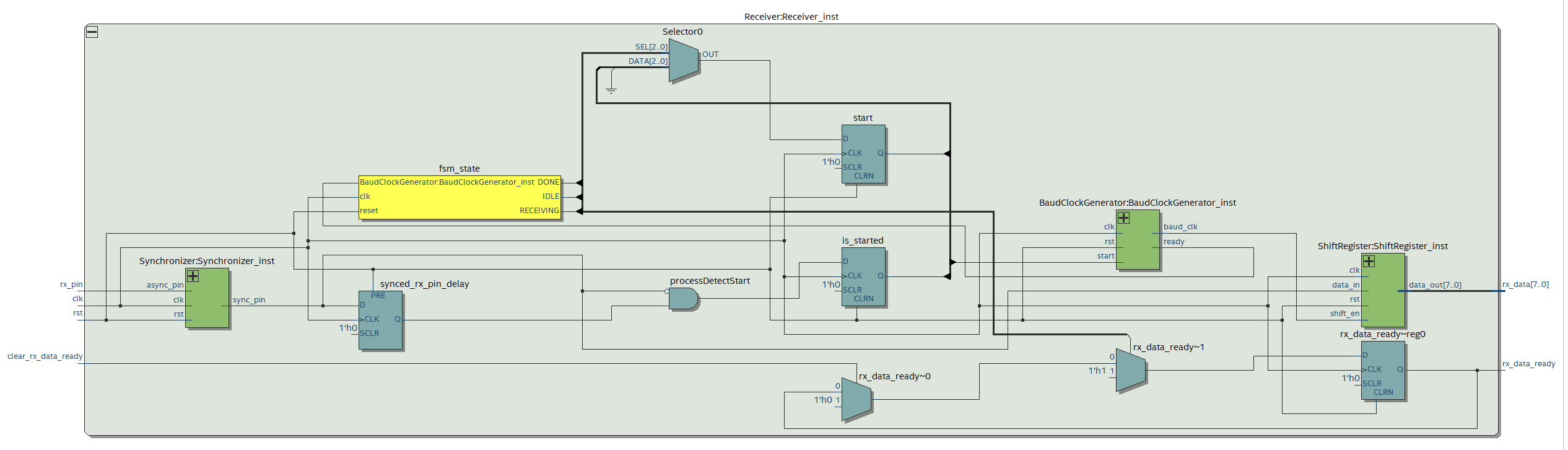

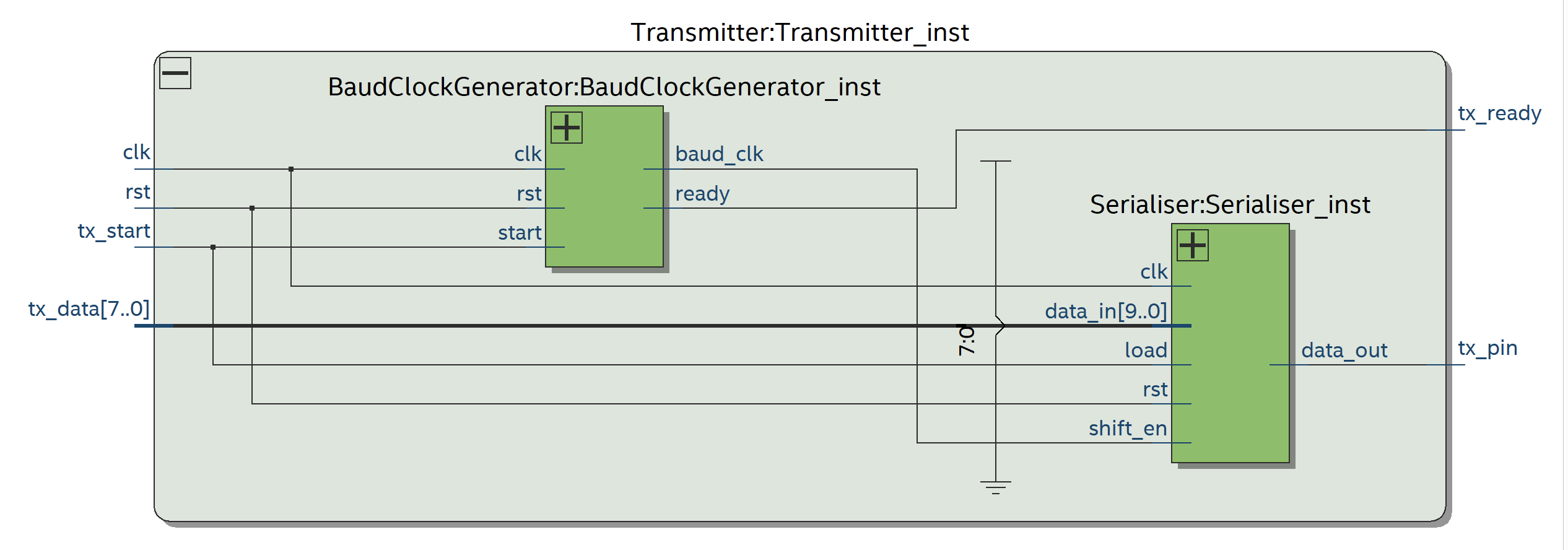

The Baud Clock Generator generates the clock signal required for timing the serial communication. It ensures that data is sampled at the correct rate.

It calculates the baud rate based on the system clock frequency and the desired baud rate.

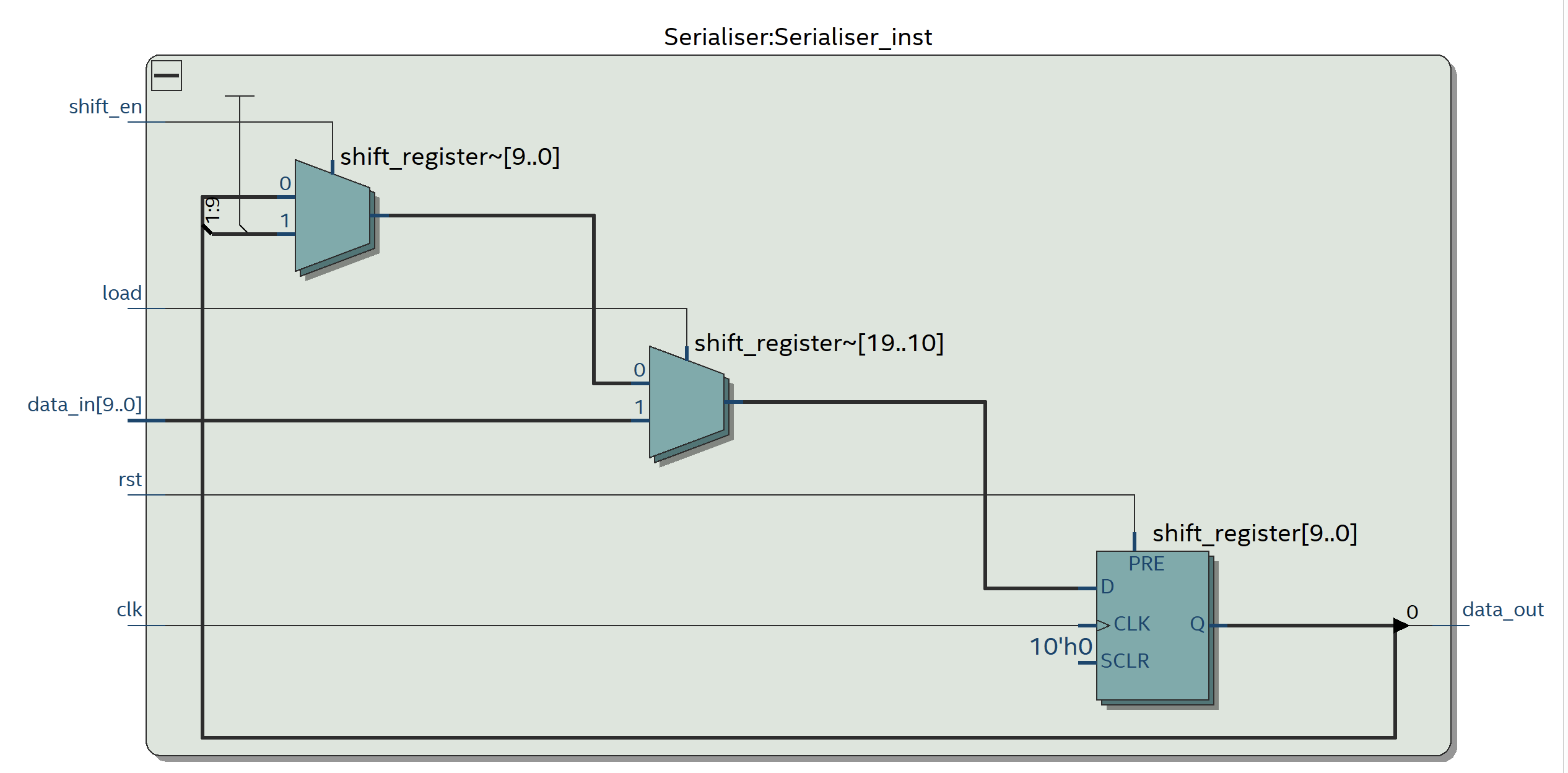

The Serialiser takes parallel data input and converts it into a serial data stream. It serializes the data for transmission over a single data line.

It typically includes a shift register to shift out each bit of the parallel data sequentially.

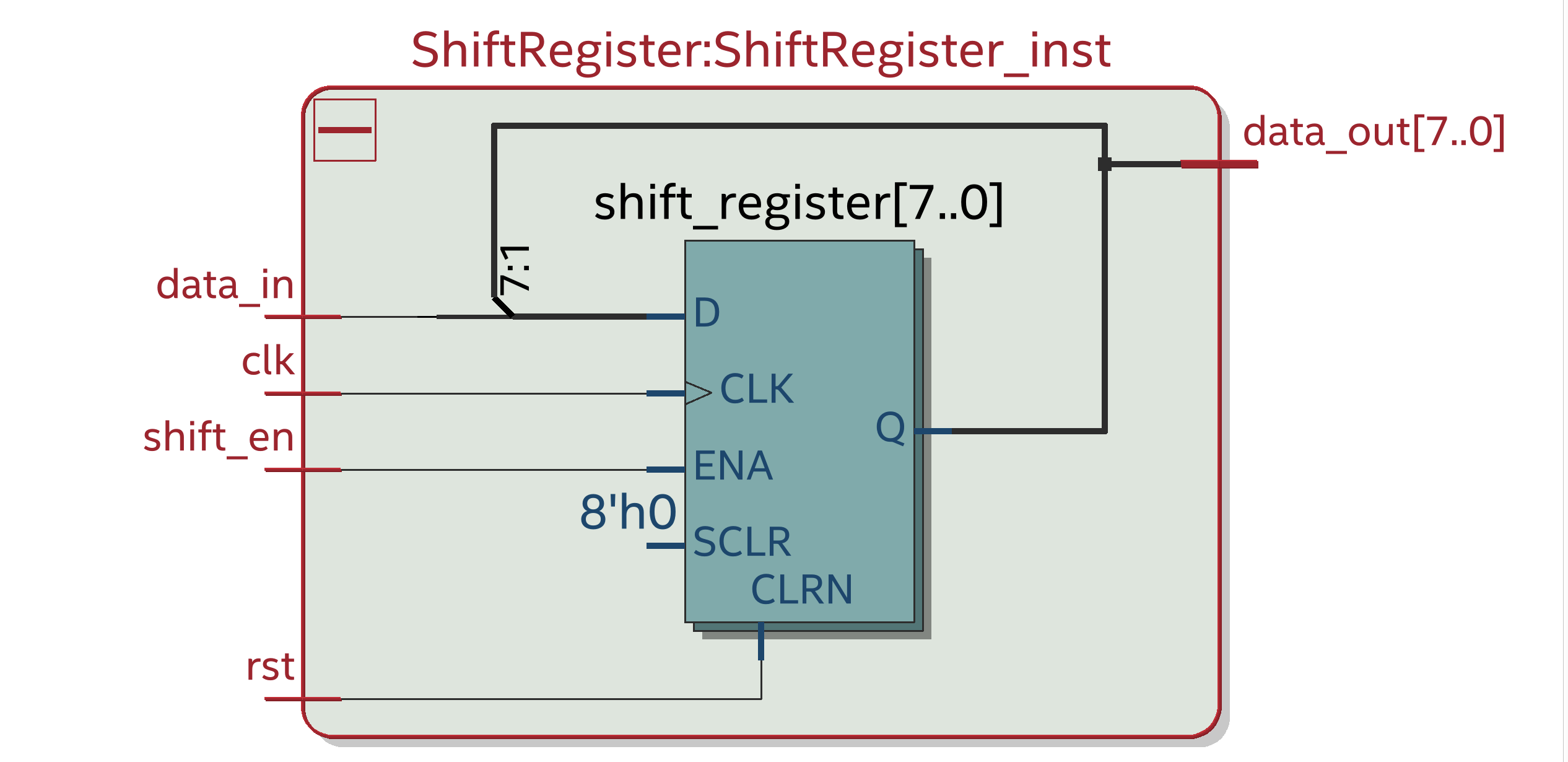

The Shift Register is used to hold the data temporarily during transmission or reception.

For transmission, it shifts data out serially.

For reception, it receives data serially and shifts it into the register.

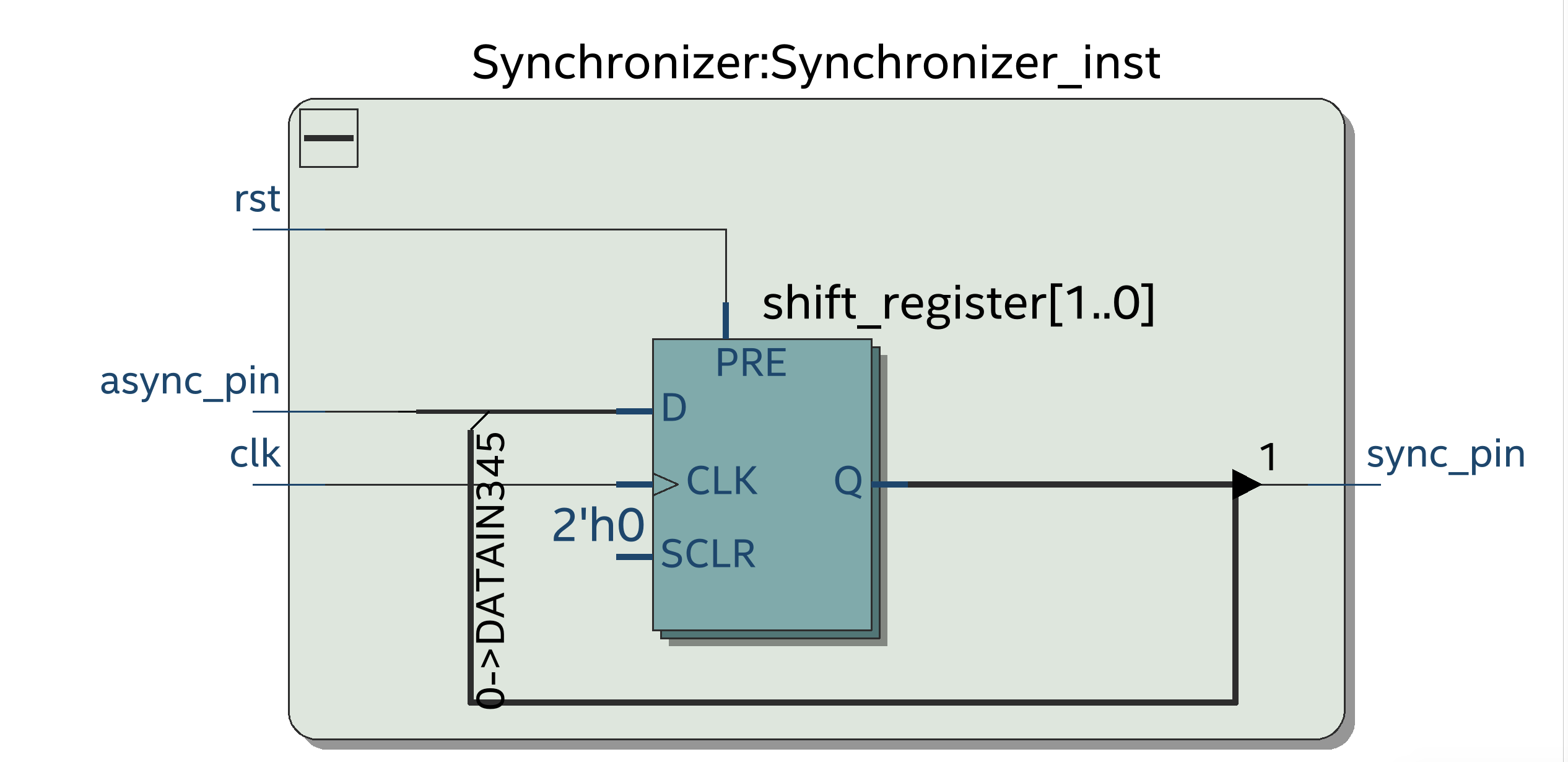

The Synchronizer ensures proper synchronization of the received data with the system clock.

It synchronizes the incoming serial data with the system clock to correctly sample the received bits.

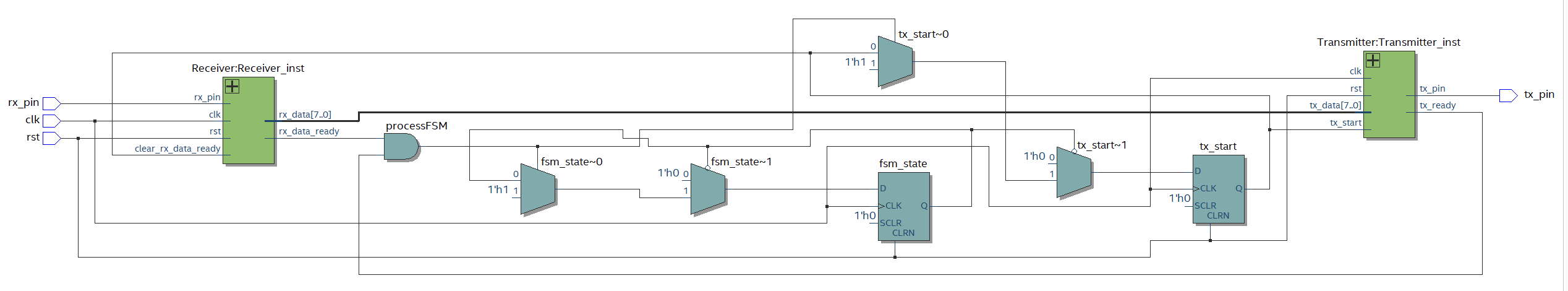

The Receiver's FSM controls the behavior of the receiver. It manages the various states of the receiver during reception.

The Receiver module is responsible for receiving serial data from an external source.

It typically includes logic for detecting the start bit, receiving the data bits, performing optional parity checks, and detecting the stop bit.

The Transmitter module is responsible for transmitting serial data to an external device.

It typically includes logic for sending data bits serially, optionally generating and sending parity bits, and adding stop bits at the end of each data frame.

The TopModule is the overarching module that combines and connects the various UART modules together to create a complete UART communication system.

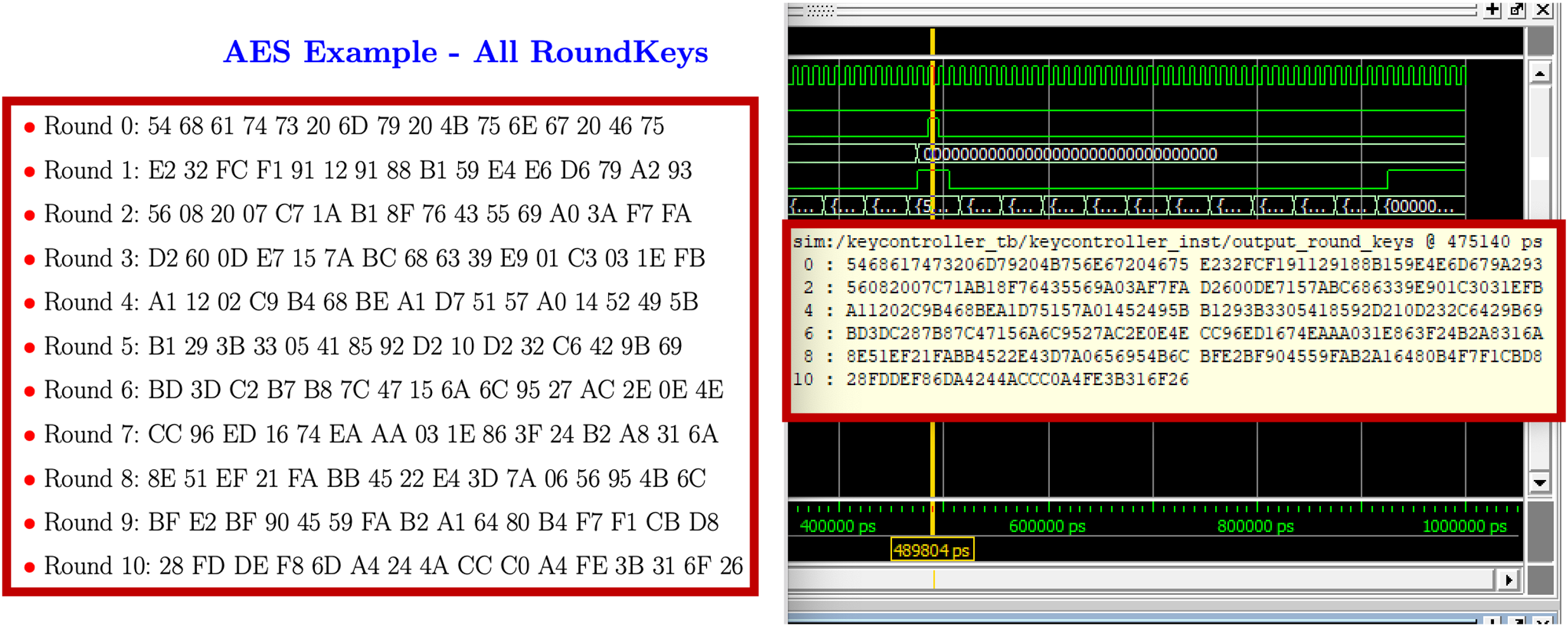

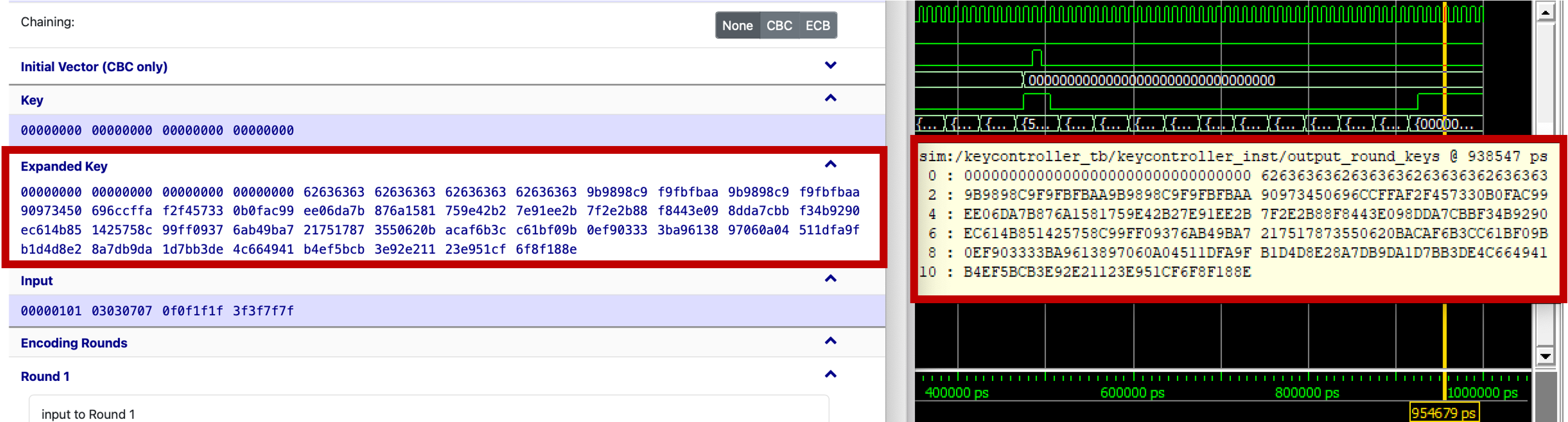

This module generates all the round keys required and stores them as a LUT for each AES encryption, decryption round.