Single Cycle CPU: Our Project of CS202 2023 Spring: Computer Organization, SUSTech.

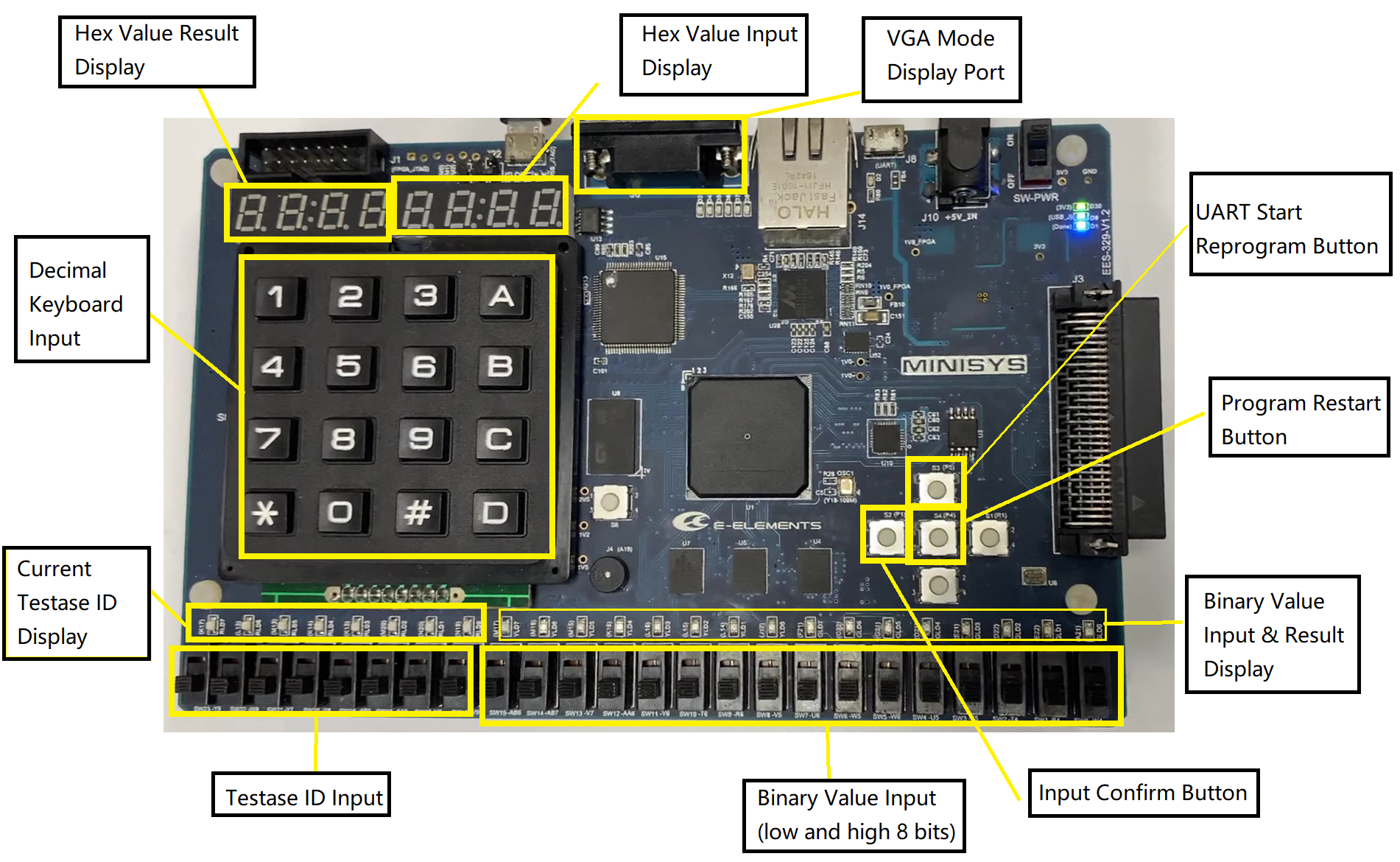

We use FPGA MINISYS 1-A to implement part of the MIPS32 instruction set. Support simple bit operations and binary addition, subtraction, multiplication, and division functions.

Final score: 121/100.

You can check docs folder to see project requirement. And our project report in Chinese.

├─ASM_Minisys-1A

├─CPU_Verilog

├─docs

├─EDA_Xilinx

└─unused

- ASM_Minisys-1A : MIPS assembly file and binary file ,check

Readmein this folder for more information. - CPU_Verilog : Verilog file for this project.

- docs : Project requirement and our report.

- EDA_Xilinx : Some files for Xilinx EDA Vivado, check

Readmein this folder for more information. - unused : Some unused files, including Verilog file for onlinejudge test.

Use Vivado, select the device xc7a100tfgg484-1.

You can load bitstream file directly, or:

- Add the IP core in

EDA_Xilinx/ - The RAM and ROM IP core loads the

.coefile inEDA_Xilinx/respectively - Add the Verilog file in

CPU_Verilog/ - Add the pin constraint file

- Use VIvado to simulate, synthesize, and then generate bitstream files

For example, if you want to do scene 1 test case 001:

- Press Program Restart Button

- Press UART Start Reprogram Button, then use UART to transmit

sc1_new_version.txt - Press Program Restart Button again to start the new program

- Let "Test case ID Input" low 3 bits switch be

001(1means on), then press Input confirm button - Let Binary Value Input low 8 bits be the number 1 you want to input, then press Input confirm button, the Binary Value Input display will show the number 1 in high 8 bits.

- Let Binary Value Input low 8 bits be the number 2 you want to input, then press Input confirm button, the Binary Value Input display will show the number 2 in low 8 bits.

- Press Input confirm button, then the led or keyboard will show the result.