What is SRAM?

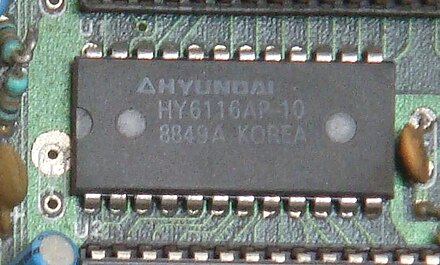

- Static Random Access Memory(SRAM) is a type of random-access memory that uses latching circuitry(flip flop) to store each bit.

- SRAM is volatile memory, data is lost when power is removed.

- Does not require periodic refresh

- OpenRAM is an open-source static random access memory (SRAM) compiler.

- Uses Python framework to create layout, netlists, timing and power models, placement and routing models, and other views necessary to use SRAMs in ASIC design.

Dependencies The OpenRAM compiler has very few dependencies:

- Ngspice 26(or later) or Hspice or CustomSim 2017(or later)

- Python 3.5 or higher

- Python numpy (

pip3 install numpyto install) - Python scipy (

pip3 install scipyto install)

- Python numpy (

If you want to perform DRC and LVS, you will need either:

Supported Technologies

- NCSU FreePDK 45nm

- MOSIS 0.35um (SCN4M_SUBM)

- NCUS FreePDJ 15nm & ASAP 7nm

For more information take a look at the detailed presentaion that serves as documentation. This is the most up-to-date information.

OpenRAM Environment Setup

Downloading the OpenRAM packages from github:

git clone https://github.com/VLSIDA/OpenRAM.git

Adding OPENRAAM_HOME to PYTHONPATH:

export PYTHONPATH="$PYTHONPATH:$OPENRAM_HOME"

It includes the tech files necessory for SCMOS SCN4M_SUBM. The SCMOS spice models, however, are generic and should be replaced with foundry models. If you are using FreePDK45, you should also have that set up and have the environment variable point to the PDK. For example add this to your .bashrc:

export FREEPDK45="/bsoe/software/design-kits/FreePDK45"

You may get the entire FreePDK45 PDK here. If you are using SCMOS, you should install Magic and Netgen. We have included the most recent SCN4M_SUBM design rules from Qflow.